低電壓、恒定增益、Rail-to-RailCMOS運算放大器設計

本文設計了一種低電壓、恒定增益、Rail-to-Rail的CMOS運算放大器,整個電路采用標準的0.6um CMOS工藝參數進行設計,并經過HSPICE工具仿真,在3V的單電源工作電壓情況下,靜態功耗約為9.1mW,當電路同時驅動20pF電容和500Ω電阻的負載時,電路的直流增益達到62dB,單位增益帶寬達到18MHz,相位裕度為50o。

??? 關鍵詞:模擬集成電路;CMOS;運算放大器

引言

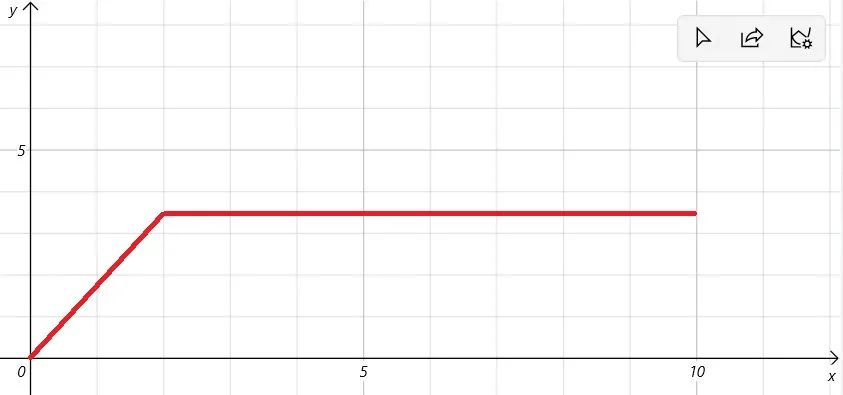

??? 隨著信息技術和微電子制作工藝技術的高速發展,器件的特征尺寸越來越小,由此構成的集成電路的電源電壓也越來越低。1997年,半導體工業協會曾對未來十年CMOS電路的電源電壓發展趨勢作了預測,如圖1所示。預計未來十年集成電路的電源電壓將降至1.5V,甚至更低。

??? 形成這種發展趨勢的原因很多。其中主要有以下三方面原因:1、隨著集成制作工藝的發展,器件的特征尺寸將逐漸減小,相同工作電壓下小尺寸器件所承受的電場將逐漸增高,器件工作的安全性要求迫使工作電壓必須相應降低,而電路集成規模或集成密度逐步增大的事實,導致大功耗、大發熱量的芯片出現,同樣要求采用降低電源電壓來降低功耗。2、便攜式電子裝置的迅速發展及其呈現出的廣闊市場,可植入人體的微功耗醫療電子部件的廣泛應用等市場需求是對低電壓電路的有力牽引。3、全球興起的綠色環保——低能耗要求亦是發展低電壓電路的重要動力。

??? 雖然數字化處理技術已經廣泛應用于電子設備中,然而電子設備的原始信號均來自現實世界,如電磁記錄、揚聲器、麥克風、CCD、LCD、無線調制器和解調器等,它們所產生的信號都為模擬信號,這些信號實現數字處理前必然要先經過模擬信號處理(比如放大、A/D轉換等),同時數字化處理后的信號作用于現實世界時仍需還原為模擬信號(比如D/A轉換、功率放大等)。因而即使在數字技術十分成熟的今天,模擬信號處理技術仍是無法回避,不能忽視的。而從集成技術的角度來看,單片數字系統集成制作的困難已成為過去,集成能力的進一步提高,提出了完整的電子系統集成,即包含數、模混合信號處理的片上系統(SoC)的要求。CMOS已是當今高密度集成的主流工藝,因此,低電壓CMOS模擬電路的設計研究已成為完整意義上的SoC的關鍵技術。

??? 運算放大器是模擬集成電路中的一個重要模塊,隨著電源電壓的降低,傳統的運算放大器結構已經不能滿足設計指標的要求,近十年來,各種新結構的低電壓運算放大器已經大量涌現出來。

??? 本文設計了一種低電壓、恒定增益、Rail-to-Rail的CMOS運算放大器結構,這種結構具有以下特點:1)具有Rail-to-Rail的輸入和輸出;2)在整個共模輸入范圍內具有恒定的增益; 3)具有驅動低阻抗的能力; 4)具有較大的增益帶寬乘積等等。

運算放大器的輸入級

??? 低電壓Rail-to-Rail運算放大器的設計難點集中在輸入級部分,因為輸出級可以采用簡單的AB類輸出級來完成。

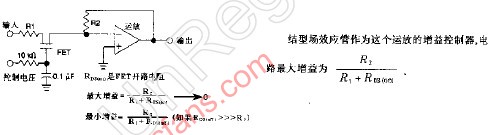

??? 為了得到Rail-to-Rail的共模輸入電壓范圍,可以采用互補輸入級的結構,如圖2所示。NMOS輸入對在高的共模輸入電壓范圍內導通,即

??? Vin,cm>Vss+Vgs,n+Vds,n???? (1)

??? 而PMOS輸入對在低的共模輸入電壓范圍內導通,即

??? Vin,cm>Vdd-Vgs,p-Vds,p (2)

??? 從(1)(2)式中可以明顯的看出,當共模輸入電壓范圍處于中間值時,NMOS和PMOS輸入對將同時導通,這也就意味著這個區間的輸入級電流將增大一倍,根據下式:

??? 其中K=μpCox(W/L)p=μnCox(W/L)n

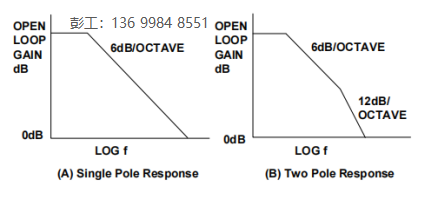

??? 所以互補輸入級的跨導也將增大一倍,進而導致運算放大器的增益在整個共模輸入電壓范圍內不是恒定的,如圖3曲線1所示。

??? 本文設計了一種具有恒定跨導的互補輸入級結構,該結構思路簡單并且有效地解決了上述互補輸入級跨導變化的問題,如圖4所示。

??? 從上面的分析得知,為了使圖2所示的輸入級結構在整個共模電壓范圍內保持跨導一致,那么對應于高和低的共模輸入電壓范圍內的跨導就必須增大一倍,又根據式(3),電流IDSQ與Gm呈平方根的關系,所以相應的尾電流就必須再增加三倍,圖4結構正是基于這個原理之上的。

??? M1、M2和M3、M4分別組成PMOS、NMOS輸入對,Iref1=Iref2=Iref提供相同的尾電流,M7、M8和M9、 M10分別組成兩個1:3的電流鏡,M11、M12是兩個電流開關管,偏置電壓Vb1=Vb2=1.3V。因此,在共模輸入電壓從Vss到Vss+1.2V時,PMOS對M1、M2導通(M3、M4截止),同時M12導通(M11截止),Iref2通過M12到達1:3的電流鏡M7、M8,M8的電流加上Iref1的尾電流,正好使電流增大到四倍,也即跨導增大到兩倍;在共模輸入電壓從Vdd-1.2V到Vdd時,M3、M4導通(M1、M2截止),Iref1通過M11到達1:3的電流鏡M9、M10,M10的電流加上Iref2的尾電流,也正好使電流增大到四倍,即跨導也增大到兩倍;在共模輸入電壓從Vss+1.4V到Vdd-1.4V時,PMOS對和NMOS對同時導通,而電流開關管M11、M12截止,每個輸入對的電流都等于Iref。

M10分別組成兩個1:3的電流鏡,M11、M12是兩個電流開關管,偏置電壓Vb1=Vb2=1.3V。因此,在共模輸入電壓從Vss到Vss+1.2V時,PMOS對M1、M2導通(M3、M4截止),同時M12導通(M11截止),Iref2通過M12到達1:3的電流鏡M7、M8,M8的電流加上Iref1的尾電流,正好使電流增大到四倍,也即跨導增大到兩倍;在共模輸入電壓從Vdd-1.2V到Vdd時,M3、M4導通(M1、M2截止),Iref1通過M11到達1:3的電流鏡M9、M10,M10的電流加上Iref2的尾電流,也正好使電流增大到四倍,即跨導也增大到兩倍;在共模輸入電壓從Vss+1.4V到Vdd-1.4V時,PMOS對和NMOS對同時導通,而電流開關管M11、M12截止,每個輸入對的電流都等于Iref。

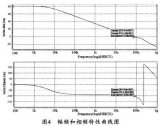

??? 圖3曲線2所示為上述互補輸入級結構中共模電壓與跨導的關系,從圖中可以看出跨導在整個共模輸入電壓范圍內基本保持不變,只是在兩個過渡區有大約15%的浮動,這是由于NMOS管和PMOS管不完全匹配造成的。

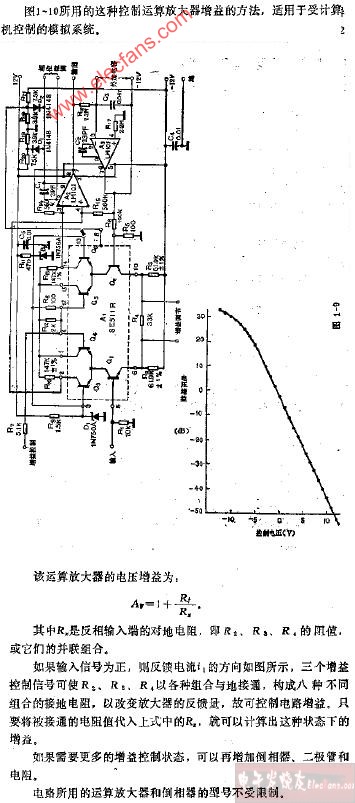

運算放大器電路整體結構與仿真結果

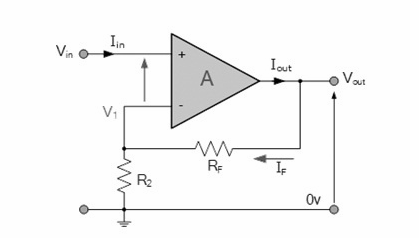

??? 運算放大器電路整體結構如圖5所示,它由上面討論過的輸入級、中間的求和電路以及輸出驅動器組成,其中輸出驅動器由一個交叉級和一個輸出級組成。 整個電路采用標準的0.6um CMOS工藝參數進行設計,并經過HSPICE工具仿真,得到如圖6、圖7所示的頻率響應曲線。

??? 整個電路在3V的單電源下工作,靜態功耗約為9.1mW,。當電路同時驅動20pF電容和500Ω電阻的負載時,電路的直流增益達到62dB,單位增益帶寬達到18MHz,相位裕度為50o。?

結語

??? 本文設計了一種低電壓、恒定增益、Rail-to-Rail的CMOS運算放大器,輸入級采用互補差分輸入級結構,通過電流開關控制原理使放大器在整個共模輸入電壓范圍內保持恒定的增益,輸出級采用帶有彌勒補償的互補共源輸出結構,得到Rail-to-Rail的對稱輸出擺幅。電路基于0.6um標準的CMOS工藝參數進行設計,并經過HSPICE工具仿真,得到了很好的性能。

電子發燒友App

電子發燒友App

評論