在這篇文章中,我們將介紹鑒頻鑒相器(PFD)的工作原理。

2023-11-22 14:49:09 1588

1588

波動都將引發輸出端的電壓變化。圖3鑒相器工作原理 目前已根據鑒相器原理開發了多種測量方法。其中,參考信號源/PLL (鎖相環) 和鑒頻器方法應用最廣泛。3. 參考信號源/PLL 測量方法如圖 4所示

2014-06-12 00:37:53

用fpga實現四倍頻鑒相計數的功能。找到一段代碼。求完整的代碼。還有LIBREAY APP;為什么報錯啊?

2012-05-15 18:25:42

Hello! 請教個關于鑒相頻率雜散與環路濾波器布線的問題。例如ADF4360,鑒相頻率的雜散抑制的典型值為-70dBc左右,而實測為-60~-65dBc,也能接受,只是感覺各次倍頻的鑒相頻率太多

2018-11-07 09:03:01

ad9518-4,改芯片用過好多次,這次應用相噪要求較高,鑒相器工作頻率20MHz。發現如下問題:

鑒相器工作頻率20MHz下,環路濾波器帶寬設置為250k、100k、50k都不能鎖定;

環路濾波器

2023-12-06 06:51:29

AD9901為AD公司生產的高速鑒相芯片,但是它有兩種引腳接法TTL及ECL,請問,這兩種接法是指它們的內部框圖是完全一樣的,只是外圍電路不一樣?還是指TTL及ECL接法內部框圖是是不一樣的?因為我

2014-08-06 10:07:23

求教各位大神有用過AD9901這款鑒相芯片嗎,我用來檢測兩列信號的相位差。為什么我輸入兩列1MHZ占空比不同的方波,輸出始終在直流4V左右,而不是我想得到的兩列方波的異或輸出。還有AD9901KQ和AD9901TQ哪個是TTL電平啊,有沒有用過這款芯片的請賜教啊

2014-06-05 21:07:37

求教各位大神有用過AD9901這款鑒相芯片嗎,為什么我輸入兩列1MHZ占空比不同的方波,輸出始終未4V左右,而不是我想得到的兩列方波的異或輸出。我是看到網上文章里有用這款芯片鑒相的,我的電路跟他的一模一樣,卻出不來結果,好郁悶,求各路大神解惑,不勝感激,附電路如下:

2014-06-12 19:16:17

ADF4110僅做鑒相電路使用時,電荷泵經濾波器輸出的直流電壓信號不會隨著相位的改變而改變

2018-09-11 10:05:03

基本上為0。為了驗證ADF4159芯片的問題,我把芯片CP輸出到環路濾波斷開,直接一個電阻進行取樣看看鑒相器有沒有工作。單獨只輸入參考時鐘,芯片RF不輸入信號時候,CP是有輸出。然后再單獨用信號源灌入

2023-12-13 08:09:19

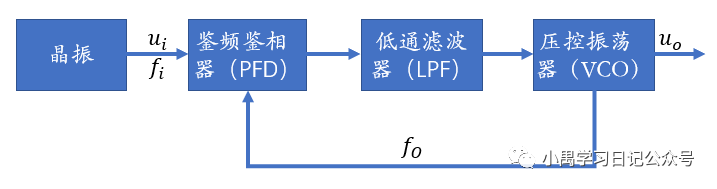

資料下載。希望大家喜歡哦! 本講義涉及以下主題內容五種類型的頻率合成什么是時鐘? 常用頻率是多少?鎖相環(PLL)基本模型鑒頻鑒相器(PFD) 驅動電荷泵(CP)數字PLL框圖 —— 分頻器PLL中輸入

2018-10-26 09:16:36

`EV1HMC3716LP4數字鑒頻鑒相器產品介紹EV1HMC3716LP4詢價熱線EV1HMC3716LP4現貨EV1HMC3716LP4代理王先生***深圳市首質誠科技有限公司

2019-05-19 11:59:10

`HMC3716LP4E數字鑒頻鑒相器產品介紹 產品名稱:數字鑒頻鑒相器 HMC3716LP4E特征 超低SSB相位噪底:-153dBc/Hz(10kHz偏置時,100MHz)集成輸出電阻改善輸入

2019-05-19 11:44:33

請問HMC704鑒相器能不能實現小數模式100M參考,100M鑒相,有用過的大神能不能指導一下?

2021-06-08 09:41:45

,即N為整數,則鑒相頻率PFD=fvco/N,算出鑒相頻率后AD9912再輸出這個頻率送至HMC的參考輸入腳,鑒相頻率范圍為68MHz~72MHz,環路帶寬為手冊上推薦的90KHz,當輸出頻率變化小于

2019-02-22 12:27:30

。2、通過外部環路細調。PLL 切換到外部環路。鑒相器和電荷泵配合外部環路濾波器工作,形成一個閉環,確保 PLL 鎖定到所需頻率。校準大約需要 94,208 個鑒頻鑒相器 (PFD) 周期;對于一個

2018-11-01 10:42:37

EF3 FPGA 內嵌 2 個多功能鎖相環(PLL),可以實現時鐘分頻、倍頻、占空比調整、輸入和反饋時鐘對準、多相位時鐘輸出等功能。PLL 的架構如圖 1 所示,包含鑒頻鑒相器(PFD)、壓控振蕩器(VCO)、低通濾波器(LPF)等基本電路。

2022-10-27 09:07:03

哪位可以提供一下mc1496用于鎖相環鑒相器的電路實例?數據手冊偏偏在這地方沒有給具體的電路。

2011-04-05 14:37:12

multisim中沒有高速鑒相器件AD9901,那么有什么方法可以解決此問題嗎?是否可以用其他的器件代替,望大家不令賜教,謝謝!!

2015-01-30 15:37:37

。該電路的第一個基本元件是鑒頻鑒相器(PFD)。PFD將輸入到REFIN的頻率和相位與反饋到RFIN的頻率和相位進行比較。ADF4002 是一 款可配置為獨立PFD(反饋分頻器N = 1)的PLL

2019-10-02 08:30:00

的經典數字PLL架構。圖1.PLL基本配置該電路的第一個基本元件是鑒頻鑒相器(PFD)。PFD將輸入到REFIN的頻率和相位與反饋到RFIN的頻率和相位進行比較。ADF4002 是一款可配置為獨立PFD

2019-01-28 16:02:54

為什么鑒相器之后要連接環路濾波器?

2014-03-24 14:02:20

二極管用作雙脈沖型鑒相器如圖是電視機使用的雙脈沖平衡型鑒相器的原理電路。同步脈沖分相管基極加有負極性行同步脈沖。在不加行同步脈沖時,由于分相管基極上沒有加正向偏置電壓,因此分相管不導通,在行同步脈沖

2009-08-05 12:41:56

橋式鑒相器電路如圖所示的電路是一種橋式鑒相器。假定在輸入端1上作用著正弦信號。這個信號在頻率和相位上需與加在輸入端11上的脈沖信號相比較,當一個信號的頻率或相位與另一個信號的頻率或相位相差別時,就可

2009-08-05 12:31:52

類型,前者用于同步鑒相器作平衡式鑒頻解調,后者用于差分峰值鑒頻器作差動微分式鑒頻解調。德鍵調頻音頻窄帶型JTCV10.7M系列貼片鑒頻器,搭配多種IC應用于FM程序檢驗,轉換頻率為有用的音頻信號。 調頻

2013-12-17 17:58:19

使用74LS74與74LS00構成鑒相器,仿真結果中,兩路輸出一路輸出為帶有相位差的方波信號和一路為周期脈沖信號,兩路信號頻率相同。但是在實際調試中,會出現兩路信號交替出現的情況,希望得到一些指點。

2020-11-26 16:45:49

基于數字鑒相的自由軸法RLC測量系統的原理是什么基于數字鑒相的自由軸法RLC測量系統由那幾部分組成

2021-05-10 06:27:50

吳鑒鷹總結的Keil編譯常見問題

2015-12-20 13:04:29

正在做一個東西,里面需要用到LABVIEW的鑒相器的仿真但是沒有思路,網上找的看不清楚,誰有文件希望讓我參考一下,謝謝

2020-04-28 09:52:27

小白網上找了很多鑒相芯片都是最多到2π,有沒有0~4π鑒相范圍的芯片?

2015-04-16 22:29:52

小白網上找了很多鑒相芯片都是最多到2π,有沒有0~4π鑒相范圍的芯片?

2015-04-17 09:24:14

。PLL 切換到外部環路。鑒相器和電荷泵配合外部環路濾波器工作,形成一個閉環,確保PLL 鎖定到所需頻率。校準大約需要94,208 個鑒頻鑒相器(PFD) 周期;對于一個30.72 MHz fPFD

2018-08-04 15:00:17

各位老師專家好,我剛接觸這方面的東西有些不太明白的地方,謝謝大家的幫助。我想將AD8032用作鑒相器,有以下兩個個問題:1、芯片鑒相輸出端輸出的信號是與兩路輸入信號相位差成正比的直流電壓,還是 需要加環路濾波器才行;2、是否有實現鑒相功能的現成評估板,大概多少錢

2018-10-31 09:12:38

異或門鑒相器具有何種鑒相特性呢?

2023-04-24 11:39:05

根據一種雷達微波鎖相本振的需要,本文作者研制了一個X波段的微波鑒頻器。這個鑒頻器的研制早在1989年就已完成,于1991年投入小批量生產。它的鑒頻特性好,性能穩定可靠,在生產過程中已經表現出良好的社會效益和經濟效益。

2019-08-20 07:25:39

求教各位大神有用過AD9901這款鑒相芯片嗎,為什么我輸入兩列1MHZ占空比不同的方波,輸出始終在直流4V左右,而不是我想得到的兩列方波的異或輸出。還有AD9901KQ和AD9901TQ哪個是TTL電平啊,有沒有用過這款芯片的請賜教啊

2014-06-05 21:06:24

我用DSP芯片發出兩路有相位差的25KPWM方波進入CD4046的3腳和14腳,為什么沿上升沿觸發的鑒相器2輸出的13腳非常亂?仿真電路圖如上傳文件。。PS:CD4046用萬用板搭的。

2012-11-15 20:53:29

相對光電編碼器的鑒相和計數電路

2019-09-16 06:25:02

請問一下鑒相器ADF4106在上電后但是未配置數據之前,其I/O口是處于一個什么狀態?具體如MUXOUT管腳是什么狀態?

2018-08-14 07:57:12

正常置數。以上是遇到的問題,由于印制板已投產,無法實現分別上電,請問如何在同時上電的情況下解決鑒相器SPI置數無效的問題,謝謝。

2018-08-22 08:23:13

一般經典的鎖相環推導公式中鑒相器的鑒相靈敏度都是v/rad,那ADF4153的輸出時電荷泵的電流,它和經典的鑒相器靈敏度之間有什么關系?該怎么計算它的鑒相器靈敏度?

2018-11-06 09:02:53

0。為了驗證ADF4159芯片的問題,我把芯片CP輸出到環路濾波斷開,直接一個電阻進行取樣看看鑒相器有沒有工作。單獨只輸入參考時鐘,芯片RF不輸入信號時候,CP是有輸出。然后再單獨用信號源灌入

2018-08-14 07:18:34

我用兩個不同參考時鐘作參考,一個8M(步進100kHz),一個8.4M(步進400kHz),實際輸出的的相噪8.4M的在10kHz處會有突起的一段噪聲,使得10kHz處的phase noise只有

2019-03-12 09:18:04

的?舉例說明:鑒相頻率50M,輸出頻率5015M,這個時候在5000M和5030M觀察到雜散,約為-75dBc,同時輸出信號的參考雜散也較強,約為-82dBc,請問有什么解決辦法么?@

2019-02-15 13:26:51

AD8302的測量范圍很寬:0 - 2.7GHz。AD有沒有專用測相位差的鑒相器芯片,測量范圍比AD8302小。

2018-08-08 08:08:39

如下圖,手冊的鑒相器補償電流的計算公式,其中Tvco沒看出是什么意思,整個手冊找不到到底Tvco指的是什么。HMC832手冊里計算公式里沒有Tvco,粗略設計沒問題,但是要精度高,補償還是要算清的。求助!

2018-09-12 10:40:49

本來想試一下用這種結構(拉扎維書中)來對兩路有延時的數據進行鑒相的,即CK和Din都是輸入數據,后來自己畫了一下發現不行的。。。所以請問大佬們對兩路NRZ數據鑒相有什么好主意嗎?

2021-06-25 07:34:04

將模擬鑒相器輸出與頻率牽引輸出相結合的方法

2019-09-26 09:00:59

濾波器工作,形成一個閉環,確保PLL鎖定到所需頻率。校準大約需要94,208個鑒頻鑒相器 (PFD) 周期;對于一個30.72 MHz fPFD,這相當于3.07 ms。校準完成后,PLL的反饋操作使

2018-10-31 10:16:46

帶寬1MHz~3GHz或更寬,希望能同時鑒頻鑒相,貴司大多RMS Responding Detector都不能鑒相。如果沒有集成的芯片那就只好單獨采用鑒相器了。

2018-08-09 08:55:13

有沒有哪位大佬做過雷達中相位干涉儀中數字鑒相的模塊呀

2019-03-30 20:58:50

模擬鑒相器邏輯圖

2020-03-16 09:00:30

鎖定的時候參考時鐘和反饋的時鐘沒有完全同步,鑒頻鑒相器顯示的結果是這樣的,但是電荷泵不放電,是什么原因?

2021-06-24 07:17:06

請問在電子電路中鎖相環和鑒相器的電路結構是什么樣的?它是如何實現此電路功能的?可否詳細解釋一下?

2024-02-29 22:34:45

有沒有人做過鑒頻鑒相器的仿真?

2014-08-14 20:31:18

概述:TLC2932是德州儀器公司出品的一款鎖相環電路(PLL)芯片,它由壓控振蕩器和以沿觸發方式工作的鑒相器(PFD:phflse frequency deteclor)組成。

2021-04-08 07:48:53

難道說鑒相器也有鑒頻的功能嗎?假設初始狀態我的參考頻率和vco的自由震蕩頻率不一樣,電路是怎樣達到使頻率相等的平衡狀態的呢,我覺的不太好理解,因為這是2個不同頻率的信號輸入鑒相器,這怎么比較相位差啊。。

求高手指點一下

2023-04-24 10:33:47

工藝,封裝形式為16-TSSOP。 性能接收發射雙通道頻率合成器工作頻率范圍: 10MHz~1.3GHz雙模前置分頻器: 64/66無死區鑒頻鑒相器(PFD)可編程電荷泵電流:200uA, 400uA

2016-03-12 14:42:42

本文探討鑒頻鑒相器(PFD)設計中死區的產生原因和消除方法。設計了一種用于高速鎖相環的零死區PFD。這種PFD采用無反饋回路結構,在保證死區為零的前提下,兼顧功耗和速度性

2010-08-04 11:39:23 42

42 PFD1K-鑒頻鑒相器具有雙40 GHz預分頻器的8 GHz相位頻率檢測器ICPFD1K是一款具有全差分輸入和輸出的高頻相頻檢測器。它具有雙7位高速預分頻器,允許PFD1K在

2024-02-29 13:56:31

相位鑒頻器實驗

一、實驗目的 1 .了解實現鑒頻的基本方法。 2 .熟悉電容耦合式相位鑒頻電路的基本工作原理。 2 、熟悉鑒頻

2008-10-21 12:54:28 7902

7902

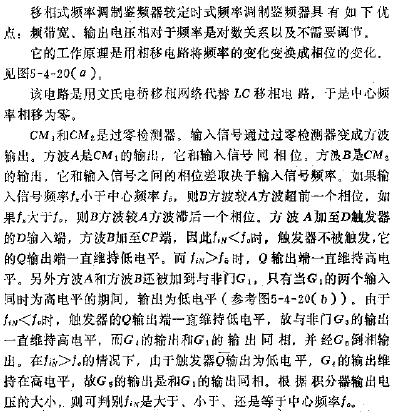

移相式鑒頻器

2009-04-13 11:05:55 1418

1418

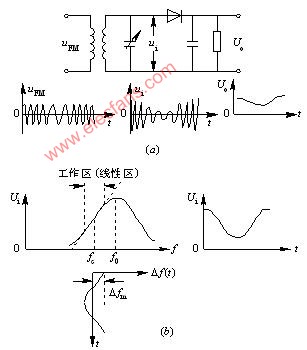

振幅鑒頻器原理

鑒頻方法的分類 (1) 直接鑒頻法:是直接從調頻信號的頻率中提取原來調制

2009-06-29 10:56:20 7012

7012

正交鑒頻器,正交鑒頻器原理是什么?

乘積型相位鑒頻(或稱正交鑒頻器,或稱差動峰值鑒頻器)

2010-03-22 15:56:43 5830

5830 斜率鑒頻器,斜率鑒頻器電路及原理

①單失諧回路斜率鑒頻器

電路

2010-03-22 15:58:51 14932

14932

電子發燒友App

電子發燒友App

硬聲App

硬聲App

42

42

評論