運算放大器作為常見的模擬電路模塊,設計好運算放大器對于模擬電路設計入門具有很好的幫助,學好運算放大器的電路設計和不同參數如靜態工作點、小信號增益Gain,相位裕度PM、輸入阻抗Rin、輸出阻抗Rout、環路增益loop gain和環路PM、共模抑制比CMRR、噪聲Noise、電源抑制比PSRR、大信號壓擺率SR、瞬態仿真tran、穩定性零極點分布仿真PZ、輸入輸出電壓范圍….等參數的仿真設置和仿真對于運放的學習具有重要的指導作用,本篇主要總結運算放大器相關的仿真設置和作者在仿真過程中的總結。

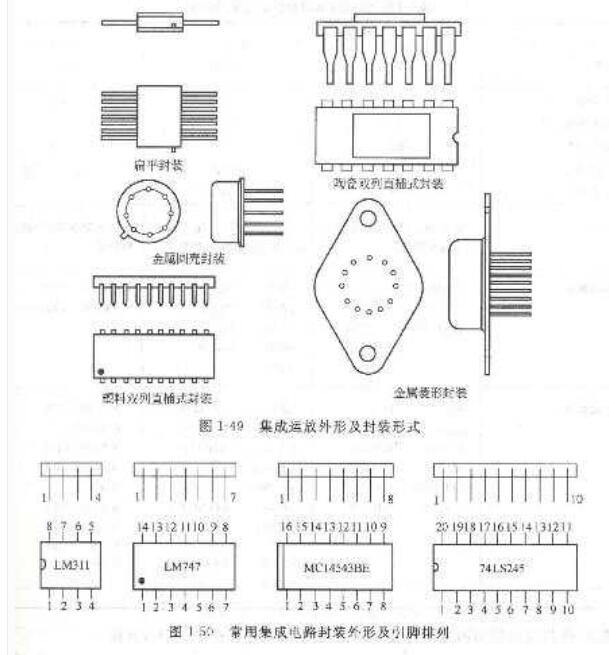

運放的常見種類

差分輸入單端輸出的運放

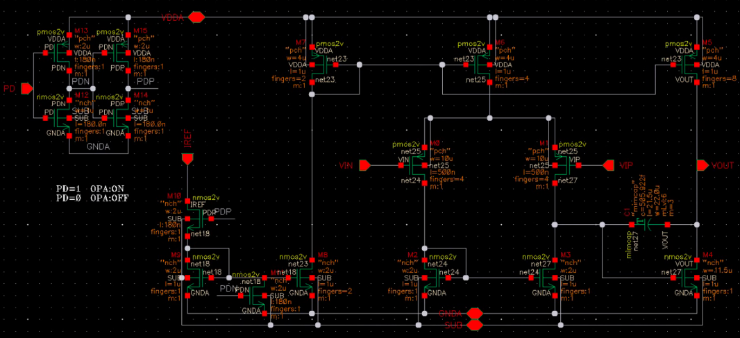

圖1 差分輸入單端輸出運放

圖1便是常見的兩級差分輸入單端輸出的兩級運放,第一級采用電流鏡作為負載將輸入

電壓轉換為電流后又通過負載電阻轉換為電壓給輸出級進行提供靜態工作點和傳遞小信號電壓,第二級首先將小信號電壓轉轉換為電流后,后又在輸出高阻態下重新轉換為電壓信號;該種結構的重要優點就是輸出級采用class-AB的輸出方式具有較寬的電壓輸出范圍,一般把輸出電壓的靜態工作點設置在電源電壓的一半也是為了保證輸出電平具有較寬的范圍,此種運放在穩定性方面為了提高相位裕度PM常常在第一級與第二級放置極點分離電容,分離第一級與輸出端的極端距離實現較高的PM,或者在第一級與第二級間放置電阻與電容串聯的LHP零點用來補償極點實現較高的PM。

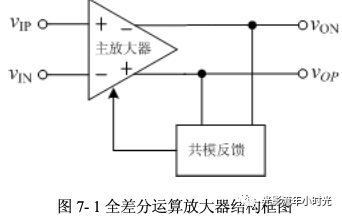

差分輸入差分輸出運算放大器

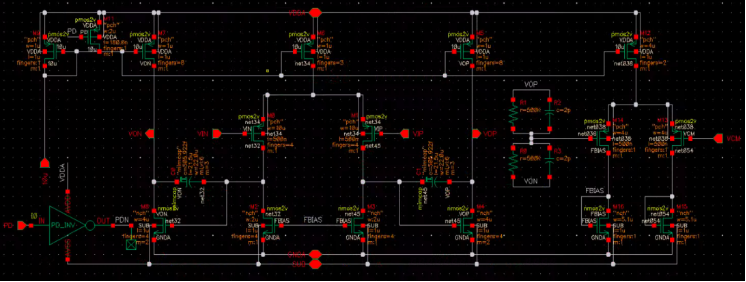

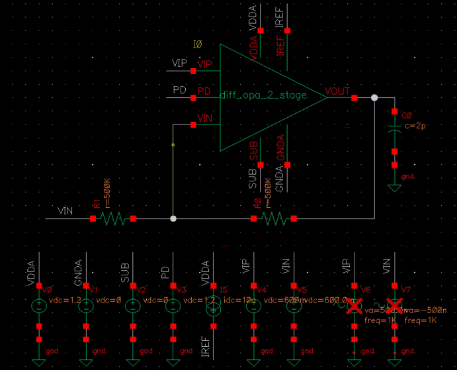

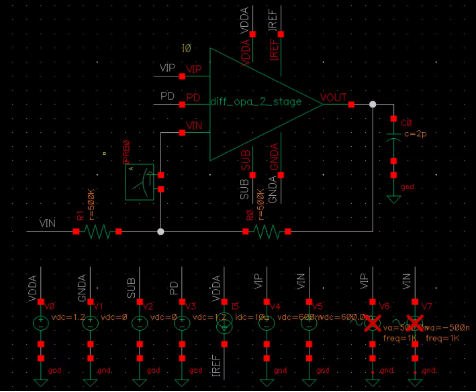

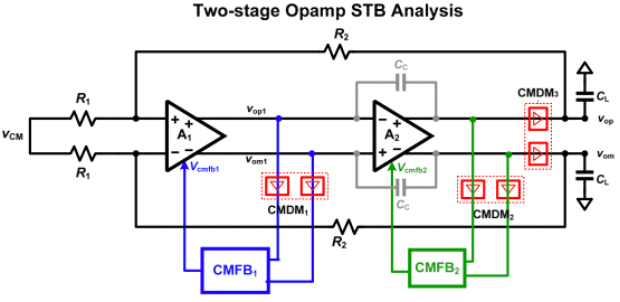

圖2 差分輸入差分輸出兩級運算放大電路原理圖圖2是常見的PMOS輸入的差分輸入差分輸出的兩級運算放大電路的原理圖,其中第一級采用恒流源作為負載,第二級采用class-AB輸出結構為了提高輸出電壓范圍,與圖1差分輸入單端輸出結構相比,圖2電路增加了共模負反饋電路CMFB用于抑制兩個支路共模電平的穩定和一致性,具體原因可以參考拉扎維、艾倫、格雷教授的模擬CMOS集成電路書中對這部分有具體的講解;CMFB電路對輸出電壓進行采集并將輸出結果負反饋給第一級電流源作為靜態偏置用于調節第一級和第二級兩個支路電平的穩定。差分輸入差分輸出電路在實際系統中采用較多,主要是因為與圖1電路相比其輸入不僅可以對共模信號進行抑制,在輸出級也可以抑制共模電平,將會增加系統的整體性能。

運算放大器穩定性

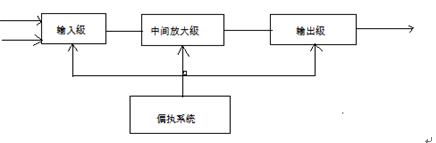

在我們一開始學習運算放電路的時候,我們常常會拿到圖1和圖2運放電路圖仿真其小信號特性中的幅頻特性和相頻特性,判斷電路的穩定性;然而實際情況下,圖1和圖2為開環的運算放大器電路并不存在穩定性問題,那我們為什么還要仿真并計算出電路的增益Gain和PM(相位裕度)?這部分主要回答這個問題,在回答這個問題前,我想說下運放的實際使用過程中我們大部分都是讓其工作在負反饋的閉環狀態,這主要是因為普通的運算放大器具有較高的小信號開環增益,其實際在固定的電壓下具有較小的線性工作范圍,如果超出其輸入范圍輸出的電壓不是高電壓就是低電壓,因此實際使用過程中均是使用運算放大器結合不同的輸入和輸出反饋類型形成閉環工作,實現較高精度的運算電路如加,減,乘除等這便是利用增益換取精度帶來的結果,這也擴大的放大器的使用范圍,讓其成為模擬電路最重要的模擬單元模塊。接下來便會介紹負反饋系統以及運算放大器在負反饋系統中的穩定性相關問題。

負反饋系統

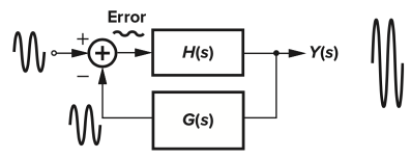

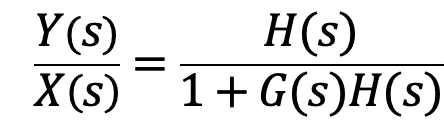

圖3 常見的負反饋系統框圖圖3為常見的負反饋系統框圖,主要包括首先輸入信號經過H(s)單元進行放大,然后經過反饋單元G(s)進行一定程度衰減后與輸入進行相減再進一步放大,通過負反饋的作用,輸出信號最終動態穩定在一個固定的數值上,而不是放大到電源電平電壓或者地電平,圖3中系統的傳輸函數如下:

根據Barkhausen’s 判據如果系統傳輸函數中G(s)H(s)=-1整個傳輸函數將會趨于∞系統將會處于不穩定系統,該判據具體產生不穩定表達如下:

即如果在一個頻率上G(s)H(s)相位發生了180度移動,并且如果此時系統的G(s)H(s)的幅度為1整個負反饋系統將會發生振蕩現象,因此為了避免上述情況的產生我們常常是的在G(s)H(s)增益為1的時候觀察此時相位與180度相位差定義為PM,如果此時PM大于零可以認為系統處于穩定狀態,但是在實際使用過程中考慮PM較低將會對輸出信號上升時間、過沖等問題帶來較大的影響,我們常常在設計過程中使得

PM>45

度作為我們負反饋系統設計的目標。在實際的運算放大器負反饋系統的過程中我們常常定義H(s)為運放的開環增益用Aopen loop代替,G(s)作為反饋電路電源常常使用?代替,G(s)H(s)我們常常成為環路增益loop Gain,整個負反饋系統的傳輸函數稱為系統的閉環增益Aclose loop,接下來將會介紹在運算放大器電路中開環增益、環路增益、開環增益所代表的具體含義和區別。

開環增益、環路增益、閉環增益

首先我要介紹下上述三種增益在負反饋運放電路中實際所指,開環增益顧名思義就是開環放大器如圖1,2電路中運放的小信號增益,此時僅僅代表運放的本身增益特性,高增益運放電路具有較高的性能常常應用于儀表等高精密儀器系統中,如何提高運算放大器開環增益有不同的電路結構和方法可以參考拉扎維書中的增益改善方案;環路增益是反饋電路單元與放大器開環增益的乘積,由于反饋單元的反饋系數?通常小于1因此環路增益一般小于運算放大器的開環增益,環路增益根據我們對上一部分負反饋系統描述可以知道主要用來判斷運算放大器組成的負反饋系統的穩定性,通常看環路增益的PM是否滿足要求進一步判定系統穩定性,因此在仿真過程中需要得到環路增益的小信號幅頻特性和相頻特性曲線是我們判定系統是否穩定的重要依據;閉環增益對于我們實際使用過程來說它是實際我們所獲得的運放組成的負反饋系統的實際增益,因此組成不同的反饋電路結構我們可以獲得不同的運算電路和放大倍數電路,通過觀察閉環增益的傳輸函數(結合負反饋系統中的傳輸函數)我們可以發現如果放大器的開環增益如果遠大于1,整個系統的閉環增益是反饋單元反饋系數的倒數,這也是我們犧牲放大器高增益換取系統高精度放大倍數的目的。接下來我們就要回答上面一開始提到的為什么我們學習運放電路會直接仿真開環運放的PM而不是直接仿真閉環負反饋系統下的運放的PM來判定系統穩定下,難道只要開環運放PM滿足大于45度要求,閉環狀態下該系統的環路增益的PM也一定會大于45度?帶著這個問題我們來看下下面這幅圖4:

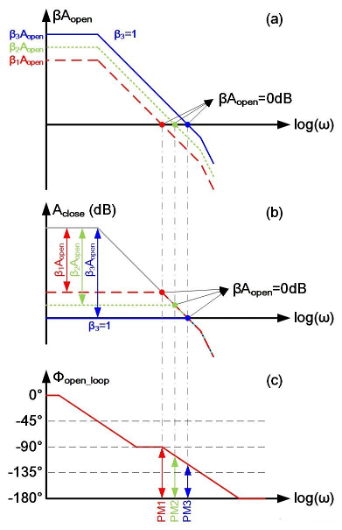

圖4 環路增益、開環增益、閉環增益與相位裕度關系

觀察圖4(a)我們可以發現其為環路增益幅頻特性曲線,其中三個曲線的反饋系

數關系如下

我們可以發現三個曲線與橫坐標的交點(增益為1)分別是藍色曲線>綠色曲線>紅色曲線,結合圖4(c)可以看出PM3>PM2>PM1,我們可以得出結論反饋系數越大,相位裕度PM越小。如果我們仔細看圖4(1)藍色曲線我們可以發現此時環路增益就是我們運放電路的開環增益,一般反饋單元的反饋系數均是小于1因此我們直接看運放電路開環的相位裕度PM是該運放最差的PM,如果連運放在開環狀態下PM都滿足大于45度,那我們就可以說該運放組成的負反饋系統(反饋系數小于1)的PM一定滿足大于45讀的穩定性要求這也就是為什么我們一開始學習時開環放大器不存在穩定性問題,還要仿真開環放大器的相位裕度PM大于45度的原因?這里還有一個問題就是,我們穩定目標只要負反饋系統的環路增益PM大于45度,而我們因為開環運放的PM已經大于45度,其組成的負反饋系統的相位裕度一定大于45度是否會造成相位裕度的浪費,這一點我想說的是,對于初學者我們可以不關注這些浪費,我們只要了解上述三種增益的關系以及如何判斷環路穩定便達到學習要求;對于實際公司和設計使用中,這種裕度浪費帶來的是電流的增加帶來功耗的浪費,我們都知道目前降低電路功耗成為延長電池壽命的重要目標,也是我們電路設計永恒的話題。因此在公司和產品的角度我們一般是對固定反饋系數的運放,實際上我們可以回歸巴克豪森判據的本質,去得到屬于該反饋系數的環路增益響應的幅頻特性和相頻特性曲線,在閉環的角度仿真電路使其滿足PM大于45度的穩定性要求。在判定穩定性方面工業界還有一種閉合速率角度快速判定系統是否穩定,原理圖下通過觀察運放電路的開環增益和反饋系數的幅頻特性曲線交點,此時二者斜率之差的絕對值與20dB大小關系,如果二者之差等于20dB可以判定此時相位裕度的大小45度

運算放大器各種指標的仿真

本部分主要介紹運算放大器電路所涉及到的不同指標仿真方法,具體包括靜態工作點、小信號增益和相位曲線、CMRR、PSRR、Noise、輸入輸出阻抗、環路增益和閉環增益等指標仿真。

靜態工作點Q

我們都知道所有電路建立合理的工作點是所有其他指標設計的第一步,因此設置合理的靜態工作點使得運算放大器內部的管子工作在合適的region是我們設計電路最重要的步驟,這可以采用仿真器中的dc進行仿真,并通過標注管子的節點電壓和靜態參數判定是否滿足要求。

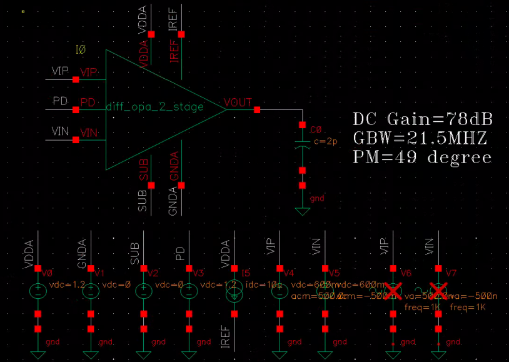

小信號AC仿真

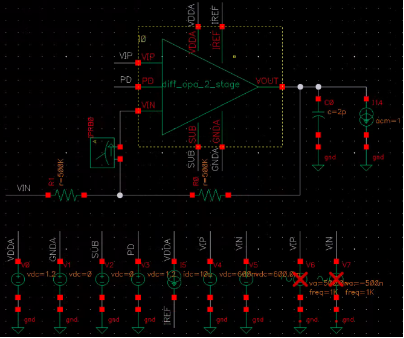

圖5 圖1電路的運放測試原理圖小信號電路在仿真過程中主要可以仿真信號的幅頻特性和相頻特性曲線直接讀出電路的開環增益和PM數值及單位增益頻率大小。在配置上對于輸入VIP和VIN中vdc直流電源首先需要設置共模電平(本電路為600mV)以及在VIP上vdc設定AC幅度大小為0.5V,VIN的vdc上AC幅度設定為-0.5V這是為了保證差分小信號輸入大小為0dB,此時輸出端電壓大小就是整個運放的開環增益所進行一種設定。

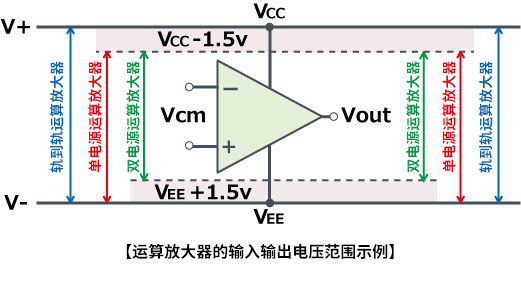

電源抑制比PSRR

電源抑制比PSRR作為對于運放對于電源噪聲和干擾的一種抑制特征指標常常也作為電路仿真之一,主要包括正電源抑制比+PSRR和-PSRR,對于+ PSRR仿真方法如下,此時圖5中VIN和VIP中的vdc僅保存直流電壓600mV作為共模電平,AC幅度大小為0;此時在VDDA的vdc的AC幅度大小為1,此時得到輸出VOUT的AC仿真幅頻特性曲線就是+PSRR,對于-PSRR在GNDA上進行上述操作并保證VDDA上AC幅度大小為零即可。

共模抑制比CMRR

共模抑制比反映的是電路對于差分信號的抑制作用,一般是差模信號增益除以共模信號增益,第2部分我們通過設定AC小信號仿真得出的就是運放電路的差分信號增益;此時只需要將圖5電路中VIP和VIN電路中的vdc的共模電平設定為600mV和AC模大小都為1代表VIP和VIN完全相同,此時小信號ac仿真得出的就是共模信號增益;此時一般我們都是選擇dB單位進行繪制相應曲線,只要將二者曲線相減便可以得到CMRR大小。

PZ、Noise、tran仿真

此部分不做過多敘述,只要配置好ADE仿真器便可以完成結果仿真,重點講一下負反饋電路中(如經典負反饋系統LDO中)PZ仿真需要把反饋回路打開才能得到正確零極點信息,否則結果會出現異常如有半平面極點(系統不穩定),Noise仿真可以打印出不同管子對于噪聲的貢獻,可以精確進行調整(增大管子寬長比)以降低管子對噪聲的貢獻實現低噪聲運放電路的設計。

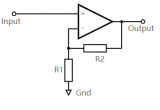

閉環增益

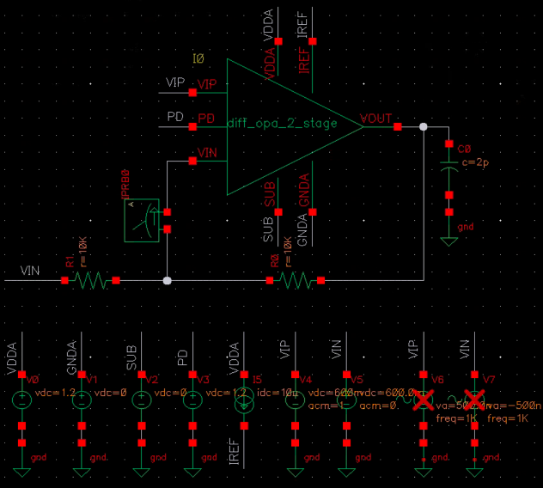

圖6 閉環負反饋運放電路閉環增益作為負反饋運放電路的實際增益大小,我們需要得到期具體數值大小,在仿真中我們需要主要如下:此時VIN上只有共模電平600mV,VIP的vdc上共模電平為600mV,AC幅度大小為1通過仿真ADE中ac仿真可以得出運算放大器電路的閉環增益大小,對于差分輸入和差分輸出負反饋運放電路來說,此時VIP和VIN共模電平均是600mV,AC幅度大小分別是0.5和-0.5V此時得到差分輸出大小為該系統的閉環增益,圖5中需要注意的是為啥VIN位置不是GNDA,我們在學習模電過程中記得此時應該是地,特別是在源極跟隨器負反饋電路也沒有對輸入進行加共模電平,這一點是我們的誤區,所有負反饋電路都需要保證輸入管處于正常打開狀態,至于源極跟隨器輸入管的偏置是來自輸出的靜態電平因此不需要在加入偏置,這一點要牢記否則電路閉環增益得不出正確的結果。

環路增益

圖6 差分輸入單端輸出閉環負反饋運放電路關于環路增益的仿真方面此時要分差分輸入單端輸出和差分輸入差分輸出兩種情況來進一步說明,如圖6所示作為第一種差分輸入單端輸出閉環負反饋運放電路環路增益所有配置與6中仿真閉環增益VIP和VIN配置相似,僅從模擬庫增加一個iprobe模塊進行stb仿真即可,此時便可以得出環路增益大小和環路相位裕度大小判定閉環負反饋電路的穩定性。

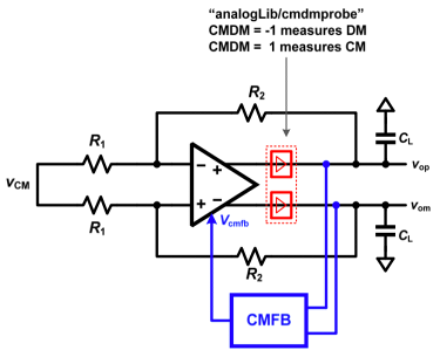

圖7 差分輸入差分輸出閉環負反饋電路

第二種對于圖7所示的差分輸入差分輸出閉環負反饋電路來說,通過從模擬庫添加CMDM(-1差分環路增益,1代表共模環路增益)也可以添加diffstbprobe進行stb仿真得出圖7所示電路的環路增益和PM判定系統穩定性,其中需要注意的是輸入必須加上共模電平使得輸入管正確打開工作。

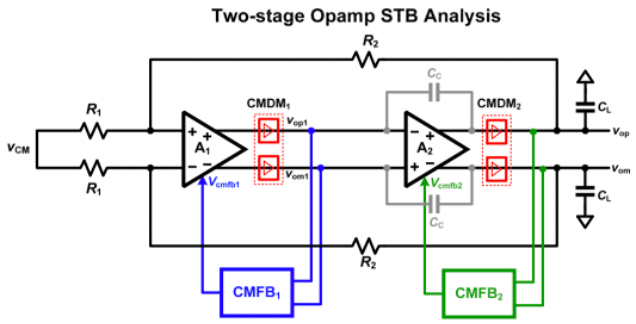

圖8兩級運放STB分析

?

圖9 兩級運放STB分析

圖8和圖9中CMDM放置不同位置可以得到不同的環路響應,其中圖8中CMDM1只能測量第一級共模環路響應,CMDM2可以得到整個第一級和第二級級聯負反饋系統的差分環路響應和第二級共模環路響應。圖9中CMDM1和CMDM2分別僅測量第一級和第二級共模環路穩定性,CMDM3可以得到整個負反饋系統的差分環路穩定性,一般有時候如圖9中單級的共模環路穩定性也可以在CMFB1和CMFB2輸出加上iprobe進行STB仿真測量。開關電容CMFB電路穩定性分析未在本部分列出。

閉環輸入輸出阻抗大小

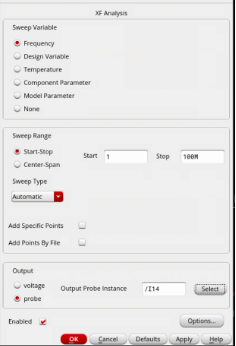

關于仿真輸入和輸出阻抗大小的方法很多,本篇主要介紹一種利用小信號xf方法進行電路仿真方法,利用原理是添加一個idc電流源將AC幅度設定為1此時測量輸出端電壓即是此時閉環系統輸出端的阻抗大小(單位電流測電壓),其中圖11為XF仿真器設置,閉環輸入阻抗大小把輸出電流idc放置在VIP即可,此時注意VIP需要斷開,如果此時VIP沒有斷開此時小信號電源相當于地短路此時idc被短路無法測出輸入阻抗大小,VIN的共模電平為600mV,AC幅度大小為0。(若計算輸入和輸出跨導用vdc其中AC=1替換圖10中的idc)

圖10 閉環放大器電路輸出阻抗仿真原理圖

圖11 XF閉環放大器電路輸出阻抗仿真器設置

其他指標

其他指標如大信號壓擺率大小、輸入和輸出電壓工作范圍大小、小信號和大信號階躍信號瞬態響應和差分DM和CM瞬態響應等其他指標由于篇幅大小和時間原因本篇內容沒有具體列出。

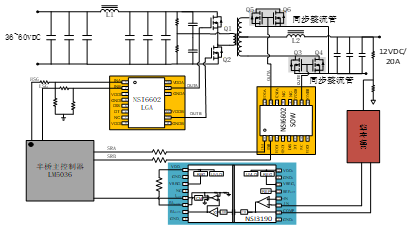

閉環負反饋電路遇到問題

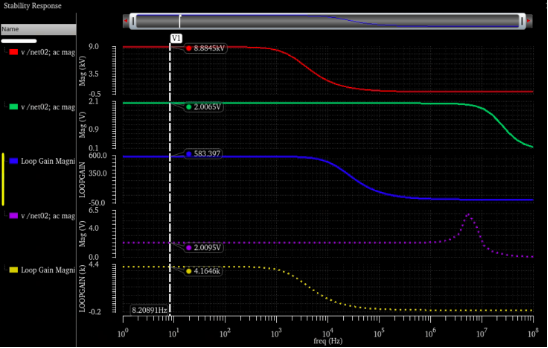

本人在仿真運算放大器電路中遇到一個問題如下圖12所示,首先作者仿真得到該運放電路的開環增益如圖13中第一條紅色曲線低頻增益為8884.5,然而在圖12中兩個電阻為10kohm是根據理論計算此時放大器增益應該為2此時通過仿真可以得出圖13中第二條、第三條曲線所示此時閉環增益為2.0065然而此時環路增益大小為583.397不滿足此時環路增益應該為開環增益與反饋系數0.5的乘積大小?本人通過增加圖12中電阻大小為1Mohm時,此時閉環增益和環路增益大小為圖13中第四條、第五條曲線所示,此時閉環增益為2.0095,環路增益大概為4164非常接近理論計算環路增益。因此雖然閉環增益都是為2時,電阻大小組織大小不同環路增益會產生不同,這一點一開始本人懷疑是不是由于低電阻10kohm反饋時,此時運放的開環增益由于輸出端具有高阻抗(NMOS和PMOS溝道電阻并聯)導致了運放開環增益發生變化降低,進一步導致環路增益降低,當反饋電阻增大到1Mohm左右時,由于此時反饋電阻對運放開環增益影響不大,因此環路增益如我們計算相似。不知道這種解釋是否合理,心中一直存在疑問。希望懂得同行,可以給予解釋。

圖12 差分輸入單端輸出負反饋運放電路

圖13運放電路輸出環路增益和閉環增益及開環增益

電子發燒友App

電子發燒友App

評論