的評估方法,不代表可以在應(yīng)用電路對共模信號實現(xiàn)有效抑制。本篇解析放大器共模抑制比參數(shù)定義與其影響的評估方法,以及結(jié)合一個實際案例討論影響電路共模抑制的因素。

2020-10-14 16:41:45 10135

10135

上個月做電阻抗法血細(xì)胞計數(shù)(又叫庫爾特原理)預(yù)研,考慮用儀表放大器試試效果,因為它的共模抑制比CMRR非常高如低頻到60Hz能達(dá)到120dB;實測效果還不錯的。現(xiàn)在這個項目已經(jīng)停了……不過還是

2022-11-09 16:54:48 3310

3310

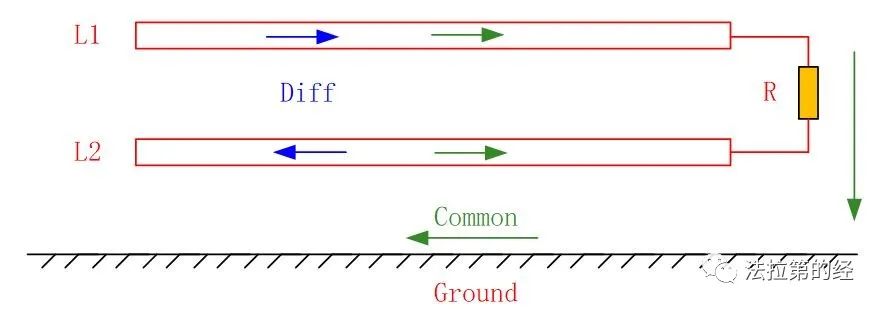

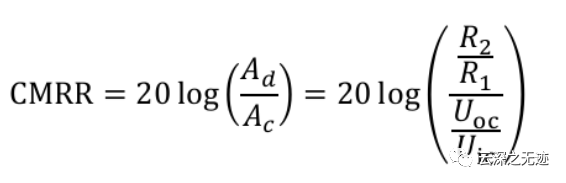

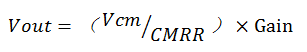

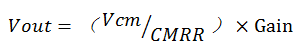

實際上,共模電壓的變化會引起輸出變化。 運算放大器共模抑制比(CMRR)是 指共模增益與差模增益的比值。

2023-02-12 17:08:42 2184

2184

今天繼續(xù)給大家分享運放另一項指標(biāo)——共模抑制比(CMRR)。

2023-10-01 13:10:00 1514

1514

號,幅度較小,源阻抗較高,并且共模電壓變化比較大。放大這些信號通常直流精度要求較高,失調(diào)電壓,失調(diào)電流通常是我們關(guān)注的參數(shù),然而還有一個非常重要的參數(shù),CMRR,共模抑制比也會對儀表放大器的精度造成

2022-11-14 06:20:19

并不是所有架構(gòu)造而平等。就像您不會選擇一個單一工具來建造一個房子一樣,您不應(yīng)該假設(shè)所有儀表放大器(INA)在所有應(yīng)用中都能發(fā)揮最佳效用。共模抑制比(CMRR)和共模抑制(CMR)測量差分輸入放大器

2019-03-21 06:45:01

號,幅度較小,源阻抗較高,并且共模電壓變化比較大。放大這些信號通常直流精度要求較高,失調(diào)電壓,失調(diào)電流通常是我們關(guān)注的參數(shù),然而還有一個非常重要的參數(shù),CMRR,共模抑制比也會對儀表放大器的精度造成

2019-03-12 06:45:04

放大器內(nèi)部,其獨特的結(jié)構(gòu)使它具有高共模抑制比、高輸入阻抗、低噪聲、低線性誤差、低失調(diào)漂移增益設(shè)置靈活和使用方便等特點,使其在數(shù)據(jù)采集、傳感器信號放大、高速信號調(diào)節(jié)、醫(yī)療儀器和高檔音響設(shè)備等方面倍受青睞

2014-05-07 18:31:20

儀表放大器AD620的共模輸入范圍超過電源電壓,會影響共模抑制比嗎?比如AD620采用正負(fù)5V電源供電,放大倍數(shù)為10倍,測試時共模輸入范圍為7.07V / 100Hz,會影響共模抑制比嗎?

2023-11-15 06:49:17

電壓或噪聲。此外,其只有一個高阻抗輸入。 常見的單端放大器只有一個高阻抗輸入,輸入和輸出共用接地參考。因此,無法抑制共模信號。圖 2現(xiàn)代的集成電路儀表放大器相比使用分立式運放和電阻器的儀表放大器有著

2017-04-01 14:40:53

噪聲和其他信號耦合到跟蹤上開辟了可能性。參考引腳上附加的電阻將降低大多數(shù)INA提供的高共模抑制比(CMRR)。因此,使參考引腳緩沖電路盡可能接近INA的參考引腳。圖3顯示了糾正這三個錯誤的布局。在圖3

2018-08-06 19:27:44

我在上一篇博客文章中討論了為什么儀表放大器電源抑制比 (PSRR) 及共模抑制比 (CMRR) 會隨放大器增益的提高而改善。回到儀表放大器的簡化模型(如圖 1 所示)中,我們可以再次回想起 PSRR

2018-09-19 10:53:42

,都需要電源的明顯變化!但一定要記住:共模抑制比 (CMRR) 和 PSRR 都是輸入?yún)⒖紖?shù):(1) PSRR 和 CMRR 定義為輸入失調(diào)電壓變化 ΔVOS(IN) 與電源電壓變化 ΔVS 或共模電壓變化 ΔVCM 的比值。為了了解增益對這些參數(shù)的影響,請將大多數(shù)儀表放大器看成兩個串行的放大器級…

2022-11-23 07:31:05

件的工作范圍。 2 儀表放大器在傳感器信號調(diào)理電路中的應(yīng)用 儀表放大器是一種高增益、直流耦合放大器,他具有差分輸入、單端輸出、高輸入阻抗和高共模抑制比等特點。差分放大器和儀表放大器所采用的基礎(chǔ)部件

2014-06-22 18:45:08

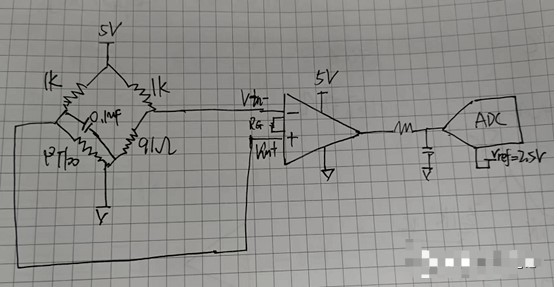

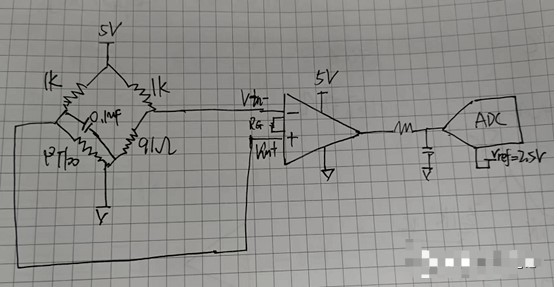

輸出信號升高同等電壓。這樣就能簡單精確地將儀表放大器的輸出調(diào)整到ADC所需的輸入電平,從而可以使用ADC的完整輸入范圍,同時提高分辨率。在具有高共模信號的情況下,另一優(yōu)勢是極為出色的共模抑制比和高精度。

2019-07-19 07:24:39

本儀表放大器是由三個OA27P集成運算放大器組成,OA27P的特點是低噪聲、高速、低輸入失調(diào)電壓和卓越的共模抑制比。儀表放大器電路連接成比例運算電路形式,其中前兩個運放組成第一級,二者都接成同相輸入

2021-05-10 07:43:14

升高同等電壓。這樣就能簡單精確地將儀表放大器的輸出調(diào)整到ADC所需的輸入電平,從而可以使用ADC的完整輸入范圍,同時提高分辨率。在具有高共模信號的情況下,另一優(yōu)勢是極為出色的共模抑制比和高精度。圖1

2018-10-11 10:41:23

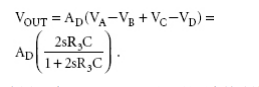

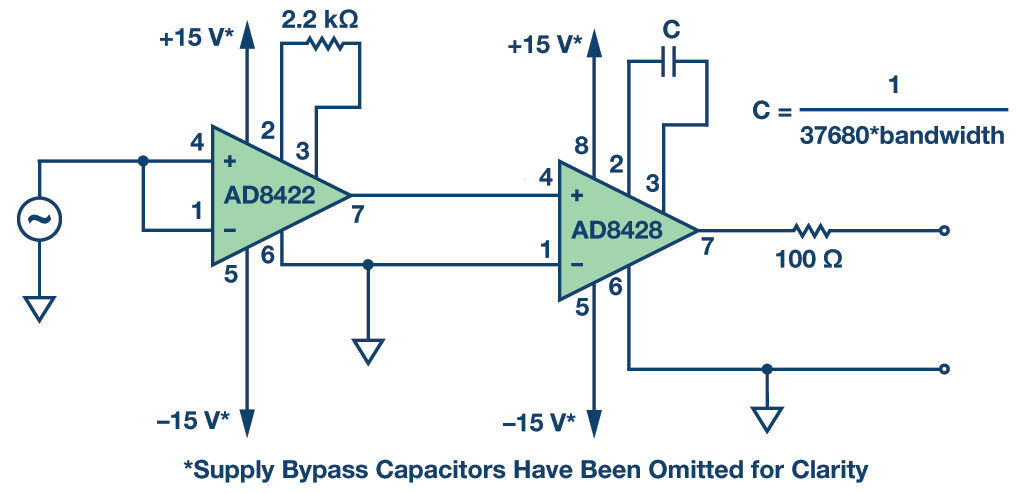

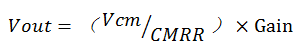

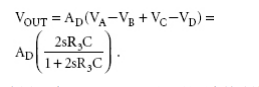

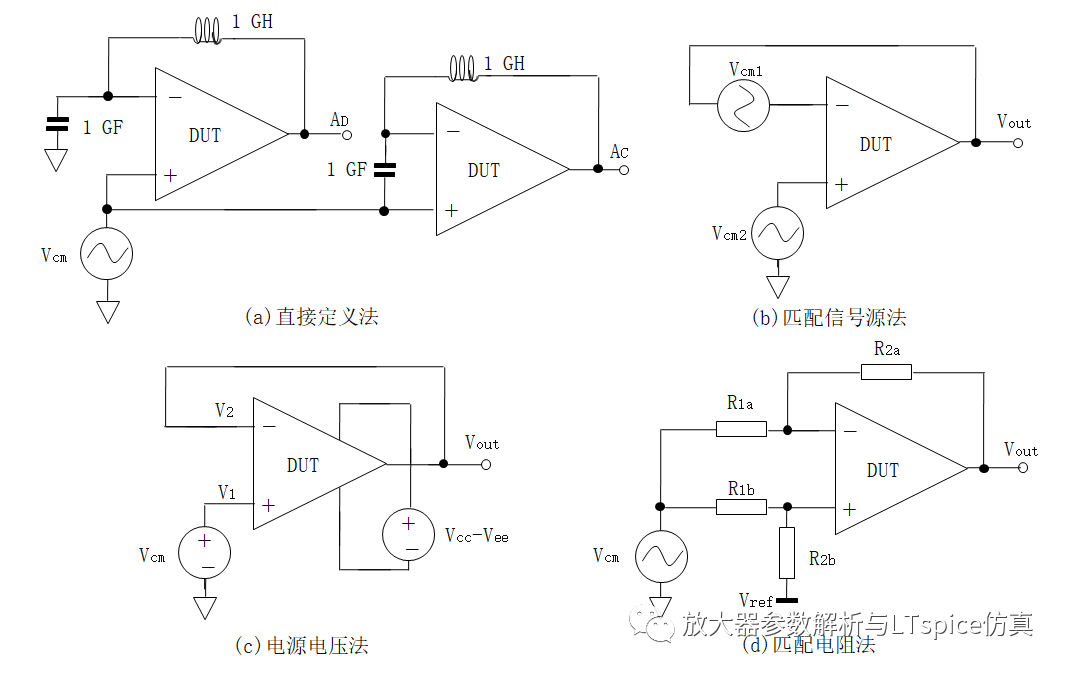

方法,在Allen書中都有相關(guān)的介紹。最近發(fā)覺對這些仿真電路的原理有點模糊(主要還是對于CMRR的仿真電路),在這里拿出來重新溫習(xí)一下下圖是共模抑制比仿真電路,通過ac小信號分析(兩個Vcm相同,都取 ac=1),分析Vout輸出的信號共模抑制比由電路分析看到: Vout=Adm?(V1?V2)+Ac

2021-12-27 07:24:51

我在找信號放大器的時候,有的給出了增益,類似于功率可以增加多少倍,有的給出了共模抑制比,這兩個我怎么分別?我最后的結(jié)果是看我的信號功率能否從-15dBm增加到10dBm,共模抑制比我怎么換算?

2018-08-09 09:48:40

常被誤用的放大器共模抑制比測量方法會存在哪些不足?有沒有一種有效測量共模抑制比電路方案介紹?

2021-03-11 06:00:18

電源或共模電壓變化產(chǎn)生的失調(diào)偏移時很容易產(chǎn)生困惑。這種困惑的根本原因如下圖所示:圖 1:儀表放大器的典型電源抑制比曲線在圖 1 中,放大器的電源抑制比 (PSRR) 隨放大器增益配置的升高而增加。這樣很

2018-09-19 11:00:26

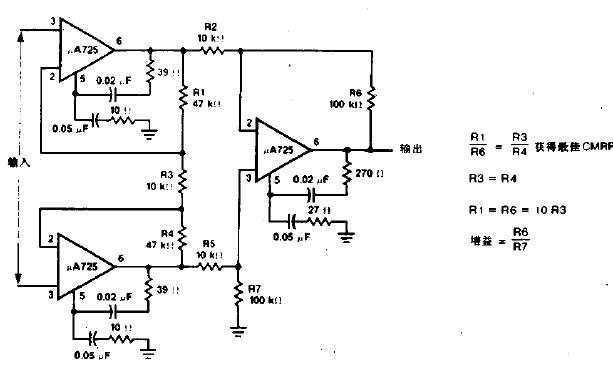

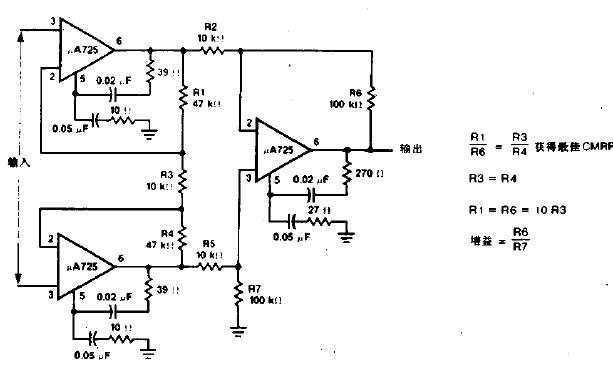

高共模抑制比儀用放大電路方案

2012-10-29 06:44:52

AD-運算放大器共模抑制比CMRR

2012-04-01 10:47:33

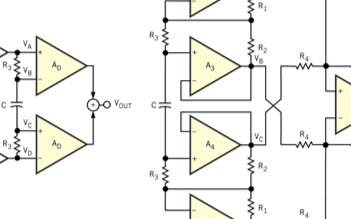

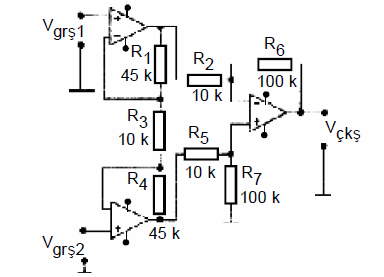

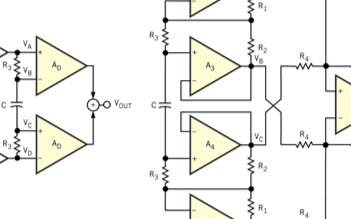

構(gòu)成的高共模抑制比儀表放大器(一)同相串聯(lián)差動放大器圖4為一同相串聯(lián)差動放大器。電路要求兩只運算放大器性能參數(shù)基本匹配,且在外接電阻元件對稱情況下(即R1=R4,R2=R3),電路可獲得

2018-10-08 10:27:27

到參考AD8221的本地接地的電壓。 共模抑制 高共模抑制比AD8221的一個優(yōu)點是,它比典型的儀表放大器具有更強(qiáng)的抗干擾能力,例如線路噪聲及其相關(guān)諧波。通常,這些放大器在200hz時具有CMRR衰減;通常

2020-07-17 14:40:58

%建立時間為12 μs,非常適合多路復(fù)用應(yīng)用;而且成本很低,足以實現(xiàn)每通道一個儀表放大器的設(shè)計。 儀表放大器特點:● 高共模抑制比 共模抑制比(CMRR) 則是差模增益( A d) 與共模增益( Ac

2012-12-28 23:38:18

和反饋電阻,以及保持放大器的溫度穩(wěn)定,可以降低噪聲。此外,采用對稱電路設(shè)計和適當(dāng)?shù)牡鼐€布局也可以有效地降低噪聲。

為了提高儀表放大器的共模抑制比(CMRR),我們可以采取一些措施。例如,增加差分輸入

2023-11-17 00:51:10

組成的。差分放大器和儀表放大器的區(qū)別差分放大器的劣勢在于輸入電阻造成的輸入阻抗低,同時還有高共模增益造成的低共模抑制比(CMRR)。而在儀表放大器內(nèi),因為緩沖電路的存在,這些都被克服了。同時在

2019-10-11 16:36:17

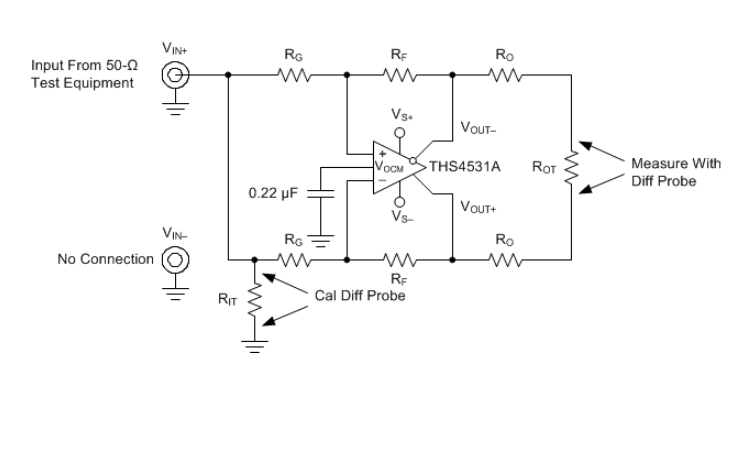

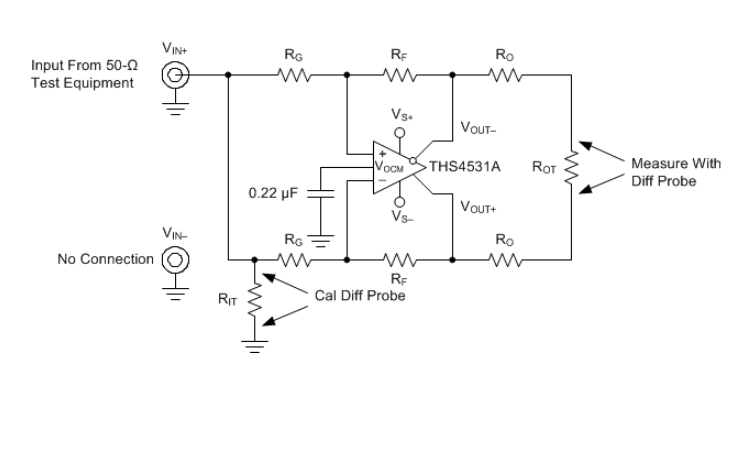

對于構(gòu)建儀表放大器的第二級電路,能否采用全差分的放大電路來進(jìn)行搭建,使其輸出仍為差分信號?第二級電路的CMRR需要多大才能滿足?我看TI上全差分放大器CMRR最大為140

2020-07-20 11:18:29

如圖所示,下面是一個交流耦合放大電路,在電路的差分輸入端輸入差模(100uV,10Hz)和共模信號(10V,10Hz),進(jìn)行電路的共模抑制比(CMRR)測試,測試發(fā)現(xiàn):

1、差分信號從INS+

2018-08-03 06:26:16

共模抑制比(CMRR) 是指差分放大器對同時加到兩個輸入端上的共模信號的抑制能力。更確切地說,CMRR是產(chǎn)生特定輸出所需輸入的共模電壓與產(chǎn)生同樣輸出所需輸入的差分電壓的比值。差分放大器共模響應(yīng),是指

2016-09-23 15:34:29

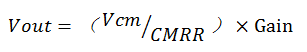

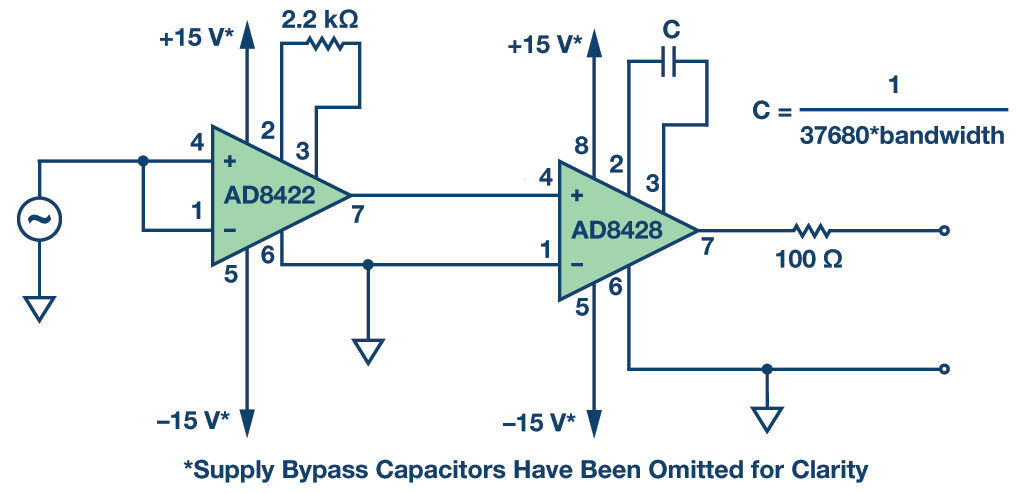

描述此設(shè)計為交流耦合的儀表放大器。更具體地講,該電路放大交流差動輸入信號,拒絕直流差動和共模信號。輸入為直流耦合,因此可以通過儀表放大器參考電壓的變動來抵消輸出偏移,實現(xiàn)有效的交流耦合。主要特色交流耦合 INA保持優(yōu)異的 CMRR拒絕直流和緩慢偏移可調(diào)的最低截止頻率

2018-08-21 07:57:21

偏移、低漂移、高增益以及優(yōu)良的共模抑制比為高性能儀表放大器提供了所需的特性。此外,電源的電流消耗非常低。圖4中的電路推薦用于共模輸入范圍相對較低且差分增益在10到1000范圍內(nèi)的應(yīng)用。這兩個運算放大器

2020-11-23 16:07:01

放大器在傳感器信號調(diào)理電路中的應(yīng)用 儀表放大器是一種高增益、直流耦合放大器,他具有差分輸入、單端輸出、高輸入阻抗和高共模抑制比等特點。差分放大器和儀表放大器所采用的基礎(chǔ)部件(運算放大器)基本相同,他們在

2018-11-01 15:21:45

電壓偏置的9個MOS管,并保持原有的功能和指標(biāo)不變。仿真結(jié)果表明,本文介紹的儀表放大器可通過片外電阻調(diào)節(jié)增益,放大倍數(shù)為14倍時,3dB帶寬為380kHz,共模輸入范圍為-1.4V至1.4V,共模抑制比和電源抑制比均遠(yuǎn)大于100dB。

2023-09-20 07:44:23

[td][/td] 如圖所示,如何設(shè)計AD8221交流耦合電路能:

1、降低噪聲,提高信噪比(SNR);

2、提高儀表運放輸入阻抗;

3、提高共模抑制比(CMRR)。

2023-11-17 09:47:43

通過精確匹配的電阻網(wǎng)絡(luò)提高差分放大器的共模抑制比

2021-01-28 06:19:27

提高差分放大器的共模抑制比,電阻的選擇很關(guān)鍵

2021-03-11 07:17:03

如何利用高增益運放,設(shè)計了一種具有高共模抑制比,高增益數(shù)控可顯的測量放大器。提高了測量放大器的性能指標(biāo),并實現(xiàn)放大器增益較大范圍的步進(jìn)調(diào)節(jié)。

2021-04-22 06:59:18

下圖是電子學(xué)第二版的一個差分放大電路,書中說這電路共模抑制比是10萬,這能從圖中算出來嗎?

2020-04-08 23:09:06

。高度匹配的電阻器確保設(shè)計人員能夠接近或達(dá)到放大器產(chǎn)品手冊所宣稱的性能指標(biāo)。共模抑制比為了在存在共模噪聲的情況下獲得精確的測量結(jié)果,擁有高CMRR是很重要的。輸入CMRR定義為差分增益與輸入共模至差分

2019-05-22 08:53:17

有時需要在有較大共模信號的情況下測量小信號。在這類應(yīng)用中,通常使用兩個或三個運算放大器的集成儀表放大器。盡管儀表放大器具有出色的共模抑制比(CMRR),但價格因素,性能指標(biāo)阻礙了其在此類應(yīng)用中

2019-07-24 06:36:28

,但卻降低了輸入阻抗。 儀表放大器有那些主要技術(shù)指標(biāo)?設(shè)計儀表放大器的工程師需要考慮的主要性能指標(biāo)包括:電源電流、-3dB帶寬、共模抑制比(CMRR)、輸入失調(diào)電壓和失調(diào)電壓隨溫度的漂移以及輸入端

2018-10-17 15:06:47

voltage will be reject by IIA”s high CMRR. 請問ADI那種儀表放大器適合用在高精度,高輸入阻抗,高共模抑制比的生物醫(yī)學(xué)儀表? AD8220,它的輸入級為JFET

2018-11-19 09:34:53

儀表放大器AD8421和AD8429,在測量高頻小信號(10KHZ-1500KHZ范圍)哪一個棕合性能更優(yōu)秀一些?在共模抑制比,輸入輸出電壓噪聲,電壓漂移,動態(tài)范圍,壓擺率等方面,目前有沒有性能更好的儀表放大器?

2023-11-16 07:56:17

如圖所示,下面是一個交流耦合放大電路,在電路的差分輸入端輸入差模(100uV,10Hz)和共模信號(10V,10Hz),進(jìn)行電路的共模抑制比(CMRR)測試,測試發(fā)現(xiàn):

1、差分信號從INS+

2023-11-17 09:09:39

麻煩問一下,我想做檢測電流,儀表放大器的最大共模電壓該如何確定啊?我看到的都是共模抑制比。。希望得到解答。謝謝

2019-01-02 11:02:20

為何儀表放大器的PSRR及CMRR會隨增益的提高而改善?

2021-04-02 07:43:43

如圖所示,如何設(shè)計AD8221交流耦合電路能:1、降低噪聲,提高信噪比(SNR);2、提高儀表運放輸入阻抗;3、提高共模抑制比(CMRR)。

2018-08-06 06:55:10

環(huán)路輸出端的失調(diào)電壓。這是 CMRRB。 注意,總電源電壓保持不變,輸出保持在兩個電源的中間位置。CMRR 的計算方法如下:圖 8.這款測量 CMRR 的電路配置采用雙放大器環(huán)路。共模抑制比(自測試

2018-09-07 11:04:41

提高了速度,但卻降低了輸入阻抗。

儀表放大器有那些主要技術(shù)指標(biāo)?

設(shè)計儀表放大器的工程師需要考慮的主要性能指標(biāo)包括:電源電流、-3dB帶寬、共模抑制比(CMRR)、輸入失調(diào)電壓和失調(diào)電壓隨溫度

2023-11-23 06:31:17

共模抑制比(CMRR) 是指差分放大器對同時加到兩個輸入端上的共模信號的抑制能力。更確切地說,CMRR是產(chǎn)生特定輸出所需輸入的共模電壓與產(chǎn)生同樣輸出所需輸入的差分電壓的比值。

2010-07-05 16:00:55 75

75

具有高共模抑制比的儀器用放大器電路圖

2009-04-01 09:14:35 1006

1006

放大器的共模抑制比的定義

共模抑制比(CMRR)是指差分放大器對同時加到兩個輸入端上的共模信號的抑制能力。更確切地說,CMRR是產(chǎn)生特

2009-04-22 20:40:37 2179

2179 儀表放大器的特點和電路設(shè)計原理

儀表放大器的特點

高共模抑制比

共模

2010-03-10 16:54:40 3122

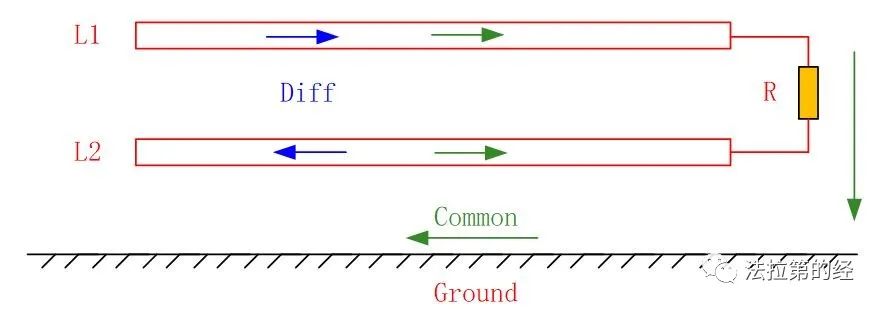

3122 用平衡輸入電路抑制共模噪聲的話筒放大器

電路的功能

OP放大器的共模抑制比很大,可

2010-04-26 17:23:34 3421

3421

共模抑制比和輸入阻抗高的儀表用差動放大電路

電路的功能

一個OP放大器構(gòu)成的高增益差

2010-04-27 16:16:13 3229

3229

本文針對傳統(tǒng)儀用放大電路的特點,介紹了一種高共模抑制比儀用放大電路,引入共模負(fù)反饋,大大提高了通用儀表放大器的共模抑制能力。

2012-02-02 14:32:34 118

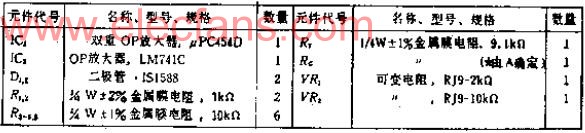

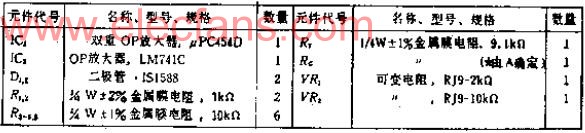

118 共模抑制比(CMMR)是一個指定參數(shù)的儀器儀表。LM4250是高性能放大器,具有很低的功率消耗。儀表放大器電路具有最大限度地CMMR校準(zhǔn)性能。

2012-03-14 10:19:25 2488

2488

回到儀表放大器的簡化模型(如圖 1 所示)中,我們可以再次回想起 PSRR 與 CMRR 都是輸入?yún)⒖紖?shù)。圖 1:儀表放大器的概念模型在更高的增益下,當(dāng)需要計算輸入時,可用輸入級增益除以第二級失調(diào)的變化:這里就是二級放大器概念模型不完備的地方。

2017-04-08 02:22:15 3122

3122

在這類應(yīng)用中,通常使用兩個或三個運算放大器的集成儀表放大器。盡管儀表放大器具有出色的共模抑制比(CMRR),但價格因素,性能指標(biāo)阻礙了其在此類應(yīng)用中的使用。

2017-12-06 10:41:02 8203

8203

電源抑制比( PSRR)和共模抑制比(CMRR)是用來設(shè)計差分放大器和表述其特性的兩個重要指標(biāo)。

2018-05-28 10:41:10 27

27 呢? 網(wǎng)絡(luò)變壓器

CMRR:在一個網(wǎng)絡(luò)系統(tǒng)中,為了說明差分放大電路抑制共模信號及放大差模信號的能力,常用共模抑制比作為一項技術(shù)指標(biāo)來衡量,其定義為放大器對差模信號的電壓放大倍數(shù)Aud與對共模信號的電壓

2019-02-25 17:55:54 1185

1185 在電子學(xué)中,差分放大器(或其他裝置)的共模抑制比(CMRR)是一個度量,用于量化裝置抑制共模信號的能力,即那些同時出現(xiàn)在兩個輸入端且同相出現(xiàn)的信號。一個理想的差分放大器將有無限的共模抑制比,但這在

2019-09-14 10:57:00 60598

60598

現(xiàn)代的電池電壓為3~3.6V,這就要求電路能在低壓下高效工作。本設(shè)計提出的一種交流耦合儀表放大器,具有很大的共模抑制比(CMRR)、很寬的直流輸入電壓容限以及一階高通特性。這些特性大多是由高增益第一

2020-07-21 14:47:51 1863

1863

現(xiàn)代的電池電壓為3~3.6V,這就要求電路能在低壓下高效工作。本設(shè)計提出的一種交流耦合儀表放大器,具有很大的共模抑制比(CMRR)、很寬的直流輸入電壓容限以及一階高通特性。這些特性大多是由高增益第一

2020-09-10 10:00:13 629

629

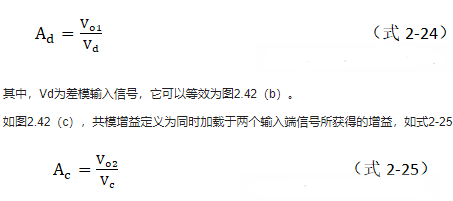

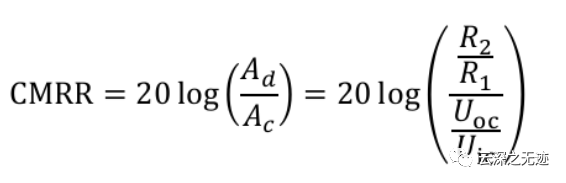

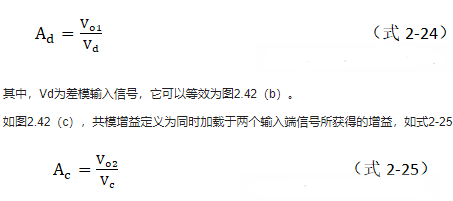

放大器的差模增益是電路所需要的增益,而共模增益將放大直流噪聲。共模抑制比(Common Mode Rejection Ratio,CMRR),定義為差模增益與共模增益的比值,如式2-26。

2020-10-22 17:51:53 3398

3398

如《放大器共模抑制比(CMRR)參數(shù)評估與電路共模抑制能力實例分析》中案例,由于電阻誤差導(dǎo)致電路共模抑制能力下降,是使用通用放大器組建差動放大電路的常見問題之一。工程師常常疑惑1%誤差的電阻

2020-10-31 09:42:35 3484

3484

MT-042:運算放大器共模抑制比(CMRR)

2021-03-21 08:57:14 13

13 通常直流精度要求較高,失調(diào)電壓,失調(diào)電流通常是我們關(guān)注的參數(shù),然而還有一個非常重要的參數(shù),CMRR,共模抑制比也會對儀表放大器的精度造成重要的影響。

共模抑制比,描述的是放大器共模電壓的變化導(dǎo)致

2021-11-10 09:37:56 1473

1473

并不是所有架構(gòu)造而平等。就像您不會選擇一個單一工具來建造一個房子一樣,您不應(yīng)該假設(shè)所有儀表放大器(INA)在所有應(yīng)用中都能發(fā)揮最佳效用。

共模抑制比(CMRR)和共模抑制(CMR)測量差分輸入

2021-12-10 10:27:43 1488

1488

在圖 1 中,放大器的電源抑制比 (PSRR) 隨放大器增益配置的升高而增加。這樣很容易讓人想到,在高增益下產(chǎn)生任何輸出偏移,都需要電源的明顯變化!但一定要記住:共模抑制比 (CMRR) 和 PSRR

2021-11-23 09:14:17 1195

1195

方法,在Allen書中都有相關(guān)的介紹。最近發(fā)覺對這些仿真電路的原理有點模糊(主要還是對于CMRR的仿真電路),在這里拿出來重新溫習(xí)一下下圖是共模抑制比仿真電路,通過ac小信號分析(兩個Vcm相同,都取 ac=1),分析Vout輸出的信號共模抑制比由電路分析看到: Vout=Adm?(V1?V2)+Ac

2022-01-05 14:22:58 5

5 理想情況下,差分放大器電路中的電阻應(yīng)仔細(xì)選擇,其比值應(yīng)相同 (R2/R1 = R4/R3)。這些比值有任何偏差都將導(dǎo)致不良的共模誤差。差分放大器抑制這種共模誤差的能力以共模抑制比(CMRR) 來表示。

2022-06-01 09:41:09 2487

2487 儀表放大器: CMRR,你偷走了我的精度

2022-11-01 08:27:14 1

1 處理抑制問題:儀表放大器的 PSRR 與 CMRR

2022-11-07 08:07:27 1

1 共模抑制比(CMRR)的概念是處理差分輸入電路時的基本概念,但它經(jīng)常被誤解。使用儀表放大器時,對電路中共模信號的影響有不正確的期望并不罕見。

2023-02-17 10:12:02 193

193

測量放大器的失調(diào)電壓、偏置電流參數(shù),可根據(jù)所設(shè)計的電路簡易調(diào)整就能完成測試。而共模抑制比參數(shù)的測試方法卻相對復(fù)雜,本篇分析幾種常被誤用的放大器共模抑制比測量方法的不足之處,以及提供一種有效測量共模抑制比電路以及提供仿真。

2023-02-22 14:33:45 1305

1305

號,幅度較小,源阻抗較高,并且共模電壓變化比較大。放大這些信號通常直流精度要求較高,失調(diào)電壓,失調(diào)電流通常是我們關(guān)注的參數(shù),然而還有一個非常重要的參數(shù),CMRR,共模抑制比也會對儀表放大器的精度造成重要的影響。

2023-04-06 10:22:43 965

965

儀表放大器(Instrumentation Amplifier,簡稱IA)是一種專門用于信號增益、濾波和隔離的放大器電路,其具有高輸入阻抗、高共模抑制比和良好的線性度等特點,因此在精密測量和數(shù)據(jù)采集等領(lǐng)域得到廣泛應(yīng)用。儀表放大器由三個運算放大器和若干個電阻組成,其構(gòu)成原理如下。

2023-06-26 09:29:18 848

848 儀表放大器共模抑制比怎么計算? 儀表放大器是一種性能較高的放大器,其主要功能是對信號進(jìn)行高精度的放大和測量,具有通用性,不僅可用于電子器件中,還可用于傳感器和儀表等領(lǐng)域。儀表放大器的共模抑制比是衡量

2023-09-05 17:39:18 1449

1449 帶恒流源的差分放大器如何提高共模抑制比的? 差分放大器是常見的電路設(shè)計,它可以提供高增益和高共模抑制比。但是,由于器件的不匹配和溫度變化等因素,共模電壓可能會出現(xiàn)偏移,使得差分電路的性能受到影響

2023-10-23 10:29:16 892

892 的值。 一、共模抑制比(CMRR) 共模抑制比是指放大器在相同輸入信號下,對于共模信號(兩個輸入端的電壓相等)的抑制能力和差模信號(兩

2023-10-29 11:45:48 2999

2999 同相比例放大器為什么對共模抑制比要求高?運放的共模抑制比如何仿真? 同相比例放大器是一種常見的放大電路,用于放大微弱信號。在應(yīng)用中,通常需要對放大的信號進(jìn)行差分測量,即對信號的差值進(jìn)行放大,而抑制

2024-01-26 14:42:55 237

237

電子發(fā)燒友App

電子發(fā)燒友App

評論