信號完整性問題是高速PCB設計者必需面對的問題。阻抗匹配、合理端接、正確拓撲結(jié)構(gòu)解決信號完整性問題的

2010-10-11 10:43:57 1941

1941

宏遠科技發(fā)展有限公司專家組成員.四、授課大綱 第一講 高速系統(tǒng)設計技術(shù)及面臨的挑戰(zhàn) 介紹信號完整性在硬件不同設計階段的工作;信號速率的提高對于系統(tǒng)設計的挑戰(zhàn)。 主要介紹當今國內(nèi)外各種互連設計及分析技術(shù)

2010-12-16 10:03:11

電阻的放置 高速PCB信號完整性仿真分析 信號完整性的電路板設計準則 基于信號完整性分析的高速數(shù)字PCB的設計方法 LVDS(低電壓差分信號)原理分析 阻抗匹配與史密斯(Smith)圓圖:基本原理

2008-12-25 09:49:59

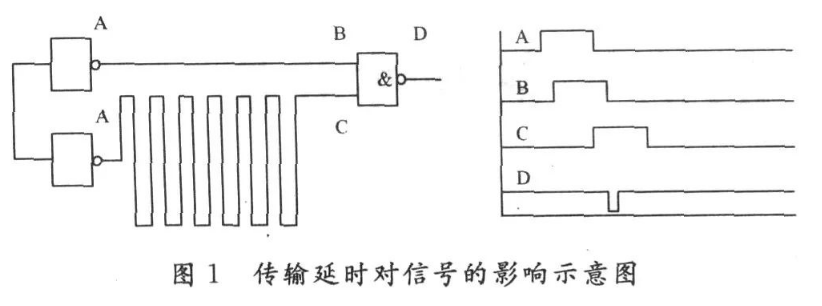

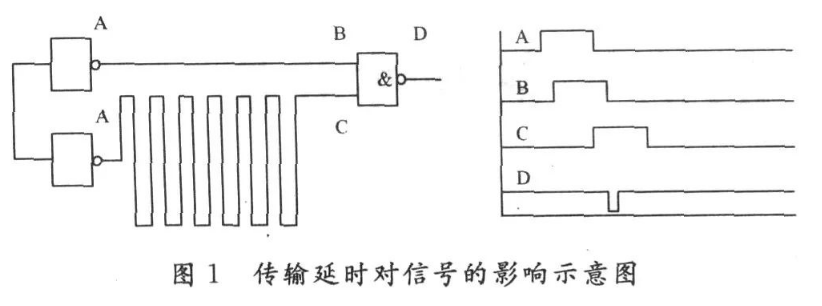

確定該電路具有較好的信號完整性。反之,當信號不能正常響應時,就出現(xiàn)了信號完整性問題。 高速PCB的信號完整性問題主要包括信號反射、串擾、信號延遲和時序錯誤。 · 反射:信號在傳輸線上傳輸時,當高速

2018-11-27 15:22:34

。參考:PCB設計中要考慮電源信號的完整性電源完整性| PCB設計資源...

2021-12-27 07:17:16

更好地學習高速PCB設計仿真知識。一、信號完整性與電源完整性分析信號完整性及電源完整性必看的書!電子工業(yè)出版社出版,伯格丁 (Eric Bogatin)著本書全面論述了信號完整性與電源完整性問題。主要

2019-11-13 18:26:40

在altium designer中想進行信號完整性的分析,可元件是自己造的,不知道仿真模型怎么建,哪些HC是啥意思也不知道

2012-11-01 21:43:04

中國電子電器可靠性工程協(xié)會關(guān)于組織召開“信號完整性仿真應用”高級研修班的邀請函各有關(guān)單位:為了幫助廣大從業(yè)人員詳細了解信號完整性(SI)和電源完整性(PI)的基本概念、分析方法和應用實例,幫助電子

2009-11-25 10:13:20

信號完整性資料

2015-09-18 17:26:36

信號完整性分析與設計信號完整性設計背景???什什么是信號完整D??信信號完整性設計內(nèi)è??典典型信號完整性問題與對2現(xiàn)在數(shù)字電路發(fā)展的趨ê??速速率越來越???芯芯片集成度越來越高£P(guān)C板板越來越

2009-09-12 10:20:03

PCB設計一些理論資料,信號完整性分析和PCB板設計提供一些指導

2018-10-19 18:58:49

Designer 6轉(zhuǎn)GERBER格式教程更多的PCB百科知識 >>>信號完整性分析基礎系列_共19節(jié).zip (8.32 MB )

2019-05-15 06:36:52

高速設計中的信號完整性和電源完整性分析

2021-04-06 07:10:59

LVDS,目前芯片接口物理標準的演變反映了集成電路工藝的不斷進步,同時也反映了高速信號傳輸要求的不斷提高。從版圖完整性的分析過程可知,只有結(jié)合了互聯(lián)結(jié)構(gòu)兩端負載特性的仿真結(jié)果才具有實際意義,而負載特性

2015-01-07 11:33:53

信號完整性與電源完整性的仿真分析與設計,不看肯定后悔

2021-05-12 06:40:35

本文主要介紹信號完整性是什么,信號完整性包括哪些內(nèi)容,什么時候需要注意信號完整性問題?

2021-01-25 06:51:11

完整性與哪些因素有關(guān)系;信號完整性會影響到產(chǎn)品的哪一個方面;等等。首推必看的第一本書就是Eric的《Signal Integrity-Simplified》即國內(nèi)現(xiàn)在號稱的藍皮書《信號完整性分析》,其次

2019-09-03 17:54:59

印制板)和系統(tǒng)的核心技術(shù)就是微波背景下的互連設計與信號完整性分析。全世界高速高密度電路的發(fā)展表明:互連正在取代器件,躍升為高速電路設計的主角。信號完整性分析是高速互連設計的支撐與保障。要想精通高速

2010-05-29 13:29:11

年,中國電子電器可靠性工程協(xié)會分期組織召開了4期“高速PCB與系統(tǒng)互連設計中信號完整性(SI)分析技術(shù)”高級研修班,課程的深度和廣度以及李教授精辟講解受到學員一致好評,應廣大客戶建議,中國電

2010-11-09 14:21:09

隨著半導體技術(shù)和深壓微米工藝的不斷發(fā)展,IC的開關(guān)速度目前已經(jīng)從幾十M H z增加到幾百M H z,甚至達到幾GH z。在高速PCB設計中,工程師經(jīng)常會碰到誤觸發(fā)、阻尼振蕩、過沖、欠沖、串擾等信號

2021-03-17 06:52:19

在高速PCB設計中,信號完整性問題對于電路設計的可靠性影響越來越明顯,為了解決信號完整性問題,設計工程師將更多的時間和精力投入到電路板設計的約束條件定義階段。通過在設計早期使用面向設計的信號分析

2018-09-10 16:37:21

,高速也就不成為“高速”。同樣的現(xiàn)象,發(fā)生在5G背板設計,6.5G背板設計,大家重復著過設計,驗證,掌握,簡化的過程。 SI領域的專家,多本信號完整性書籍的作者Eric有個描述: 世界上只有兩種硬件

2014-10-21 09:41:25

高速PCB設計的信號完整性問題 隨著器件工作頻率越來越高,高速PCB設計所面臨的信號完整性等問題成爲傳統(tǒng)設計的一個瓶頸,工程師在設計出完整的解決方案上面臨越來越大的挑戰(zhàn)。盡管有關(guān)的高速仿真工具

2012-10-17 15:59:48

高速信號的電源完整性分析在電路設計中,設計好一個高質(zhì)量的高速PCB板,應該從信號完整性(SI——Signal Integrity)和電源完整性 (PI——Power Integrity )兩個方面來

2012-08-02 22:18:58

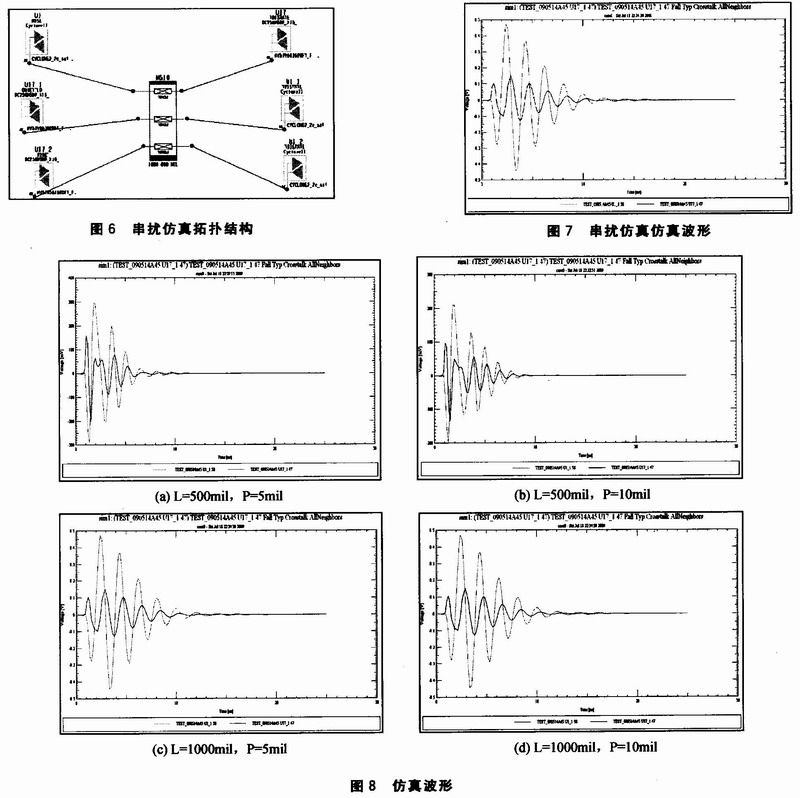

,具有工程應用實際參考價值。【關(guān)鍵詞】:高速電路;;仿真;;Cadence PCB SI軟件;;拓撲;;信號完整性【DOI】:CNKI:SUN:SYCS.0.2010-02-007【正文快照】:1引言現(xiàn)在

2010-05-06 08:57:45

高速電路信號完整性分析與設計—PCB設計多層印制板分層及堆疊中應遵徇的基本原則;電源平面應盡量靠近接地平面。布線層應安排與映象平面層相鄰。重要信號線應緊臨地層。[hide] [/hide][此貼子已經(jīng)被作者于2009-9-12 10:38:14編輯過]

2009-09-12 10:37:02

高速電路信號完整性分析與設計—信號完整性仿真仿真中有兩類信號可稱之為高速信號:高頻率的信號(>=50M)上升時間tr很短的信號:信號上升沿從20%~80%VCC的時間,一般是ns級或

2009-09-12 10:31:31

高速IC(芯片)、PCB(電路印制板)和系統(tǒng)的核心技術(shù)就是微波背景下的互連設計與信號完整性分析。全世界高速高密度電路的發(fā)展表明:互連正在取代器件,躍升為高速電路設計的主角。信號完整性分析是高速互連

2010-04-21 17:11:35

在高速電路設計中信號完整性分析由于系統(tǒng)時鐘頻率和上升時間的增長,信號完整性設計變得越來越重要。不幸的是,絕大多數(shù)數(shù)字電路設計者并沒意識到信號完整性問題的重要性,或者是直到設計的最后階段才初步認識到

2009-10-14 09:32:02

高速數(shù)字硬件電路設計中信號完整性在通常設計的影響是什么?高速電路設計中信號完整性面臨的挑戰(zhàn)有哪些?怎么處理?

2021-04-22 06:26:55

本文分析了高速電路設計中的信號完整性問題,提出了改善信號完整性的一些措施,并結(jié)合一個VGA視頻分配器系統(tǒng)的設計過程,具體分析了改善信號完整性的方法。

2021-06-03 06:22:05

本文分析了高速電路設計中的信號完整性問題,提出了改善信號完整性的一些措施,并結(jié)合一個VGA視頻分配器系統(tǒng)的設計過程,具體分析了改善信號完整性的方法。

2021-06-04 06:16:07

隨著通信系統(tǒng)中高速板設計復雜性的日益提高,依賴某一種特定的CAD工具已經(jīng)無法在可接受的精度范圍內(nèi)完成整個設計仿真。PCB設計工程師和信號完整性(SI)設計工程師需要采用各種仿真工具。除了價格、性能

2014-12-12 16:14:49

本文介紹高速高密度PCB設計的關(guān)鍵技術(shù)問題(信號完整性、電源完整性、EMC /EM I和熱分析)和相關(guān)EDA技術(shù)的新進展,討論高速高密度PCB設計的幾種重要趨勢。

2021-04-25 07:07:17

Designer的信號完整性分析工具可以支持包括差分對信號在內(nèi)的高速電路信號完整性分析功能。Altium Designer仿真參數(shù)通過一個簡單直觀的對話框進行配置,通過使用集成的波形觀察儀,實現(xiàn)圖形顯示仿真

2015-12-28 22:25:04

Cadenc高速電路設計SI PI 信號完整性電源完整性仿真視頻教程下載鏈接地址:鏈接:http://pan.baidu.com/s/1pJiPpzl密碼:3yjv

2015-07-30 21:44:10

`關(guān)于HyperLynx仿真的分析,當PCB發(fā)展到今天的時候,信號速度越來越快,信號的頻率越來越快,很多時候我們都無法去琢磨,在PCB板子設計好的時候我們都可以進行熱仿真,關(guān)鍵信號仿真,因為文件比較大,我們暫時無法上傳資料,有需要資料的人可以加QQ群:78297712 PCB高速信號完整性分析群78`

2015-05-17 17:03:52

哪位同學有Hyperlynx的對PCB信號完整性仿真的相關(guān)教程分享一下???跪求!!!

2016-06-15 10:16:02

VNA是如何測量高速器件的信號完整性(SI)?

2021-05-11 06:49:40

高速數(shù)字系統(tǒng)中,Altium designer 進行信號完整性分析技巧,

2017-03-20 15:43:02

hyperlynx Sigrity信號完整性仿真之高速理論視頻教程Allegro 平板電腦DDR3 PCB設計視頻教程鏈接:https://pan.baidu.com/s/1P1elXupWFQ8KNh-u7QhCDg 密碼:fc5q

2018-08-25 15:54:28

省部級獎勵10項。在IEEE Trans.上發(fā)表長文12篇;正式出版教材/專著/譯著12部。研究方向:高速電路設計與信號完整性分析,EDA技術(shù)及軟件研發(fā)。目錄第1章信號完整性分析概論 1.1信號完整性

2017-09-19 18:21:05

信號完整性領域,包括基本原理、測量技術(shù)和分析工具等方面舉辦過多期短期課程,目前為GigaTest實驗室首席技術(shù)主管。李玉山,西安電子科技大學教授,教育部“超高速電路設計與電磁兼容”重點實驗室學術(shù)委員會

2017-08-08 18:03:31

模型與布局、電源分配系統(tǒng)、電壓調(diào)節(jié)模塊、電源平面、單節(jié)點仿真、多節(jié)點仿真等電源完整性分析內(nèi)容。 目錄:序言前言目錄第1章 高速PCB設計知識第2章 仿真前的準備工作第3章 約束驅(qū)動布局第4章 約束驅(qū)動

2017-07-18 18:12:07

基于信號完整性分析的高速PCB仿真與設計,CAJ格式,需下載閱讀器查看。

2021-03-26 10:09:56

詳細流程)為了幫助大家更好學習Cadence SI仿真信號完整性、電源完整性設計,小編特地建立了高速PCB設計與仿真技術(shù)交流(微信群)。群里會不定期邀請講師分享,PCB設計直播,高速PCB設計、PI

2019-11-19 18:55:31

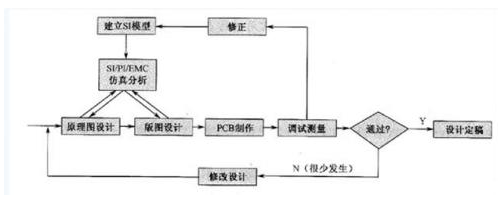

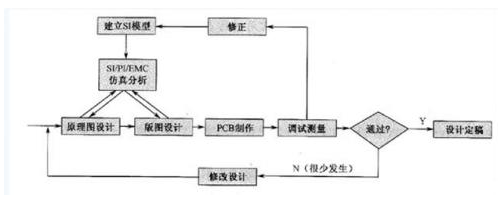

``【轉(zhuǎn)載】Allegro SI 高速信號完整性仿真連載之一(附詳細流程)高速PCB設計的流程為:傳統(tǒng)的PCB設計流程如下圖所示:而引入的Allegro PCB SI仿真工具后的設計流程改進為

2019-11-19 19:14:25

主辦單位:北京中鼎暢訊科技有限公司舉辦時間:2016年6月17-18日(2天)舉辦地點:北京主講老師:于爭博士 著名實戰(zhàn)型信號完整性設計專家課程簡介信號完整性是內(nèi)嵌于PCB設計中的一項必備內(nèi)容,無論

2016-05-05 14:26:26

基于信號完整性分析的PCB設計流程如圖所示。 主要包含以下步驟: 圖 基于信號完整性分析的高速PCB設計流程 (1)因為整個設計流程是基于信號完整性分析的,所以在進行PCB設計之前,必須建立

2018-09-03 11:18:54

,與信號本身的頻率相比,信號邊沿的諧波頻率更高,信號快速變化的跳變(上升沿與下降沿)引發(fā)了信號傳輸?shù)姆穷A期效果。這也是信號完整性問題的根源所在。因此,如何在高速PCB設計過程中充分考慮信號完整性因素,并

2015-01-07 11:30:40

業(yè)界中的一個熱門課題。基于信號完整性計算機分析的高速數(shù)字PCB板設計方法能有效地實現(xiàn)PCB設計的信號完整性。 1. 信號完整性問題概述 信號完整性(SI)是指信號在電路中以正確的時序和電壓作出響應

2018-08-29 16:28:48

業(yè)界中的一個熱門課題。基于信號完整性計算機分析的高速數(shù)字PCB板設計方法能有效地實現(xiàn)PCB設計的信號完整性。 1. 信號完整性問題概述 信號完整性(SI)是指信號在電路中以正確的時序和電壓作出響應

2008-06-14 09:14:27

完整性分析工具內(nèi)嵌在PCB編輯器中,提供一個便于使用的交互式仿真環(huán)境。在PCB編輯主界面中執(zhí)行菜單命令【Tools】/【Signal Integrity. . . 】,會出現(xiàn)信號完整性仿真器窗口,如圖2

2018-08-27 16:13:55

常值得注意的問題。本文首先介紹了PCB信號完整性的問題,其次闡述了PCB信號完整性的步驟,最后介紹了如何確保PCB設計信號完整性的方法。PCB信號完整性的問題包括:PCB的信號完整性問題主要包括信號

2018-07-31 17:12:43

高速數(shù)字PCB設計信號完整性解決方法

2021-03-29 08:12:25

潛在風險,仿真及設計控制等多種手段并用。總之,系統(tǒng)化信號完整性設計方法,是設計PCB而不是簡單仿真PCB。文章轉(zhuǎn)載于博士信號完整性網(wǎng)站http://www.sig007.cn關(guān)注于博士信號完整性微信公眾號 zdcx007了解更多PCB設計知識

2017-06-23 11:52:11

完整性的旅程中,以上為大家系統(tǒng)地梳理了其在硬件設計中的核心地位。從總線協(xié)議到PCB設計,從材料選擇到高速互連器件的理解,每一個環(huán)節(jié)都彰顯著信號完整性的重要性。而測試測量與仿真軟件的應用,更是為信號完整性

2024-03-05 17:16:39

Cadence電源完整性仿真軟件可以分析電源噪聲和高速電路中的電源分配系統(tǒng)設計。包含一種用于設計和優(yōu)化高速基板設計中電源分配系統(tǒng)的頻域分析方法(求解傳輸阻抗)。它讓用戶可以迅速而輕松地進行“變化

2020-07-07 15:53:56

PCB設計中的電源信號完整性的考慮因素有哪些?

2021-04-23 06:54:29

、在PCB設計過程中,使用仿真軟件評估具體走線,觀察信號質(zhì)量能不能滿足要求,這個仿真過程本身非常簡單,關(guān)鍵是要理解信號完整性的原理知識,并用來指導。PCB設計技巧3、做PCB的過程中,一定要進行風險控制

2017-02-28 16:13:27

摘要! 介紹了高速+,& 設計中的信號完整性概念以及破壞信號完整性的原因!從理論和計算的層面上分析了高速電路設計中反射和串擾的形成原因!并介紹了-&-. 仿真"關(guān)鍵詞!

2008-10-15 08:15:02 0

0 本文介紹了一種基于信號完整性計算機分析的高速數(shù)字信號 PCB板的設計方法。在這種設計方法中,首先將對所有的高速數(shù)字信號建立起PCB板級的信號傳輸模型,然后通過對信號完

2009-04-25 16:49:13 37

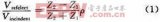

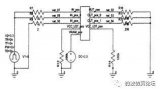

37 高速PCB設計中的串擾分析與控制:物理分析與驗證對于確保復雜、高速PCB板級和系統(tǒng)級設計的成功起到越來越關(guān)鍵的作用。本文將介紹在信號完整性分析中抑制和改善信號串擾的

2009-06-14 10:02:38 0

0 高速電路信號完整性分析與設計—信號完整性仿真:仿真信號仿真中有兩類信號可稱之為高速信號:高頻率的信號(>=50M)上升時間tr很短的信號:信號上

2009-10-06 11:19:50 0

0 針對高速數(shù)字電路印刷電路板的板級信號完整性, 分析了IBIS 模型在板級信號完整性分析中的作用。利用ADS 仿真軟件, 采用電磁仿真建模和電路瞬態(tài)仿真測試了某個實際電路版

2010-08-23 17:18:04 37

37 討論了高速PCB 設計中涉及的定時、反射、串擾、振鈴等信號完整性( SI)問題,結(jié)合CA2DENCE公司提供的高速PCB設計工具Specctraquest和Sigxp,對一采樣率為125MHz的AD /DAC印制板進行了仿真和分析,根

2011-11-21 16:43:23 0

0 現(xiàn)在的高速電路設計已經(jīng)達到GHz的水平,高速PCB設計要求從三維設計理論出發(fā)對過孔、封裝和布線進行綜合設計來解決信號完整性問題。高速PCB設計要求中國工程師必須具備電磁場的理

2011-11-30 11:11:31 0

0 文中以基于FPGA設計的高速信號下載器為例,從LVDS的PCB設計,約束設置和信號完整性仿真等多方面研究LVDS信號的實現(xiàn)。

2012-04-20 10:37:02 58

58 在電路設計中,設計好一個高質(zhì)量的高速PCB板,應該從信號完整性(SISignal Integrity)和電源完整性 (PIPower Integrity )兩個方面來考慮。盡管從信號完整性上表現(xiàn)出來的結(jié)果較為直接,但是信

2012-05-29 13:51:26 2498

2498 信號完整性與PCB設計+Douglas+Brooks。

2015-08-28 18:12:51 491

491 信號完整性分析及其在高速PCB設計中的應用,教你如何設計高速電路。

2016-04-06 17:29:45 15

15 10129@52RD_信號完整性與電源完整性的仿真分析與設計

2016-12-14 21:27:39 0

0 描述了高速PCB電路板信號完整性設計方法。 介紹了信號完整性基本理論, 重點討論了如何采用高速PCB設計方法保證高速數(shù)采模塊的信號完整性

2017-11-08 16:55:13 0

0 基于信號完整性分析的PCB設計流程如圖所示。 主要包含以下步驟: 圖基于信號完整性分析的高速PCB設計流程 (1)因為整個設計流程是基于信號完整性分析的,所以在進行PCB設計之前,必須建立或獲取高速

2017-12-04 10:46:30 0

0 信號完整性問題已成為當今高速PCB設計的一大挑戰(zhàn),傳統(tǒng)的設計方法無法實現(xiàn)較高的一次設計成功率,急需基于EDA軟件進行SI仿真輔助設計的方法以解決此問題。

2018-02-06 18:44:43 4138

4138

隨著半導體工藝的發(fā)展,在電子系統(tǒng)高功耗、高密度、高速、大電流和低電壓的發(fā)展趨勢下,高速 PCB設計領域 中的電源完整性 問題變得 日趨嚴重。本文研究 了高速 PCB設計中出現(xiàn)的電源完整性問題 ,并對其進行 了仿真分析。

2018-02-07 08:32:47 8319

8319

高速 PCB 信號完整性仿真分析.pdf

2018-05-07 14:52:31 48

48 本文首先介紹了PCB信號完整性的問題,其次闡述了PCB信號完整性的步驟,最后介紹了如何確保PCB設計信號完整性的方法。

2018-05-23 15:08:32 10976

10976 周一的時候給大家分享了一份文檔,下載量達到了1000來次,正好,下周我們給大家做一次關(guān)于高速PCB仿真技術(shù)的分享,包括電源完整性和信號完整性、過孔仿真。

2018-09-12 16:52:01 5737

5737 針對 DDR2高速電路中存在的信號完整性問題進行了分析,提出了PCB設計要點。并以單個DDR2存儲器與控制器間的 PCB設計為例,對如何在減少仿真工作的情況下成功完成一個可用的設計進行了論述。

2019-03-04 08:00:00 0

0 借助功能強大的Cadence公司SPEECTRAQuest仿真軟件,利用IBIS模型,對高速信號進行信號完整性仿真分析是一種高效可行的分析方法,可以發(fā)現(xiàn)信號完整性問題,根據(jù)仿真結(jié)果在信號完整性相關(guān)問題上做出優(yōu)化的設計,從而達到提高設計質(zhì)量,縮短設計周期的目的。

2019-05-20 15:25:37 1098

1098

(1)因為整個設計流程是基于信號完整性分析的,所以在進行PCB設計之前,必須建立或獲取高速數(shù)字信號傳輸系統(tǒng)各個環(huán)節(jié)的信號完整性模型。

(2)在設計原理圖過程中,利用信號完整性模型對關(guān)鍵網(wǎng)絡進行信號完整性預分析,依據(jù)分析結(jié)果來選擇合適的元器件參數(shù)和電路拓撲結(jié)構(gòu)等。

2019-10-11 14:52:33 2023

2023

發(fā)生的選擇。借助當今的現(xiàn)代PCB,了解抗墊對信號完整性的影響非常重要 。 防墊和信號完整性 當涉及信號完整性時,請仔細閱讀組件制造商的應用說明,并始終驗證您從容易理解的概念中看到的內(nèi)容。如果您查看某些組件的應用筆記,他們將建議

2020-12-15 15:47:04 1316

1316

信號完整性問題與PCB設計說明。

2021-03-23 10:57:06 0

0 總結(jié)了在高速PCB板設計中信號完整性產(chǎn)生的原因、抑制和改善的方法。介紹了使用IBS模型的仿真步驟以及使用 CADENCE公司的 Allegro SPB軟件,支持IBIS模型對反射和串擾的仿真,驗證了其改善后的效果,可以直觀地看到PCB設計是否滿足設計要求,進而指導和驗證高速PCB的設計。

2021-05-27 13:59:31 20

20 信號完整性與電源完整性的仿真(5V40A開關(guān)電源技術(shù)參數(shù))-信號完整性與電源完整性的仿真分析與設計!!!

2021-09-29 12:11:21 89

89 介紹了高速PCB設計中的信號完整性概念以及破壞信號完整性的原因,從理論和計算的層面上分析了高速電路設計中反射和串擾的形成原因,并介紹了IBIS仿真。

2021-12-17 13:47:07 1

1 高速電路信號完整性分析與設計—信號完整性仿真

2022-02-10 17:29:52 0

0 高速電路信號完整性分析與設計—PCB設計1

2022-02-10 17:31:51 0

0 高速電路信號完整性分析與設計—PCB設計2

2022-02-10 17:34:49 0

0 本文首先介紹了傳輸線理論,詳細分析了高速PCB設計中的信號完整性問題,包括反射、串擾、同步開關(guān)噪聲等,然后利用Mentor Graphics公司的EDA軟件HyperLynx對給定電路模型進行了反射

2022-07-01 10:53:00 0

0 本文首先介紹了PCB信號完整性的問題,其次闡述了PCB信號完整性的步驟,最后介紹了如何確保PCB設計信號完整性的方法。

2022-12-22 11:53:39 771

771 PCB級的信號完整性仿真

2022-12-30 09:20:36 5

5 高速電路板設計與仿真--信號與電源完整性分析

2022-12-30 09:22:20 82

82 信號傳輸并非嚴格針對網(wǎng)絡設計師,您的PCB設計可能會遇到相同類型的問題。由于您無需費力地擺弄耳朵,因此防止電源完整性和信號完整性問題對于您的PCB設計流暢且無靜電至關(guān)重要。

2023-11-08 17:25:01 344

344

PCB上信號速度高、端接元件的布局不正確或高速信號的錯誤布線都會引起信號完整性問題,從而可能使系統(tǒng)輸出不正確的數(shù)據(jù)、電路工作不正常甚至完全不工作,如何在PCB板的設計過程中充分考慮信號完整性的因素,并采取有效的控制措施,已經(jīng)成為當今PCB設計業(yè)界中的一個熱門話題。

2024-01-11 15:28:00 86

86

電子發(fā)燒友App

電子發(fā)燒友App

評論