高速電路PCB電源布線技巧

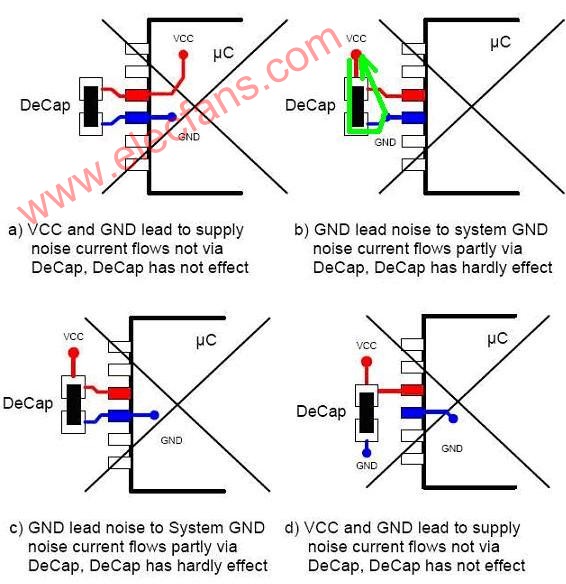

PCB設(shè)計(jì)來(lái)說(shuō)電源處理好壞直接關(guān)系到整個(gè)電路板的性能。下面我們分析一下高速電路PCB板的電源布線需要注意的地方和技

2010-03-21 18:29:39 2743

2743

現(xiàn)在,著名媒體TomsHardware也拿到真片送上測(cè)試,他們也是黑了一把(功耗和發(fā)熱不理想),只是尚受限保密期的Intel公關(guān)和技術(shù)人員拒絕評(píng)論。

2016-12-01 13:53:34 18317

18317 PCB平面變壓器可由獨(dú)立的標(biāo)準(zhǔn)疊層電路或小型多層PCB板組件構(gòu)成,或者集成到電源多層PCB板內(nèi)。本文詳細(xì)介紹了PCB平面變壓器設(shè)計(jì)及應(yīng)用舉例。

2018-02-08 09:45:13 84464

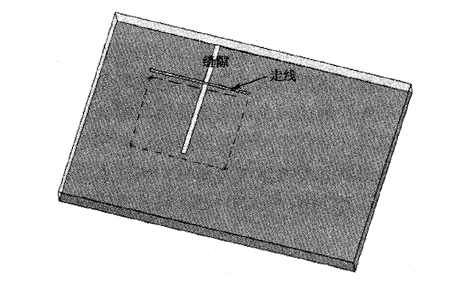

84464 很多人對(duì)于PCB走線的參考平面感到迷惑,經(jīng)常有人問(wèn):對(duì)于內(nèi)層走線,如果走線一側(cè)是VCC,另一側(cè)是GND,那么哪個(gè)是參考平面?

2022-09-09 13:05:47 4185

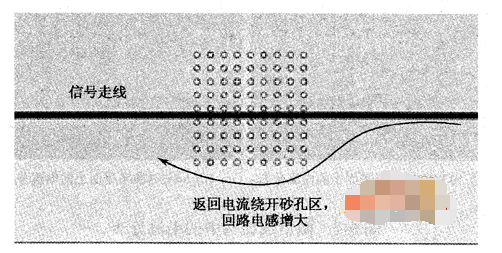

4185 如果參考平面上有間隙,然后信號(hào)穿過(guò)該間隙,會(huì)在PCB中產(chǎn)生很多不良性能。

2022-11-16 14:16:23 521

521 在電路PCB設(shè)計(jì)中,地平面設(shè)計(jì)是一個(gè)重要的組成部分,PCB地平面的設(shè)計(jì)不僅關(guān)乎到電子產(chǎn)品的工作性能,而且對(duì)于EMC方面的影響也是息息相關(guān)。

2024-03-19 14:12:46 767

767

快速理解高速layout設(shè)計(jì) ? 在高速PCB電路的布線中需要注意些什么?

2021-03-05 06:00:06

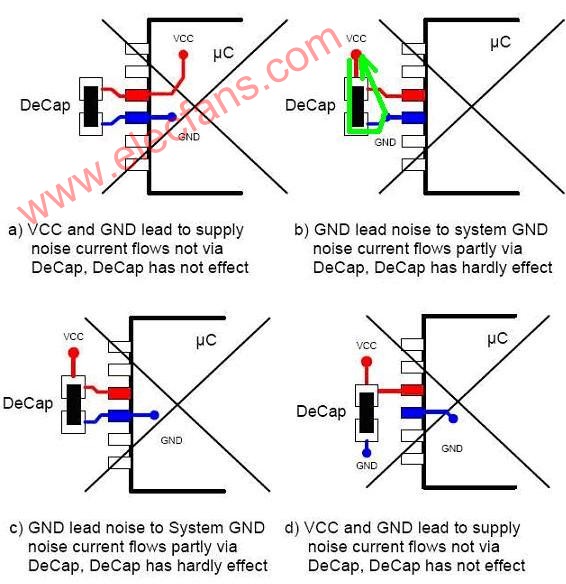

PCB PDN design guidelines (PCB電源完整性設(shè)計(jì)指導(dǎo)) ------PCB平面圖指南在開(kāi)始進(jìn)行PCB布局之前,必須注意正確放置組件。 較低等級(jí)的模擬,高速數(shù)字和噪聲電路

2021-12-28 07:34:07

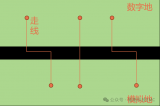

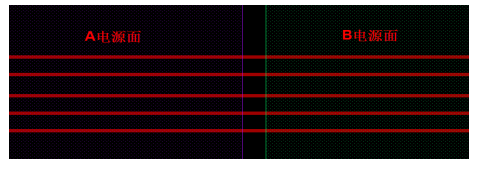

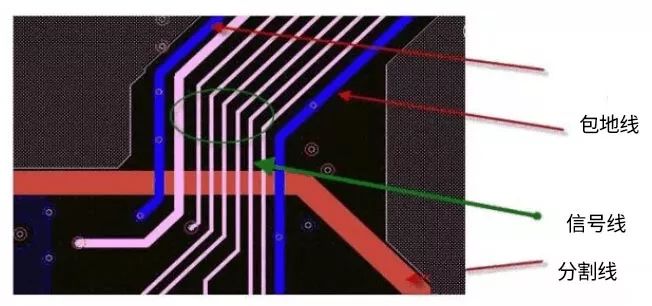

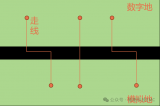

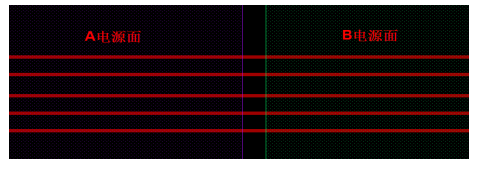

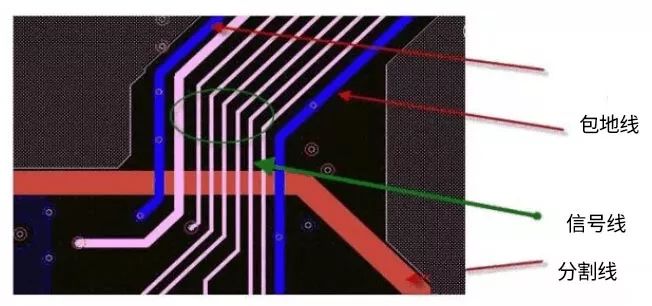

在 PCB 設(shè)計(jì)過(guò)程中,由于平面的分割,可能會(huì)導(dǎo)致信號(hào)參考平面不連續(xù),對(duì)于低低頻信號(hào),可能沒(méi)什么關(guān)系,而在高頻數(shù)字系統(tǒng)中,高頻信號(hào)以參考平面作返回路徑,即回流路徑,如果參考?面不連續(xù),信號(hào)跨分割

2016-10-09 13:10:37

本文討論了適當(dāng)接地技術(shù)在PCB設(shè)計(jì)中的重要性。 我不否認(rèn)可以設(shè)計(jì)沒(méi)有接地平面的PCB,并且在許多情況下,您可以通過(guò)這種方式創(chuàng)建功能齊全的電路板(或者至少在有利的環(huán)境中運(yùn)行時(shí)它將完全正常工作)。但是

2018-07-14 12:31:53

知道,必須使用傳輸線來(lái)分析PCB上的信號(hào)傳輸,才能解釋高速電路中出現(xiàn)的各種現(xiàn)象。最簡(jiǎn)單的傳輸線包括兩個(gè)基本要素:信號(hào)路徑、參考路徑(也稱為返回路徑)。信號(hào)在傳輸線上是以電磁波的形式傳輸?shù)模瑐鬏斁€的兩個(gè)

2014-11-05 09:24:09

PCB畫(huà)板總是畫(huà)不理想,該怎么辦?有沒(méi)有一些PCB布局心得,可以分享?

2019-09-12 13:51:32

電源平面的處理,在PCB設(shè)計(jì)中占有很重要的地位。在一個(gè)完整的設(shè)計(jì)項(xiàng)目中,通常電源的處理決定項(xiàng)目的30%-50%的成功率。本次給大家介紹在PCB設(shè)計(jì)過(guò)程中電源平面處理應(yīng)該考慮的基本要素。

2019-09-11 11:52:19

電流將會(huì)遭遇不理想的返回路徑,使返回路徑上出現(xiàn)縫隙。對(duì)于高速信號(hào),這種不合理的返回路徑設(shè)計(jì)可能會(huì)帶來(lái)嚴(yán)重的問(wèn)題。所以,高速信號(hào)布線應(yīng)該遠(yuǎn)離多電源參考平面。 · 多個(gè)地敷銅層可以有效地減小PCB的阻抗

2018-11-27 15:14:59

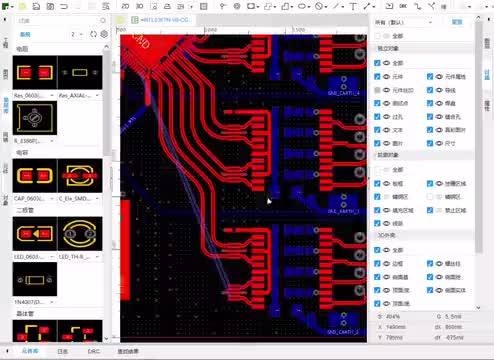

環(huán)繞。 原因:避免信號(hào)直接耦合,影響信號(hào)質(zhì)量。15、多種模塊電路在同一PCB 上放臵時(shí),數(shù)字電路與模擬電路、高速與低速電路應(yīng)分開(kāi)布局。 原因:避免數(shù)字電路、模擬電路、高速電路以及低速電路之間的互相干擾。16、當(dāng)

2022-04-18 15:22:08

的設(shè)計(jì)常常注意電路板的視覺(jué)效果,現(xiàn)在不一樣了。自動(dòng)設(shè)計(jì)的電路板不比手動(dòng)設(shè)計(jì)的美觀,但在電子特性上能滿足規(guī)定的要求,而且設(shè)計(jì)的完整性能得到保證。二:高速PCB設(shè)計(jì)解決EMI問(wèn)題的九大規(guī)則隨著信號(hào)上升沿

2021-03-31 06:00:00

PCB(印制電路板)布線在高速電路中具有關(guān)鍵作用,那么高速PCB的布線需要考慮哪些事項(xiàng)呢? 這個(gè)問(wèn)題大家考慮過(guò)嗎?

2019-08-02 06:46:56

高速設(shè)計(jì)已成為愈來(lái)愈多 PCB 設(shè)計(jì)人員關(guān)切的重點(diǎn)。在進(jìn)行高速 PCB 設(shè)計(jì)時(shí),每位工程師都應(yīng)重視其信號(hào)完整性,并且需時(shí)常考慮其信號(hào)電路的回流路徑,因?yàn)椴涣嫉幕亓髀窂饺菀讓?dǎo)致噪聲耦合等信號(hào)完整性

2021-02-05 07:00:00

高速PCB設(shè)計(jì)中常規(guī)PCB布線,有以下基本要求:(1)QFP、SOP等封裝的矩形焊盤(pán)出線,應(yīng)從PIN中心引出(一般采用鋪shape)(2)布線到板邊的距離不小于20MIL。(3)金屬外殼器件下

2017-02-16 15:06:01

` 本帖最后由 飛翔的烏龜005 于 2017-2-10 10:43 編輯

高速PCB設(shè)計(jì)中常規(guī)PCB布線,有以下基本要求:(1)QFP、SOP等封裝的矩形焊盤(pán)出線,應(yīng)從PIN中心引出(一般采用

2017-02-10 10:42:11

的平面層,回流路徑分布在信號(hào)周圍各個(gè)地和電源上,仿真時(shí)需要使用3D場(chǎng)提取工具分析,這時(shí)候打彎布線和過(guò)孔的回流需要具體分析;高速數(shù)字電路分析一般只處理有完整平面層的多層PCB,使用2D場(chǎng)提取分析,只考慮在

2012-10-17 15:59:48

詳細(xì)介紹。 ˉˉˉˉ理想返回路徑 ˉˉˉˉ實(shí)際返回路徑 圖1返回路徑上存在縫隙 電路中不可避免會(huì)用到一些直插式的元件,如BGA封裝,必然會(huì)在PCB上形成許多貫穿整個(gè)電路板的通孔。過(guò)多、過(guò)密的通孔

2018-11-27 15:23:28

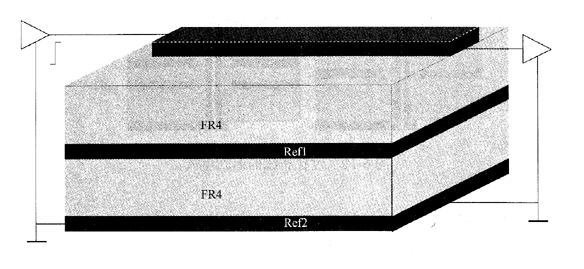

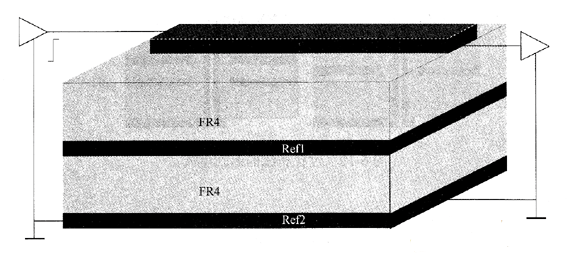

近的參考平面所構(gòu)成的傳輸線的特性阻抗,而與信號(hào)源返回端實(shí)際連接在哪個(gè)平面無(wú)關(guān)。同時(shí),為了最大限度地排除金屬平面間阻抗的影響,要盡量減小平面間介質(zhì)的厚度。 圖2多參考平面的返回電流路徑 在多層PCB中

2018-11-27 15:17:09

`高速電路PCB設(shè)計(jì)與EMC技術(shù)分析`

2017-09-21 21:31:03

,工程師希望能在PC平臺(tái)上用更好的工具完成復(fù)雜的高性能的設(shè)計(jì)。由此,我們不難看出,PCB板設(shè)計(jì)有以下三種趨勢(shì):高速數(shù)字電路(即高時(shí)鐘頻率及快速邊沿速率)的設(shè)計(jì)成為主流。 產(chǎn)品小型化及高性能必須面對(duì)在同一

2014-04-17 21:15:29

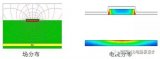

比較小,比較亮,由此說(shuō)明頻率越高,電流分布越集中。 如果返回路徑不理想,就無(wú)法保證如圖2所示的返回電流分布,比如參考平面上有一道裂縫(這種情況是經(jīng)常遇到的,因?yàn)閮?nèi)電層有時(shí)候會(huì)分配給多個(gè)電源或地網(wǎng)絡(luò)

2018-11-23 16:54:41

高速電路信號(hào)完整性分析與設(shè)計(jì)—PCB設(shè)計(jì)多層印制板分層及堆疊中應(yīng)遵徇的基本原則;電源平面應(yīng)盡量靠近接地平面。布線層應(yīng)安排與映象平面層相鄰。重要信號(hào)線應(yīng)緊臨地層。[hide] [/hide][此貼子已經(jīng)被作者于2009-9-12 10:38:14編輯過(guò)]

2009-09-12 10:37:02

耦合到各敏感源器件,同時(shí)電流環(huán)還會(huì)耦合進(jìn)外部產(chǎn)生的各類干擾,影響正常的工作系統(tǒng)。減小差模干擾的主要方法是布線時(shí)盡量減短走線長(zhǎng)度, 減小信號(hào)環(huán)路面積。 2.2 PCB電路板上干擾源產(chǎn)生方式 高速

2018-09-12 15:01:56

高速電路設(shè)計(jì)學(xué)習(xí) 一、PCB設(shè)計(jì)時(shí)高速信號(hào)和低速信號(hào)區(qū)分 在高速PCB電路設(shè)計(jì)過(guò)程中,經(jīng)常會(huì)遇到信號(hào)完整性問(wèn)題,導(dǎo)致信號(hào)傳輸質(zhì)量不佳甚至出錯(cuò)。那么如何區(qū)分高速信號(hào)和普通信號(hào)呢?很多人覺(jué)得信號(hào)頻率高

2020-12-21 09:23:34

什么是傳輸線效應(yīng)?高速DSPs的PCB電路板該怎樣去設(shè)計(jì)?

2021-04-25 06:27:07

摘要隨著現(xiàn)代總線接口頻率越來(lái)越高,必須謹(jǐn)慎設(shè)計(jì)印刷電路板(PCB)的布局,以確保解決方案的可靠性。內(nèi)容1 引言.................21.1 范圍

2023-04-14 15:47:37

印制電路板(PCB)布線在高速電路中具有關(guān)鍵的作用,但它往往是電路設(shè)計(jì)過(guò)程的最后幾個(gè)步驟之一。高速PCB布線有很多方面的問(wèn)題,關(guān)于這個(gè)題目已有人撰寫(xiě)了大量的文獻(xiàn)。本文主要從實(shí)踐的角度來(lái)探討高速電路

2019-02-27 10:19:33

上次沒(méi)有上傳設(shè)計(jì)電路,其實(shí)設(shè)計(jì)就是按照參考電路來(lái)的,但是接入到PCB中由于7、8腳的問(wèn)題就會(huì)導(dǎo)致整個(gè)PCB電源平面和地平面的短接,求解決辦法,如果是中間的exposed paddle能解決這個(gè)問(wèn)題 麻煩詳細(xì)指點(diǎn)一下

2023-11-24 06:23:04

PCB上的信號(hào)傳輸,才能解釋高速電路中出現(xiàn)的各種現(xiàn)象。最簡(jiǎn)單的傳輸線包括兩個(gè)基本要素:信號(hào)路徑、參考路徑(也稱為返回路徑)。信號(hào)在傳輸線上是以電磁波的形式傳輸?shù)模瑐鬏斁€的兩個(gè)基本要素構(gòu)成了電磁波傳輸

2014-11-17 10:07:29

寄生電容)的功能。雖然使用接地平面有許多好處,但是在實(shí)現(xiàn)時(shí)也必須小心,因?yàn)樗鼘?duì)能夠做的和不能夠做的都有一些限制。理想情況下,PCB有一層應(yīng)該專門(mén)用作接地平面。這樣當(dāng)整個(gè)平面不被破壞時(shí)才會(huì)產(chǎn)生最好的結(jié)果

2018-11-01 12:36:45

學(xué)習(xí)進(jìn)步。寄生效應(yīng)所謂寄生效應(yīng)就是那些溜進(jìn)你的PCB并在電路中大施破壞、令人頭痛、原因不明的小故障。它們就是滲入高速電路中隱藏的寄生電容和寄生電感。其中包括由封裝引腳和印制線過(guò)長(zhǎng)形成的寄生電感;焊盤(pán)到

2018-10-19 13:46:56

15:多種模塊電路在同一 PCB 上放臵時(shí),數(shù)字電路與模擬電路、高速與低速電路應(yīng)分開(kāi)布局。原因:避免數(shù)字電路、模擬電路、高速電路以及低速電路之間的互相干擾。

2018-11-23 16:21:49

做了一個(gè)三角波生成器,但是前一段的方波生成不理想,導(dǎo)致三角波的數(shù)據(jù)差了點(diǎn),

2019-11-12 15:21:12

我們經(jīng)常在教科書(shū)或者原廠的PCB Design Guide里看到一些關(guān)于高頻高速信號(hào)的設(shè)計(jì)原則,其中就包括在PCB電路板的邊緣不要走高速信號(hào)線,而對(duì)于板載PCB天線的設(shè)計(jì)來(lái)說(shuō),又建議天線要盡量靠近

2020-03-30 08:00:00

高速設(shè)計(jì)往往易被忽視或者相當(dāng)重要。系統(tǒng)電路板布局已成為設(shè)計(jì)本身的一個(gè)主要組成部分,因此,我們必須了解影響高速信號(hào)鏈路設(shè)計(jì)性能的機(jī)制。 盡管身為工程師,但我們也很可能"制造"

2018-11-21 11:02:34

號(hào),高頻信號(hào)等關(guān)鍵信號(hào)的下面設(shè)計(jì)地線層,這樣信號(hào)環(huán)路的路徑最短,輻射最小。高速電路設(shè)計(jì)過(guò)程中必須考慮如何處理電源的輻射和對(duì)整個(gè)系統(tǒng)的干擾。一般情況要使電源層平面的面積小于地平面的面積,這樣可以對(duì)電源起屏蔽

2022-12-08 11:49:11

電流總是在環(huán)路中流動(dòng),電路中任意的信號(hào)都以一個(gè)閉合回路的形式存在。對(duì)于高頻信號(hào)傳輸,實(shí)際上是對(duì)傳輸線與直流層之間包夾的介質(zhì)電容充電的過(guò)程。 2回流的影響 數(shù)字電路通常借助于地和電源平面來(lái)完成回流

2020-08-01 17:30:00

。減小差模干擾的主要方法是布線時(shí)盡量減短走線長(zhǎng)度, 減小信號(hào)環(huán)路面積。2.2 PCB電路板上干擾源產(chǎn)生方式高速數(shù)字電路各類干擾的主要產(chǎn)生原因是由電源自身固有噪聲頻率及外部線路上各類變化的di/dt

2011-07-16 11:50:08

印刷電路板的映像平面一個(gè)映像平面(image plane)是一層銅質(zhì)導(dǎo)體(或其它導(dǎo)體),它位于一個(gè)印刷電路板(PCB)里面。它可能是一個(gè)電壓平面,或鄰近一個(gè)電路或訊號(hào)路由層(signal

2009-05-15 11:58:33

高速PCB設(shè)計(jì)中常規(guī)PCB布線,有以下基本要求:(1)QFP、SOP等封裝的矩形焊盤(pán)出線,應(yīng)從PIN中心引出(一般采用鋪shape)(2)布線到板邊的距離不小于20MIL。(3)金屬外殼器件下

2017-01-23 09:36:13

1 引言 隨著人們對(duì)通信需求的不斷提高,要求信號(hào)的傳輸和處理的速度越來(lái)越快.相應(yīng)的高速PCB的應(yīng)用也越來(lái)越廣,設(shè)計(jì)也越來(lái)越復(fù)雜.高速電路有兩個(gè)方面的含義:一是頻率高,通常認(rèn)為數(shù)字電路的頻率達(dá)到

2018-11-22 16:03:30

1 引言 人們對(duì)于通信的要去總是朝著“快”的方向發(fā)展,要求信號(hào)的傳輸和處理的速度越來(lái)越快,相應(yīng)的,高速PCB的應(yīng)用也越來(lái)越廣。高速電路有兩個(gè)方面的含義:一是頻率高,通常認(rèn)為數(shù)字電路的頻率達(dá)到或是

2018-09-12 15:16:15

我們經(jīng)常在教科書(shū)或者原廠的PCB Design Guide里看到一些關(guān)于高頻高速信號(hào)的設(shè)計(jì)原則,其中就包括在PCB電路板的邊緣不要走高速信號(hào)線,而對(duì)于板載PCB天線的設(shè)計(jì)來(lái)說(shuō),又建議天線要盡量靠近

2019-11-09 07:00:00

如何設(shè)計(jì)pcb板的高速電路,需要考慮哪些因素?

2021-04-21 06:02:33

印刷電路板(PCB)布線在高速電路中具有關(guān)鍵的作用,但它往往只是電路設(shè)計(jì)過(guò)程的最后幾個(gè)步驟之一。高速PCB布線有很多方面的問(wèn)題,關(guān)于這個(gè)主題已有大量的文獻(xiàn)可供參考。本文主要從實(shí)踐的角度來(lái)探討高速電路的布線

2018-10-12 10:22:31

耦合強(qiáng),那一種就成為主要的回流通路。 在PCB 電路設(shè)計(jì)中,一般差分走線之間的耦合較小,往往只占10~20%的耦合度,更多的還是對(duì)地的耦合,所以差分走線的主要回流路徑還是存在于地平面。當(dāng)?shù)?b class="flag-6" style="color: red">平面發(fā)生不

2023-04-18 14:52:28

作為一名合格的、優(yōu)秀的PCB設(shè)計(jì)工程師,我們不僅要掌握高速PCB設(shè)計(jì)技能,還需要對(duì)其他相關(guān)知識(shí)有所了解,比如高速PCB材料的選擇。這是因?yàn)椋?b class="flag-6" style="color: red">PCB材料的選擇錯(cuò)誤也會(huì)對(duì)高速數(shù)字電路的信號(hào)傳輸性能造成不良影響。

2021-03-09 06:14:27

(但它也會(huì)增加寄生電容)的功能。雖然使用接地平面有許多好處,但是在實(shí)現(xiàn)時(shí)也必須小心,因?yàn)樗鼘?duì)能夠做的和不能夠做的都有一些限制。理想情況下,PCB有一層應(yīng)該專門(mén)用作接地平面。這樣當(dāng)整個(gè)平面不被破壞時(shí)才會(huì)產(chǎn)生

2014-08-20 16:13:46

摘要在高頻電路設(shè)計(jì)中,可以采用多種不同的傳輸線技術(shù)來(lái)進(jìn)行信號(hào)的傳輸,如常見(jiàn)的同軸線、微帶線、帶狀線和波導(dǎo)等。而對(duì)于PCB平面電路,微帶線、帶狀線、共面波導(dǎo)(CPW),及介質(zhì)集成波導(dǎo)(SIW)等是常用

2019-06-24 06:35:11

在一般的非高速PCB設(shè)計(jì)中,我們都是認(rèn)為電信號(hào)在導(dǎo)線上的傳播是不需要時(shí)間的,就是一根理想的導(dǎo)線,這種情況在低速的情況下是成立的,但是在高速的情況下,我們就不能簡(jiǎn)單的認(rèn)為其是一根理想的導(dǎo)線了,電信號(hào)

2019-05-30 06:59:24

PCB布線PCB布局怎樣去設(shè)計(jì)高速PCB?

2021-04-25 08:46:51

運(yùn)算放大器用作比較器結(jié)果不理想的原因?yàn)槭裁磳⑦\(yùn)算放大器用作比較器時(shí)會(huì)造成低速度?

2021-03-08 07:15:42

這顆電容變得不“理想”,這顆電容沒(méi)有設(shè)計(jì)好,就可能會(huì)導(dǎo)致整個(gè)項(xiàng)目的失敗。因此,對(duì)高速電路而言,這顆AC耦合電容沒(méi)有優(yōu)化好將是“致命”的。

2020-10-23 06:08:05

印刷電路板的映像平面一個(gè)映像平面(image plane)是一層銅質(zhì)導(dǎo)體(或其它導(dǎo)體),它位于一個(gè)印刷電路板(PCB)里面。它可能是一個(gè)電壓平面,或鄰近一個(gè)電路或訊號(hào)路由

2009-05-15 14:46:55 0

0 一個(gè)映像平面(imageplane)是一層銅質(zhì)導(dǎo)體(或其它導(dǎo)體),它位于一個(gè)印刷電路板(PCB)里面。它可能是一個(gè)電壓平面,或鄰近一個(gè)電路或訊號(hào)路由層(signalroutinglayer)的0V參考平

2010-06-06 11:41:00 0

0 高速電路PCB設(shè)計(jì)技巧分享,好東西,喜歡的朋友可以下載來(lái)學(xué)習(xí)。

2016-01-18 15:41:19 0

0 高速電路PCB設(shè)計(jì)實(shí)踐,好東西,喜歡的朋友可以下載來(lái)學(xué)習(xí)。

2016-01-18 15:41:19 0

0 PCB板平面變壓器設(shè)計(jì)與仿真,感興趣的小伙伴們可以看看。

2016-07-26 16:29:36 0

0 高速電路PCB板級(jí)設(shè)計(jì)技巧,很有用

2016-12-16 21:20:06 0

0 高速電路PCB板級(jí)設(shè)計(jì)技巧

2017-01-28 21:32:49 0

0 描述了高速PCB電路板信號(hào)完整性設(shè)計(jì)方法。 介紹了信號(hào)完整性基本理論, 重點(diǎn)討論了如何采用高速PCB設(shè)計(jì)方法保證高速數(shù)采模塊的信號(hào)完整性

2017-11-08 16:55:13 0

0 很多人對(duì)于PCB走線的參考平面感到迷惑,經(jīng)常有人問(wèn):對(duì)于內(nèi)層走線,如果走線一側(cè)是VCC,另一側(cè)是GND,那么哪個(gè)是參考平面?

2018-03-08 17:18:54 9515

9515

在高頻電路設(shè)計(jì)中,經(jīng)常會(huì)用到AC耦合電容,要么在芯片之間加兩顆直連,要么在芯片與連接器之間加兩顆。看似簡(jiǎn)單,但一切都因?yàn)樾盘?hào)的高速而不同。信號(hào)的高速傳輸使這顆電容變得不“理想”,這顆電容沒(méi)有設(shè)計(jì)好,就可能會(huì)導(dǎo)致整個(gè)項(xiàng)目的失敗。因此,對(duì)高速電路而言,這顆AC耦合電容沒(méi)有優(yōu)化好將是“致命”的。

2018-08-18 11:40:43 6861

6861 一個(gè)映像平面(image plane)是一層銅質(zhì)導(dǎo)體(或其它導(dǎo)體),它位于一個(gè)印刷電路板(PCB)里面。它可能是一個(gè)電壓平面,或鄰近一個(gè)電路或訊號(hào)路由層(signal routing layer

2018-09-10 08:00:00 7

7 如果MEMS傳感器安裝到PCB后輸出不理想, 可先從 PCB 設(shè)計(jì)及焊膏使用方面著手。

2019-08-16 21:24:00 1496

1496 PCB走線的參考平面在哪?

很多人對(duì)于PCB走線的參考平面感到迷惑,經(jīng)常有人問(wèn):對(duì)于內(nèi)層走線,如果走線一側(cè)是VCC,另一側(cè)是GND,那么哪個(gè)是參考平面?

2019-08-20 15:47:13 6457

6457 電路中不可避免會(huì)用到一些直插式的元件,如BGA封裝,必然會(huì)在PCB上形成許多貫穿整個(gè)電路板的通孔。

2019-09-24 14:27:04 3765

3765 default線寬及線距(綜合考慮高速電路性能及PCB板廠制程能力):6mil

2019-10-27 09:43:27 2550

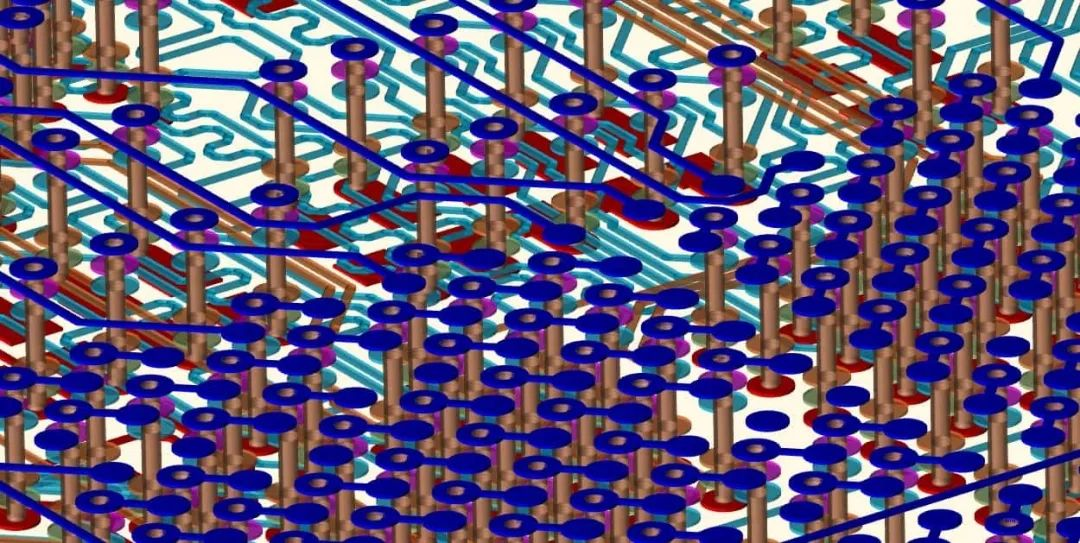

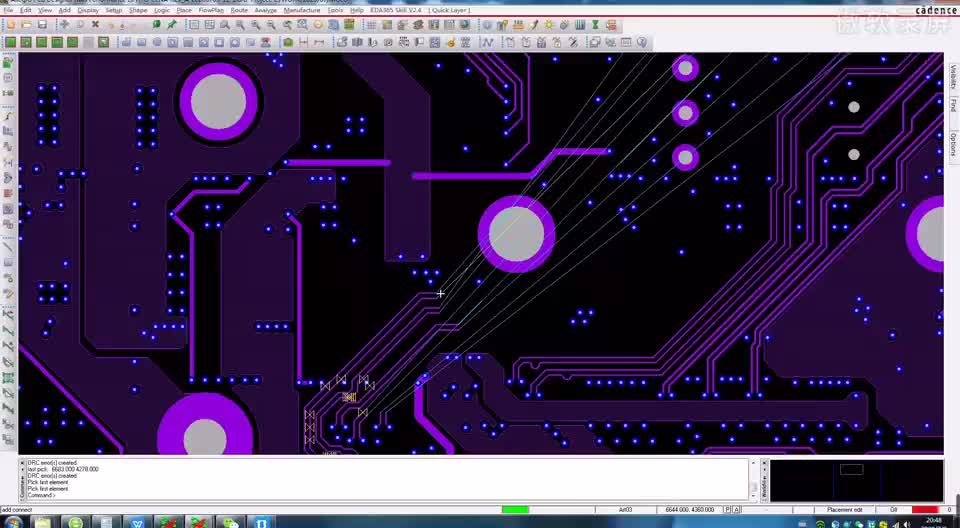

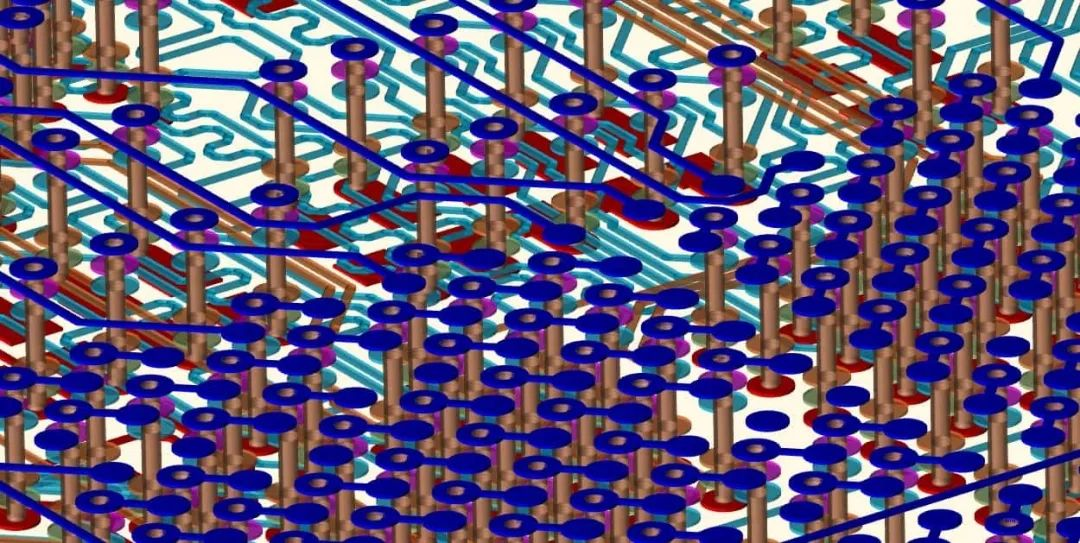

2550 高速電路--數(shù)模混合電路最新PCB創(chuàng)新技術(shù) 大家好!在這里,為大家介紹一種新的PCB設(shè)計(jì)創(chuàng)新技術(shù),下面的圖為設(shè)計(jì)好的PCB文件的底層放大局部視圖;該PCB文件為4層電路板,圖中的過(guò)孔與底層覆銅的地線

2020-05-06 10:06:17 966

966 高速電路設(shè)計(jì)是一個(gè)非常復(fù)雜的設(shè)計(jì)過(guò)程,在進(jìn)行高速電路設(shè)計(jì)時(shí)有多個(gè)因素需要加以考慮,這些因素有時(shí)互相對(duì)立。如高速器件布局時(shí)位置靠近,雖可以減少延時(shí),但可能產(chǎn)生串抗和顯著的熱效應(yīng)。因此在設(shè)計(jì)中,需權(quán)衡

2020-07-10 10:28:00 6

6 隨著高速 PCB 設(shè)計(jì)的引入,電路建筑行業(yè)正在為設(shè)計(jì)師,工程師和 PCB 制造而改變。如果您需要有關(guān) PCB 技術(shù)的復(fù)習(xí)知識(shí),需要知道如何設(shè)計(jì) PCB ,或者是電路初學(xué)者,我們的綜合指南將為您提

2020-10-23 19:42:12 3522

3522 電路板上信號(hào)最理想的返回路徑是大面積的金屬或平面層,該金屬層將成為參考平面。通常,這將是一個(gè)接地平面,并且需要在信號(hào)走線的相鄰層上,并在它們之間有一層電介質(zhì)。

2020-11-19 16:06:57 2183

2183 導(dǎo)熱硅脂是應(yīng)用在發(fā)熱體與散熱器之間的導(dǎo)熱散熱材料,是用來(lái)提高組件的傳熱效率。但是有人反應(yīng)說(shuō)買(mǎi)了貴的導(dǎo)熱硅脂,散熱效果卻不理想,沒(méi)有達(dá)到令人滿意的程度。今天,小編就來(lái)為大家解答:導(dǎo)致導(dǎo)熱硅脂散熱效果不理想的原因究竟在哪里。

2021-09-30 11:40:05 1550

1550 高速PCB不同種類的電源平面分割后,如何處理直流壓降過(guò)大?

2022-01-04 09:29:25 1458

1458 在PCB設(shè)計(jì)過(guò)程中,電源平面的分割或者是地平面的分割,會(huì)導(dǎo)致平面的不完整,這樣信號(hào)走線的時(shí)候,它的參考平面就會(huì)出現(xiàn)從一個(gè)電源面跨接到另一個(gè)電源面,這種現(xiàn)象我們就叫做信號(hào)跨分割。

2022-12-23 09:34:03 4634

4634

電子發(fā)燒友網(wǎng)站提供《PCB項(xiàng)目之平面揚(yáng)聲器.zip》資料免費(fèi)下載

2023-01-30 11:03:09 2

2 馬斯克收購(gòu)?fù)铺睾蠼?jīng)營(yíng)狀況很不理想 推特X平臺(tái)或失敗 馬斯克透露推特的經(jīng)營(yíng)狀況很不理想;目前推特的廣告收入下降50%且債務(wù)負(fù)擔(dān)沉重;更可怕的是推特的現(xiàn)金流仍然為負(fù)。 為此馬斯克正抓緊開(kāi)源節(jié)流,包括

2023-08-23 18:46:01 741

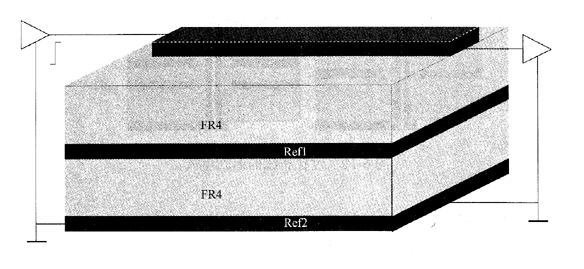

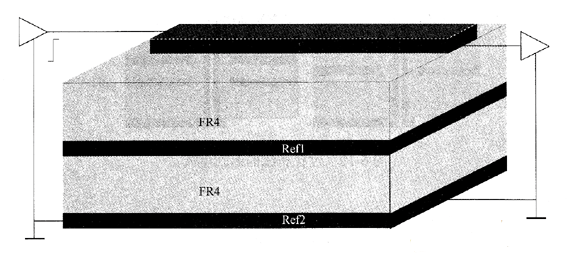

741 回路電流的分布總是趨于減小回路電感。對(duì)于圖1所示的結(jié)構(gòu),返回路徑是沿電容→參考平面1(Ref1)→參考平面2(Ref2)流動(dòng)的。信號(hào)路徑上的電流在懸空的中間參考平面Ref1的上表面感應(yīng)出渦流,參考平面Ref2的返回電流叉在中間參考平面Ref1的下表面上感應(yīng)出渦流

2023-08-25 14:47:54 322

322

回路電流的分布總是趨于減小回路電感。對(duì)于圖1所示的結(jié)構(gòu),返回路徑是沿電容→參考平面1(Ref1)→參考平面2(Ref2)流動(dòng)的。信號(hào)路徑上的電流在懸空的中間參考平面Ref1的上表面感應(yīng)出渦流,參考平面Ref2的返回電流叉在中間參考平面Ref1的下表面上感應(yīng)出渦流

2023-08-28 14:37:10 224

224

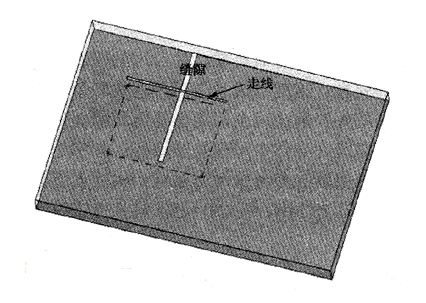

理想的參考平面應(yīng)該為其鄰近信號(hào)層上的信號(hào)路徑提供完美的返回路徑,理想的參考平面應(yīng)該是一個(gè)完整的實(shí)體平面。但在實(shí)際系統(tǒng)中,并不總存在這樣一個(gè)實(shí)體平面。

2023-09-12 15:10:19 148

148

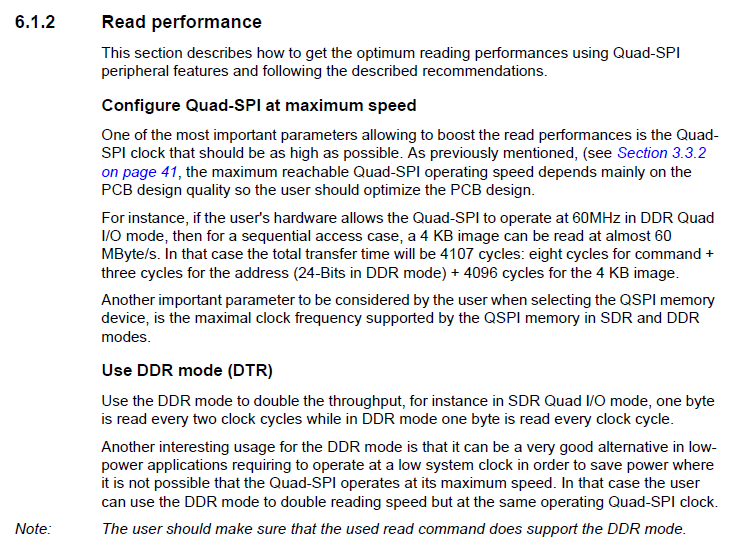

STM32L4R9的QuadSPI Flash通訊速率不理想

2023-11-06 17:06:20 421

421

高速電路PCB板級(jí)設(shè)計(jì)技巧

2022-12-30 09:22:19 39

39 高速電路PCB板級(jí)設(shè)計(jì)技巧

2023-03-01 15:37:57 2

2 高速電路無(wú)疑是PCB設(shè)計(jì)中要求非常嚴(yán)苛的一部分,因?yàn)?b class="flag-6" style="color: red">高速信號(hào)很容易被干擾,導(dǎo)致信號(hào)質(zhì)量下降,所以在PCB設(shè)計(jì)的過(guò)程中就需要避免或降低這種情況的發(fā)生。 在具體的高速電路布局布線中,這些知識(shí)技能需要掌握

2023-11-06 14:55:20 255

255 PCB 高速電路板 Layout 設(shè)計(jì)指南

2023-11-30 10:07:58 1269

1269

PCB設(shè)計(jì)之高速電路

2023-12-05 14:26:22 288

288

一站式PCBA智造廠家今天為大家講講PCB信號(hào)跨分割線怎么處理?PCB設(shè)計(jì)中跨分割的處理方法。在 PCB設(shè)計(jì) 過(guò)程中,電源平面的分割或者是地平面的分割,會(huì)導(dǎo)致平面的不完整,這樣信號(hào)走線的時(shí)候

2023-12-04 10:26:34 288

288

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論