低溫漂低功耗的帶隙基準源技術設計

摘 要:設計一種低溫漂低功耗的帶隙基準結構,在傳統帶隙基準核心電路結構上增加一對PNP管,兩個雙極型晶體管疊加的結構減小了運放的失調電壓對輸出電壓的影響,降低了基準電壓的溫度失調系數。電路設計與仿真基于CSMC 0.5 μm CMOS工藝,經流片,測得室溫下帶隙基準輸出電壓為1.326 65 V,在-40~+85 ℃范圍內的溫度系數為2.563 ppm/℃;?在3.3 V電源電壓下,整個電路的功耗僅為2.81 μW;在2~4 V之間的電源調整率為206.95 ppm。

關鍵詞:帶隙基準;低溫漂;低功耗;CMOS

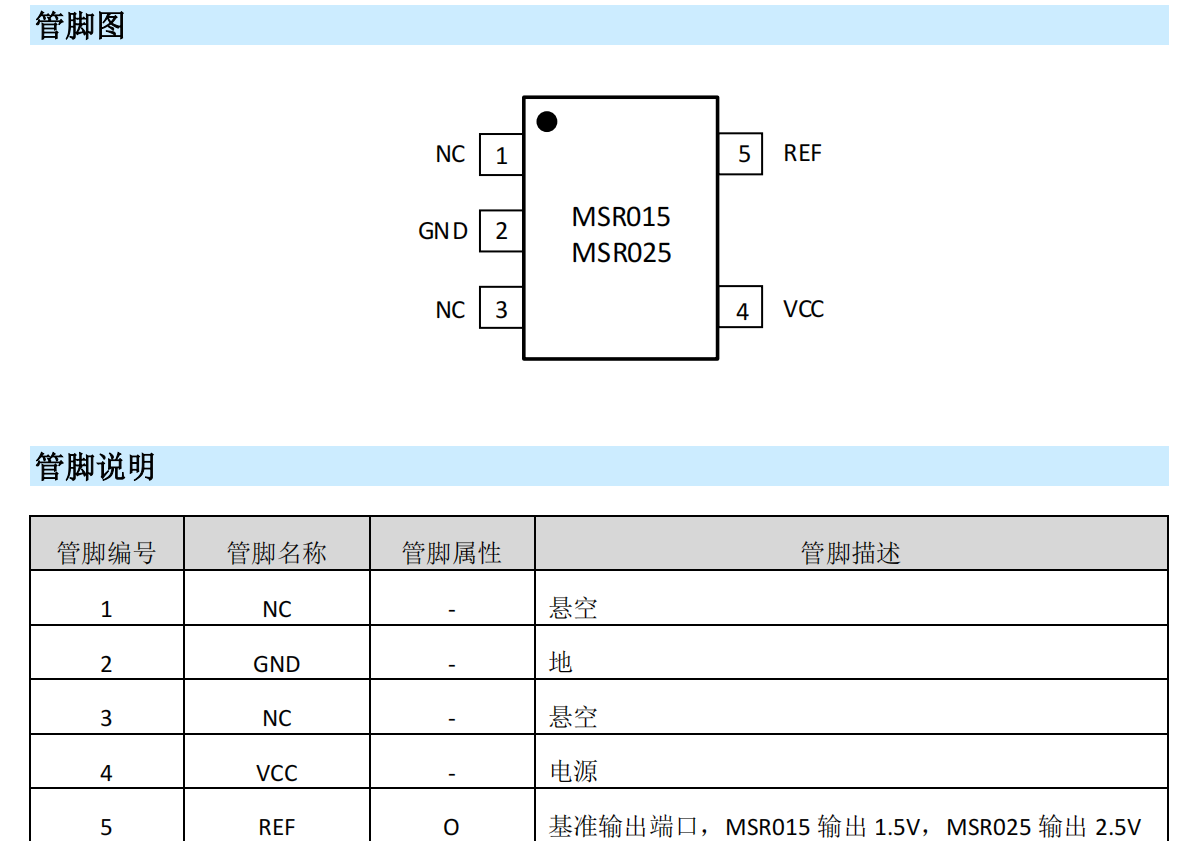

便攜式電子產品在市場上占有越來越大的份額,對低電壓、低功耗的基準電壓源的需求量大大增加,也導致帶隙基準的設計要求有了較大的提高。帶隙基準廣泛應用于數/模轉換、模/數轉換、存儲器以及開關電源等數模混合電路中。基準源的穩定性對整個系統的內部電源的產生,輸出電壓的調整等都具有直接且至關重要的影響。基準電壓必須能夠克服制造工藝的偏差,系統內部電源電壓在工作范圍內的變化以及外界溫度的影響。

由文獻可知傳統的一階補償通常可以得到10 ppm/℃左右的溫度系數,而新發展的比較成熟的補償技術,包括二階溫度補償,分段線性補償,指數溫度補償等其他的補償方法,文獻中所提及的電路的結構均比較復雜,或受到比較多的工藝的限制,或運用BiCMOS工藝,其制造成本比較高。在此設計一種以共源共柵電流鏡為負載的低溫漂高電源抑制比CMOS帶隙基準電壓源,利用新型核心電路和NMOS為輸入管的套筒式共源共柵運算放大器使得帶隙基準的輸出溫度系數遠小于傳統帶隙基準的溫度系數。

1 曲率補償的帶隙基準

1.1 VBE的溫度特性

由文獻可知,雙極型晶體管的VBE的溫度曲線不是簡單地隨溫度做線性變化的,其溫度特性為:

其中:VBG0為由零度推導出的PN結外接電壓;T0為參考溫度,T為絕對溫度;VBE0是雙極晶體管在溫度為T0時的發射結電壓;η為與溫度無關,但與工藝有關的一個參數;α的值與集電極電流Ic的溫度特性有關(I0與溫度成正比即PTAT電流時α=1;當I0是與溫度無關的電流時,α=0)。

式(1)中與溫度相關的非線性項作泰勒展開可得:

其中:α0,α1...αn為常數項,傳統的帶系基準電路工作時只將VBE和溫度有關的非線性項的一次項消除,輸出值仍與溫度的高階項呈現非線性的相關性。要進一步的降低輸出的溫度相關性,就要使用新方法對VBE的非線性溫度系數進行補償。

1.2 帶隙基準原理

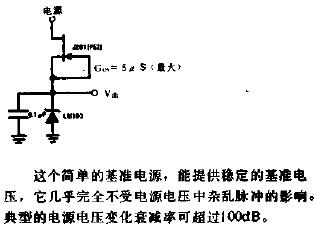

傳統帶系基準的電路如圖1所示,其主要由襯底PNP、電阻和運放構成。利用具有負溫度特性的雙極型晶體管的VBE與具有正溫度特性的熱電壓vt,在適當的系數下將兩者疊加,從而得到與溫度無關的基準電壓。在T0處,推導式(1)與溫度的關系:

處于深度負反饋的運放強制A,B點電壓近似相等,假設電阻R1,R2上流過的電流分別為I1和I2,而N為Q1,Q2發射極面積之比,因此:

寬長比相同的PMOS管P1,P2使兩條支路的電流近似相等,且具有相同溫度特性,就可以得到以下輸出參考電壓:

上式對在T0處溫度求導可得:

聯合上式和式(3)可以看出,只要選擇合適的電阻R1,R2值和數值N就可以得到一個溫度系數接近零的輸出電壓。

帶隙基準在設計中非常注重運算放大器這個環節。首先運算放大器的輸入匹配要求比較高,核心電路中PTAT電流的產生對后面有決定性的影響,如果可以設計一種高匹配的PTAT電流源,就可以保證運算放大器的輸入端的匹配,使基準電壓的產生有了基本保障。其次運算放大器有失調電壓,失調電壓也將被運算放大器放大,運放增益越大則被放大的噪聲越大。使用新的PTAT電流產生方法,使得能在帶隙基準中使用較低增益的運算放大器,就可以進一步減小輸出電壓中包含的運算失調電壓的影響。

2 新型帶系基準的設計與分析

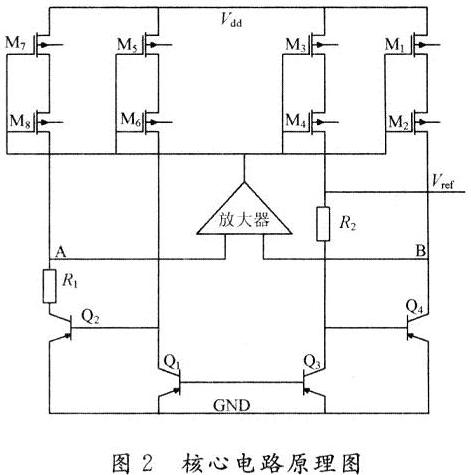

在溫度300 kΩ 時,VBE的溫度系數約為一2.2 mV/℃,VT的溫度系數約為O.86 mV/℃。這里所提出的核心電路如圖2所示,使用雙極型晶體管構成電路的核心部分,實現VBE和VT的線性疊加,得到溫度系數近似為零的輸出電壓。

2.1 核心電路

圖2中Q1和Q2,Q3和Q4的發射結面積相同,根據設計需要,取Q1和Q2的發射結面積為Q3和Q4的發射結面積的46倍。假設雙極型晶體管基極電流為零,且運放的增益足夠大,則A點和B點的電壓被迫相等:

其中:m為2條支路上的電流的比值;n為Q1和Q2的發射結面積之比。該電流是與絕對溫度成正比的PTAT電流,且與電源電壓無關。Vref的值為:

圖2采用2個雙極型晶體管疊加的結構,主要目的是減小運放失調電壓對輸出電壓的影響。假設運放的失調電壓為VOS,得到以下輸出電壓:

由上式可得,要減小運放的失調電壓的影響,可以增大括號中的第一項,也就是增大m或竹的值,取Q,和Q2的發射結面積為Q3和Q4的發射結面積的46倍就是為了減小失調電壓對輸出的影響,使用比較大的n值;其次,兩個相疊的雙極型晶體管使運算放大器的兩個輸入電壓中均含有兩個疊加的VBE,減小核心電路中對運算放大器的增益的需求,使得使用的運算放大器的增益小于傳統帶隙基準中的運算放大器的增益,從而使輸出中減小了運放失調電壓對輸出電壓的影響。兩種方法使該電路輸出的基準電壓有比使用傳統核心電路更低的溫度系數。

此電路的缺點是比普通帶隙基準多消耗1個電壓余度,兩個疊加的雙極型晶體管需要多消耗1個VBE,大約是0.7 V的電壓。電源電壓Vdd,至少需要2VBE+VDS1+VDS2,其中VDS1和VDS2分別為M1和M2的源漏電壓,共計3 V左右。在低電源電壓中應用這種結構對共源共柵電流鏡的輸出電壓擺幅即所消耗的電壓余度的要求比較高。

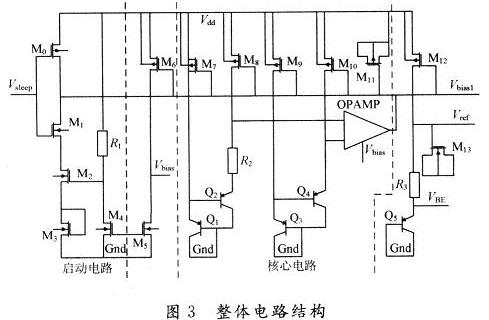

2.2 運算放大器的設計

要使帶隙基準有高的電源抑制比,電路中使用的運放開環增益和電源抑制比就必須足夠大。計算得運放增益大約60 dB,使用了套筒式共源共柵結構,以NMOS管作為輸入管,兩對PMOS管作為負載管。套筒式結構簡單,功耗和消耗的電壓余度和都相對要更小,比較適合設計中低功耗的需求,并且可以解決核心電路中疊加的雙極型晶體管多消耗的一個電壓余度。圖3是帶隙基準整體結構圖,啟動電路在核心結構正常工作后自動關斷,由圖可知運算放大器所需要的偏置電流由帶隙基準產生。

3 測試結果分析

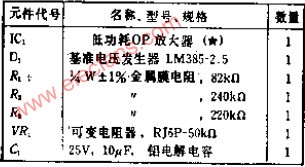

基于CSMCO.5μm DPTM CMOS工藝對版圖進行設計、流片。電路概貌圖如圖4所示。

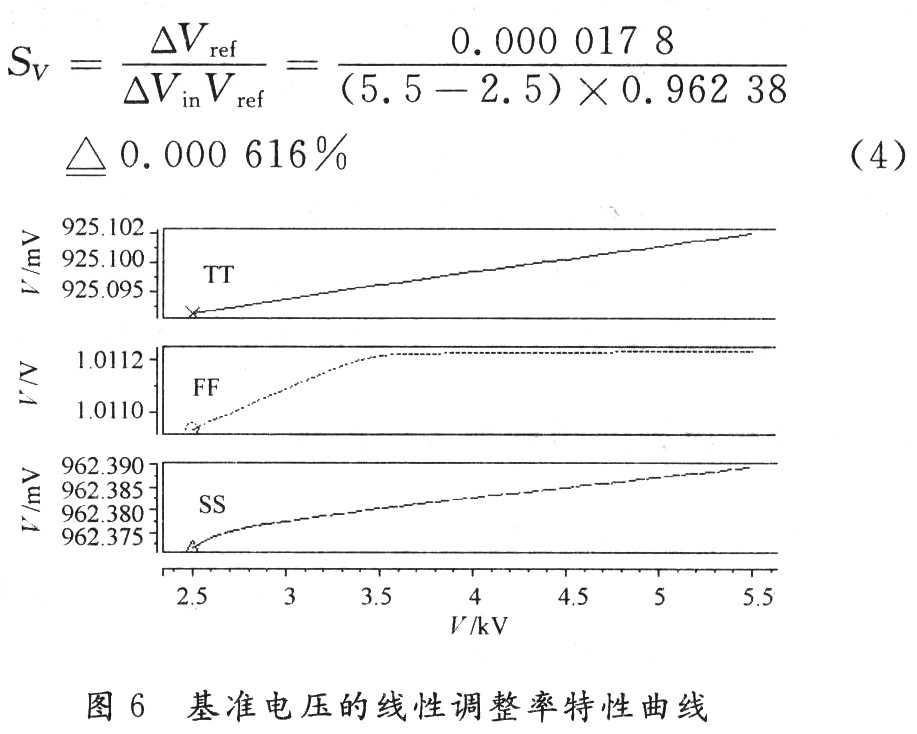

圖5是在3.3 V的電源電壓下,一40~+85℃的工作溫度范圍內帶隙基準的溫度特性曲線;表1是將電源電壓的設定范圍為2~4 V,對帶隙基準電路的輸出電壓進行測試,得到的電源電壓特性。

圖5 3.3 V電源電壓下,溫度為一40~+85℃時的輸出電壓與工作溫度曲線圖5表示的是基準電壓源的溫度特性曲線,測試結果表明此電壓源在工作溫度范圍內,溫度系數為2.563 ppm/℃。

表1是電源電壓特性分布,在室溫下,電源電壓在2~4 V間變化時的輸出電壓,由表1可知,此電壓源在電源電壓為2 V時就可以正常工作。基準電壓源在2~4 V間的輸出差值為413.9μV,即電源調整率為206.95 ppm。

蒙特卡羅分析是用于衡量器件特性值對電路性能影響的一種測試分析方法。在每個蒙特卡羅分析中,器件的特征值被當作潛在影響測試結果的因素并進行分類,由于測試是隨機選取樣本,各個特征值也將是隨機。在一個完整的測試結束后,可以得到1個或多個結果。每一項性質將得到一系列可被統計學統計的結果。對帶隙基準而言,主要特征值包括制造中的摻雜濃度的分布,內部電源電壓值的偏差和外界的溫度變化。

分析測試結果的方法是將它們歸納在不同范圍中,每個范圍表示在所有結果中占有的比例。將這些范圍用柱狀圖表示出來,每部分柱狀圖都由其高度表示在總體中占有的數量。

圖6是在室溫下選取80個芯片并對其帶隙基準電路輸出電壓測試。由圖可以看出,輸出電壓有95%以上都分布在設計的輸出電壓周圍,在實際應用中不需要trim就可以得到合適的輸出電壓。

4? 結 語

這里設計了一種具有低溫漂低功耗且不需要trim的基準電壓源,利用低壓共源共柵電流鏡來減小輸出電壓對電源電壓的依賴。測試結果表示:電路在2 V電源電壓下就可以正常工作,輸出基準電壓為1.326 65 V;在-40~+85℃之間的溫度系數為2.563 ppm/0C;電路在3.3 V電源電壓下,功耗僅為2.81 μW,可以廣泛應用在移動電子設備中。

電子發燒友App

電子發燒友App

評論