在這個(gè)項(xiàng)目中,我們用 VHDL 語(yǔ)言創(chuàng)建一個(gè) 8 位算術(shù)邏輯單元 (ALU),并在連接到帶有輸入開(kāi)關(guān)和 LED 顯示屏的定制 PCB 的 Altera CPLD 開(kāi)發(fā)板上運(yùn)行。

2023-10-24 17:05:57 52

52

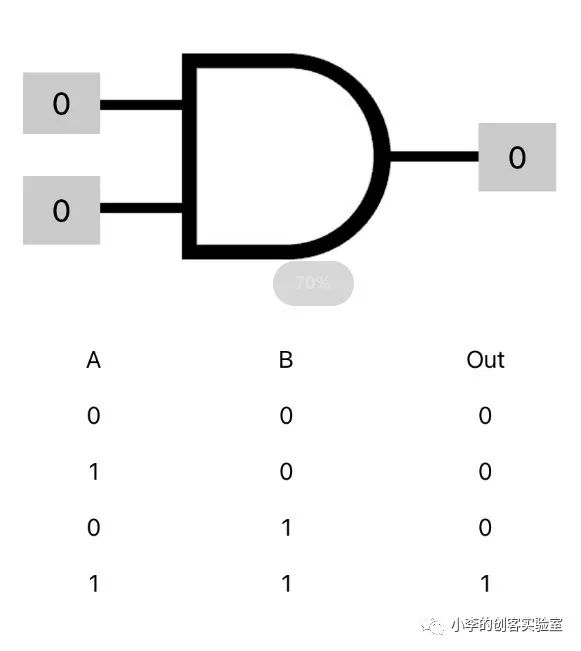

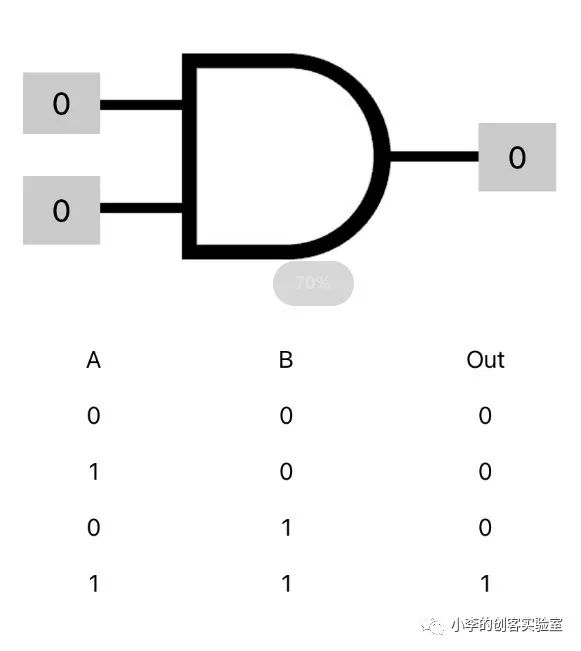

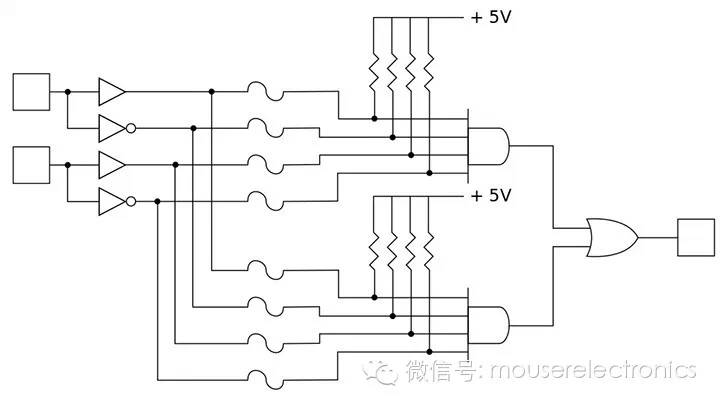

邏輯門(mén)(Logic Gates)是在集成電路(Integrated Circuit)上的基本組件。簡(jiǎn)單的邏輯門(mén)可由晶體管組成。

2023-07-08 14:38:31 513

513

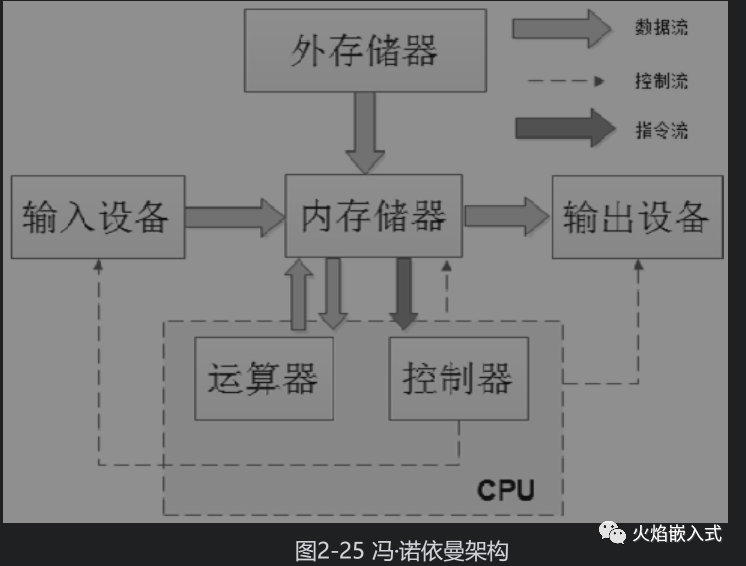

ALU(算術(shù)邏輯單元)、控制單元、寄存器、Cache(緩存)。

2023-07-07 14:46:51 1141

1141

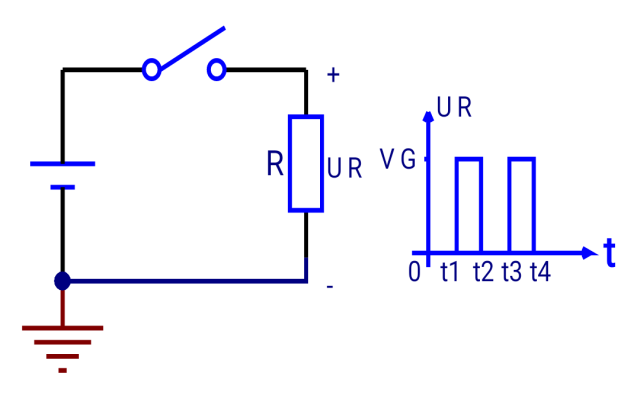

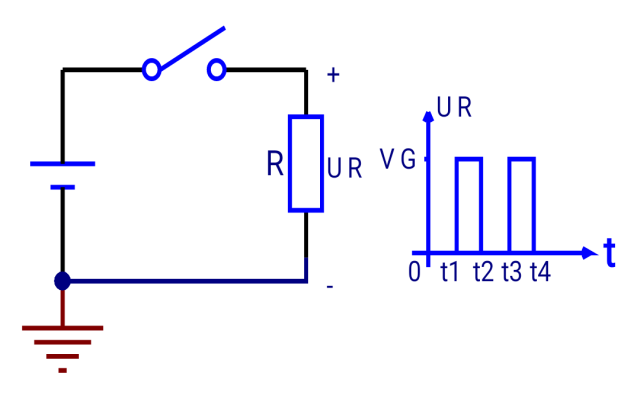

用數(shù)字信號(hào)完成對(duì)數(shù)字量進(jìn)行邏輯運(yùn)算和算術(shù)運(yùn)算的電路稱為數(shù)字電路。由于它具有邏輯運(yùn)算和邏輯處理功能,所以又稱為數(shù)字邏輯電路。現(xiàn)代的數(shù)字電路由半導(dǎo)體工藝制成的數(shù)字集成器件構(gòu)造而成。邏輯門(mén)是數(shù)字電路的基本單元電路,就如同在模擬電路中基本放大電路是模擬電路的基本單元電路。

2023-03-24 10:39:29 1277

1277

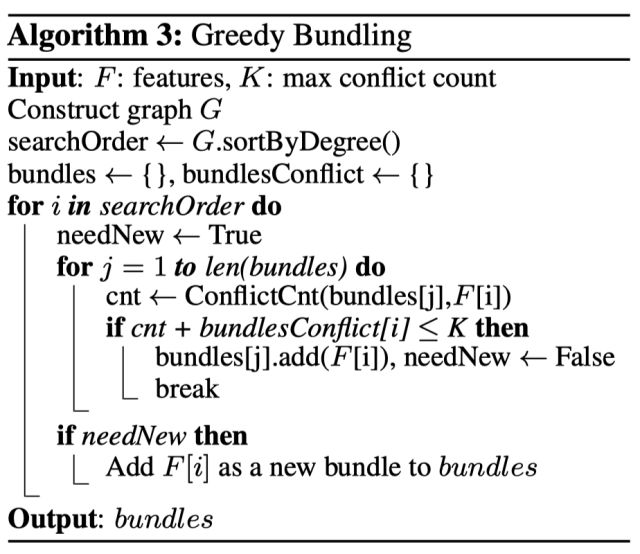

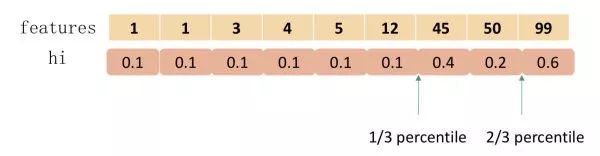

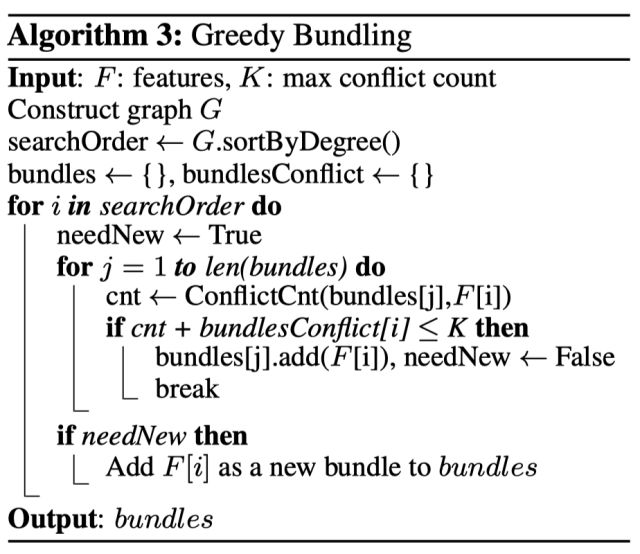

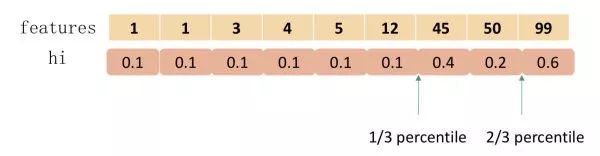

本文是決策樹(shù)的第三篇,主要介紹基于 Boosting 框架的主流集成算法,包括 XGBoost 和 LightGBM。

XGBoost

2023-02-17 15:58:05 2025

2025

本文是決策樹(shù)的第三篇,主要介紹基于 Boosting 框架的主流集成算法,包括 XGBoost 和 LightGBM。

XGBoost

2023-02-17 15:58:02 298

298

本文是決策樹(shù)的第三篇,主要介紹基于 Boosting 框架的主流集成算法,包括 XGBoost 和 LightGBM。

XGBoost

2023-02-17 15:57:58 429

429

算術(shù)邏輯單元/函數(shù)發(fā)生器 Number of channels (#) 4 Technology Family LS Input type Bipolar

2022-12-13 15:47:54

在進(jìn)行MCU開(kāi)發(fā)時(shí),有時(shí)需要用到一些簡(jiǎn)單的數(shù)字邏輯電路,LPC804與LPC55XX系列集成了PLU(Programmable Logic Unit),即可編程邏輯單元,可創(chuàng)建小型組合與時(shí)序邏輯電路,降低成本。

2022-12-01 09:17:42 823

823 最近我一直在思考這個(gè)問(wèn)題,下文是我的解釋。計(jì)算機(jī)的核心是一個(gè)稱為算術(shù)邏輯單元(ALU)的功能塊。毫不奇怪,這是執(zhí)行算術(shù)和邏輯運(yùn)算的地方,比如算術(shù)上兩個(gè)數(shù)字相加求和、邏輯上兩個(gè)數(shù)值進(jìn)行“與”運(yùn)算。

2022-10-31 10:39:25 755

755

;3.2.2 全加器電路 3.2.3 集成算術(shù)/邏輯運(yùn)算單元 3.3 信號(hào)變換電路 3.3.1 編碼器

2008-05-15 21:57:28

邏輯單元(Logic Element,LE)在FPGA器件內(nèi)部,用于完成用戶邏輯的最小單元。一個(gè)邏輯陣列包含16個(gè)邏輯單元以及一些其他資源, 在一個(gè)邏輯陣列內(nèi)部的16個(gè)邏輯單元有更為緊密的聯(lián)系,可以實(shí)現(xiàn)特有的功能。

2022-06-15 16:50:21 2067

2067 CLB是xilinx基本邏輯單元,每個(gè)CLB包含兩個(gè)slices,每個(gè)slices由4個(gè)(A,B,C,D)6輸入LUT和8個(gè)寄存器組成。

2022-04-24 14:48:55 2801

2801 DSP48E1片的數(shù)學(xué)部分由一個(gè)25位的預(yù)加器、2個(gè)25位、18位的補(bǔ)法器和3個(gè)48位的數(shù)據(jù)路徑多路復(fù)用器(具有輸出X、Y和Z)組成,然后是一個(gè)3輸入加法器/減法器或2輸入邏輯單元(參見(jiàn)圖2-5)。使用2輸入邏輯單元時(shí),不能使用乘法器。

2022-01-21 14:14:26 842

842 51系統(tǒng)指令中算術(shù)運(yùn)算有加、進(jìn)位加…等指令邏輯運(yùn)算有與、或、異或等…算術(shù)運(yùn)算和邏輯運(yùn)算指令對(duì)標(biāo)志位的影響:PSW寄存器中有四個(gè)測(cè)試標(biāo)志位:P(奇偶)、OV(溢出)、CY(進(jìn)位)、AC(輔助進(jìn)位)對(duì)于

2021-11-23 16:21:11 2

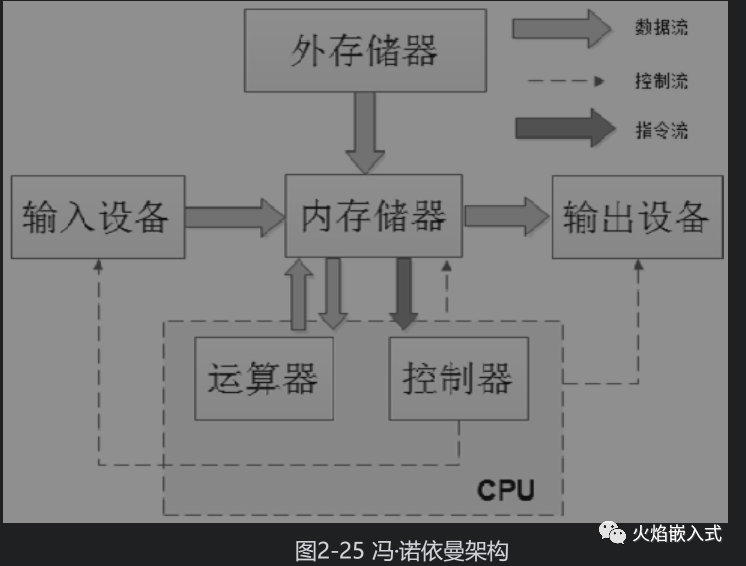

2 按照計(jì)算機(jī)原始定義 計(jì)算機(jī)系統(tǒng)由五大部分—控制單元(CU)、算術(shù)運(yùn)算單元(ALU)、存儲(chǔ)器(Memory)、輸入設(shè)備(Input)、輸出設(shè)備(Output)組成。早期的計(jì)算機(jī)的(晶體管的或集成

2021-11-13 14:51:02 8

8 算術(shù)熵編碼CABAC(力普拉斯電源技術(shù)有限公司)-算術(shù)熵編碼CABAC? ? ? ? ? ? ? ? ??

2021-08-31 12:24:34 0

0 的青睞,并得到了廣泛的應(yīng)用。由于算術(shù)邏輯單元(ALU)在運(yùn)算中對(duì)系統(tǒng)性能要求很高,而采用中小規(guī)模的集成電路設(shè)計(jì)的系統(tǒng)既龐大又存在穩(wěn)定性的問(wèn)題。

2021-01-04 10:36:00 1909

1909

本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA硬件基礎(chǔ)之FPGA的邏輯單元的工程文件免費(fèi)下載。

2020-12-10 15:00:28 18

18 貌似需要將S,A,B,F(xiàn)的位數(shù)統(tǒng)一起來(lái),S是幾位的設(shè)定,那么輸入A,B,輸出F也同樣是幾位的設(shè)定,如果計(jì)算結(jié)果超過(guò)了,就采用進(jìn)位的辦法。

2020-09-03 16:59:55 19376

19376

看看上面這個(gè)實(shí)物,圖片中是最著名的ALU——英特爾74181,1970年發(fā)布,當(dāng)時(shí)它是第一個(gè)完全被封裝在單個(gè)芯片里的完整ALU,對(duì)人們來(lái)說(shuō)這是一個(gè)驚人的工程。

2020-06-18 16:27:01 13115

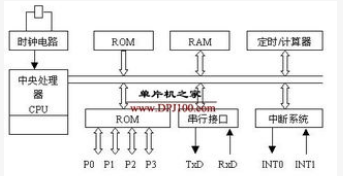

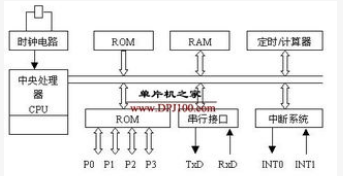

13115 CPU是整個(gè)單片機(jī)的核心部件,由運(yùn)算器和控制器組成。運(yùn)算器可以完成算術(shù)運(yùn)算和邏輯運(yùn)算,其操作順序在控制器控制下進(jìn)行。

2019-10-29 16:44:33 7573

7573

A)算術(shù)和邏輯運(yùn)算,可對(duì)半字節(jié)(一個(gè)字節(jié)是8位,半個(gè)字節(jié)就是4位)和單字節(jié)數(shù)據(jù)進(jìn)行操作。

B)加、減、乘、除、加1、減1、比較等算術(shù)運(yùn)算。

C)與、或、異或、求補(bǔ)、循環(huán)等邏輯運(yùn)算。

D)位處理功能(即布爾處理器)。

2019-09-14 17:20:00 3952

3952 FPGA架構(gòu)與ASIC類(lèi)似,但與CPLD差異巨大。一個(gè)通用的FPGA架構(gòu)包括配置邏輯塊(CLB)陣列、I / O焊盤(pán)和可編程互連,如圖3所示。加入了時(shí)鐘電路以驅(qū)動(dòng)時(shí)鐘信號(hào)到每一個(gè)邏輯塊。算術(shù)邏輯單元、存儲(chǔ)單元和譯碼器也是典型的組件。

2019-08-28 15:12:20 2592

2592

按照單片機(jī)的組成結(jié)構(gòu),其最基本的能夠完成算術(shù)運(yùn)算和邏輯運(yùn)算,即完成數(shù)值計(jì)算和邏輯判斷。

2019-07-27 10:26:44 541

541 本文檔的主要內(nèi)容詳細(xì)介紹的是51單片機(jī)的數(shù)據(jù)傳遞和算術(shù)運(yùn)算及邏輯運(yùn)算指令表資料免費(fèi)下載。

2019-07-09 17:40:00 1

1 Reconfigurable Cell Array)結(jié)構(gòu)測(cè)試FPGA邏輯單元PLB(Programmable Logic Block)的方法,該方法對(duì)邏輯單元PLB 進(jìn)行了分類(lèi)、分階段的測(cè)試,同時(shí)進(jìn)行電路模擬實(shí)驗(yàn)。

2018-11-28 09:02:00 3842

3842

為了推廣更加系統(tǒng)化的數(shù)值外推,我們提出了一種新的架構(gòu),它將數(shù)字式信息表示為線性激活函數(shù),使用原始算術(shù)運(yùn)算符進(jìn)行運(yùn)算,并由學(xué)習(xí)門(mén)控制。

2018-08-07 08:27:30 2958

2958 雖然加法和減法使得許多有用的系統(tǒng)泛化成為可能,但是可能需要學(xué)習(xí)更復(fù)雜的數(shù)學(xué)函數(shù)(例如乘法)的強(qiáng)健能力。 圖2描述了這樣一個(gè)單元:神經(jīng)算術(shù)邏輯單元(NALU),它學(xué)習(xí)兩個(gè)子單元之間的加權(quán)和,一個(gè)能夠

2018-08-05 09:54:16 3126

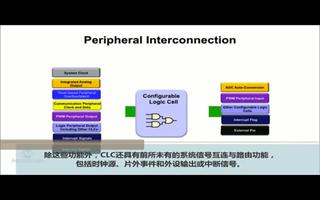

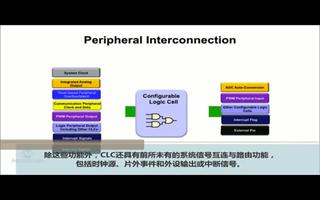

3126 本視頻介紹了可配置邏輯單元(CLC),該靈活外設(shè)可用于整合片上和片外邏輯信號(hào),用來(lái)產(chǎn)生不同的輸出值,可以在多種條件下將器件從低功耗休眠模式喚醒。嵌入式設(shè)計(jì)人員還可以利用時(shí)序邏輯特性開(kāi)發(fā)簡(jiǎn)單的狀態(tài)機(jī),而無(wú)需CPU干預(yù)。此外,CLC還具有系統(tǒng)信號(hào)互連與路由功能,包括時(shí)鐘源、片外事件和外設(shè)輸出或中斷信號(hào)。

2018-06-07 02:46:00 3945

3945

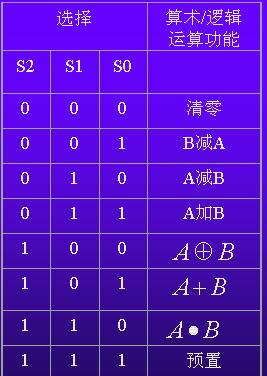

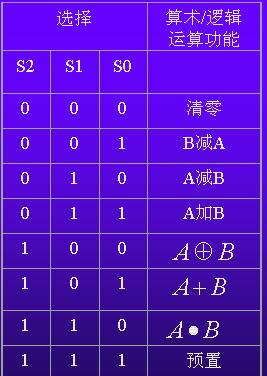

本文主要介紹了一文讀懂如何驗(yàn)證74ls181運(yùn)算和邏輯功能。ALU(算術(shù)邏輯單元)能進(jìn)行多種算術(shù)運(yùn)算和邏輯運(yùn)算。一個(gè)4位的ALU—74LS181運(yùn)算功能發(fā)生器能進(jìn)行16種算術(shù)運(yùn)算和邏輯運(yùn)算。輸入模塊

2018-05-09 09:05:49 34197

34197

已有的一些直覺(jué)模糊集成算子在處理一些特殊直覺(jué)模糊數(shù)時(shí)會(huì)出現(xiàn)反直覺(jué)現(xiàn)象。首先介紹了兩個(gè)直覺(jué)模糊集成算子和直覺(jué)模糊數(shù)的比較方法。接著,舉例說(shuō)明了這些集成算子在某些情況下出現(xiàn)的反直覺(jué)現(xiàn)象。然后提出了基于£

2017-11-17 14:36:52 9

9 內(nèi)容提要: 本章系統(tǒng)地介紹數(shù)字電路的基本邏輯單元門(mén)電路,及其對(duì)應(yīng)的邏輯運(yùn)算與圖形描述符號(hào),并針對(duì)實(shí)際應(yīng)用介紹了三態(tài)邏輯門(mén)和集電極開(kāi)路輸出門(mén),最后簡(jiǎn)要介紹TTL集成門(mén)和CMOS集成門(mén)的邏輯功能、外特性

2017-10-26 17:27:59 9

9 盡量不要使用"大于""小于"這樣的判斷語(yǔ)句, 這樣會(huì)明顯增加使用的邏輯單元數(shù)量 .看一下報(bào)告,資源使用差別很大.

2017-02-11 11:31:11 876

876 一....盡量不要使用"大于""小于"這樣的判斷語(yǔ)句, 這樣會(huì)明顯增加使用的邏輯單元數(shù)量 .看一下報(bào)告,資源使用差別很大.

2017-02-11 06:52:20 1104

1104

電子專業(yè)單片機(jī)相關(guān)知識(shí)學(xué)習(xí)教材資料之Cyclone_IV器件的邏輯單元

2016-09-02 16:54:40 24

24 電子類(lèi)的基礎(chǔ)手冊(cè),很好的資料,工程師必備的資料。

2016-05-31 16:06:37 6

6 電子類(lèi)的基礎(chǔ)手冊(cè),很好的資料,工程師必備的資料。

2016-05-31 15:42:56 5

5 低功耗時(shí)鐘門(mén)控算術(shù)邏輯單元在不同F(xiàn)PGA中的時(shí)鐘能量分析

2015-11-19 14:50:20 0

0 韶山型電力機(jī)車(chē)邏輯控制單元,原理分析,超詳細(xì),鐵路專業(yè)人士必備!

2015-11-10 17:04:02 10

10 MIDI合成算法及其FPGA實(shí)現(xiàn).

2012-04-16 13:57:38 44

44 文中提出了一種基于加權(quán)co-occurrence矩陣的聚類(lèi)集成算法(WCSCE)。該方法首先計(jì)算出聚類(lèi)成員基于屬性值的co-occurrence矩陣,然后對(duì)聚類(lèi)成員的質(zhì)量進(jìn)行簡(jiǎn)單評(píng)價(jià)并賦予權(quán)重,生成加權(quán)co-occur

2012-02-29 14:11:17 27

27 芯片綜合的過(guò)程:芯片的規(guī)格說(shuō)明,芯片設(shè)計(jì)的劃分,預(yù)布局,RTL 邏輯單元的綜合,各邏輯單元的集成,測(cè)試,布局規(guī)劃,布局布線,最終驗(yàn)證等步驟。設(shè)計(jì)流程與思想概述:一個(gè)設(shè)計(jì)

2011-12-29 16:28:35 25

25 傳統(tǒng)的神經(jīng)網(wǎng)絡(luò)集成中各個(gè)自網(wǎng)絡(luò)間的相關(guān)性較大,從而影響集成的泛化能力,本內(nèi)容提出了基于負(fù)相關(guān)神經(jīng)網(wǎng)絡(luò)集成算法及其應(yīng)用

2011-05-26 15:45:49 18

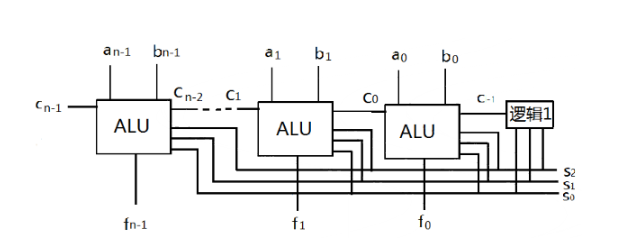

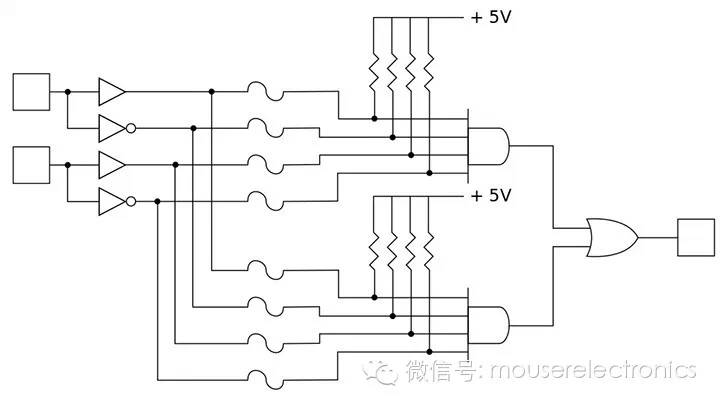

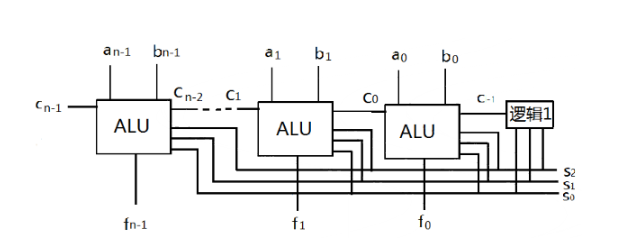

18 多功能算術(shù)/邏輯運(yùn)算單元(ALU) ,什么是多功能算術(shù)/邏輯運(yùn)算單元(ALU)

由一位全加器(FA)構(gòu)成的行波進(jìn)位加法器,它可以實(shí)現(xiàn)補(bǔ)碼數(shù)的加法運(yùn)算和減法運(yùn)算。但是這種加法/

2010-04-13 11:24:11 25416

25416 邏輯運(yùn)算,什么是邏輯運(yùn)算 計(jì)算機(jī)中除了進(jìn)行加、減、乘、除等基本算術(shù)運(yùn)算外,還可對(duì)兩個(gè)或一個(gè)邏輯數(shù)進(jìn)行邏輯運(yùn)算。所謂邏輯數(shù),是指不帶符號(hào)的二進(jìn)制

2010-04-13 10:48:38 29945

29945 充分地利用電路的結(jié)構(gòu)信息,提出一種應(yīng)用基本門(mén)單元完全測(cè)試集的測(cè)試生成算法,并給出了一些應(yīng)用實(shí)例,表明了算法的可行性。

2010-02-24 15:48:35 9

9 集成邏輯部件:本章主要分析和討論完成數(shù)字邏輯電路各種功能的基本邏輯部件——門(mén)電路的外特性及基本結(jié)構(gòu)。首先介紹目前廣泛應(yīng)用的TTL集成邏輯門(mén)電路,然后討論MOS集成邏輯電

2009-09-01 09:05:12 30

30 CMOS集成邏輯門(mén)的邏輯功能與參數(shù)測(cè)試一、實(shí)驗(yàn)?zāi)康?.掌握CMOS集成門(mén)電路的邏輯功能和器件的使用規(guī)則;2.學(xué)會(huì)CMOS與非門(mén)主要參數(shù)的測(cè)試方法。二、預(yù)習(xí)要求1.復(fù)

2009-07-15 18:37:20 51

51 摘要: 在簡(jiǎn)單介紹算術(shù)編碼和自適應(yīng)算術(shù)編碼的基礎(chǔ)上,介紹了利用FPGA器件并通過(guò)VHDL語(yǔ)言描述實(shí)現(xiàn)自適應(yīng)算術(shù)編碼的過(guò)程。整個(gè)編碼系統(tǒng)在LTERA公司的MAX+plus Ⅱ軟

2009-06-20 13:40:24 969

969

直線生成算法,尤其是直線掃描轉(zhuǎn)換算法,是計(jì)算機(jī)圖形學(xué)和計(jì)算機(jī)輔助設(shè)計(jì)等領(lǐng)域最基本、最重要的算法之一。本文提出了一種改進(jìn)的直線生成算法——直線掃描轉(zhuǎn)換的五步生成算法

2009-06-06 16:24:27 24

24 集成邏輯門(mén)電路邏輯功能的測(cè)試

一、實(shí)驗(yàn)?zāi)康?

2009-03-28 09:49:44 11893

11893

TMS320F24X 指令集累加器、算術(shù)與邏輯指令附件

TMS320F24X 指令集累加器、算術(shù)與邏輯指令

助記

2008-10-17 22:41:11 1024

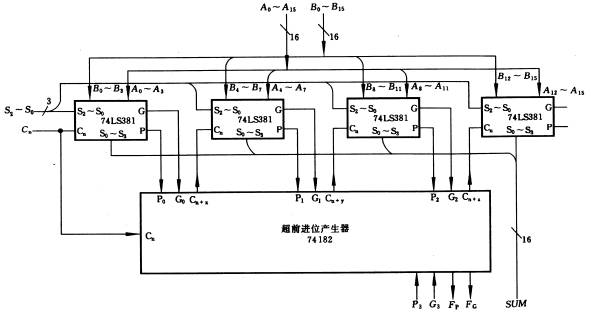

1024 74ls381引腳圖

集成算術(shù)/邏輯運(yùn)算單元(ALU)能夠完成一系列算術(shù)運(yùn)算和邏輯運(yùn)算。在這里我們介紹

2008-03-30 10:15:17 3981

3981

算術(shù)邏輯部件設(shè)計(jì)

2006-05-25 23:48:39 40

40

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論