電子發(fā)燒友網(wǎng)報(bào)道(文/吳子鵬)后摩爾定律時(shí)代,如何在不依賴價(jià)格昂貴的先進(jìn)制程的情況下顯著提升芯片的性能,成為行業(yè)共同關(guān)注的話題。此時(shí),封裝在整個(gè)產(chǎn)業(yè)中的戰(zhàn)略地位凸顯出來(lái),從傳統(tǒng)的倒裝和晶圓級(jí)封裝

2022-08-05 08:19:00 6763

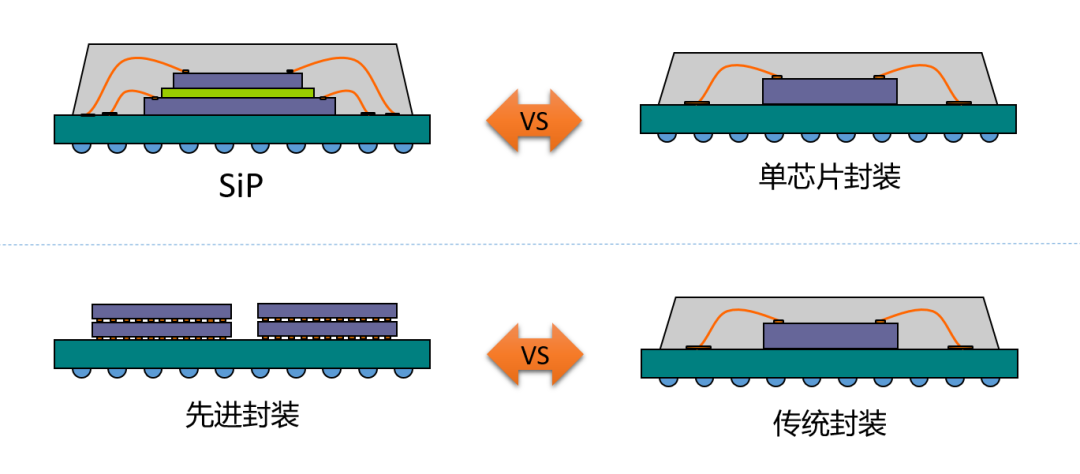

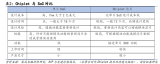

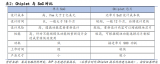

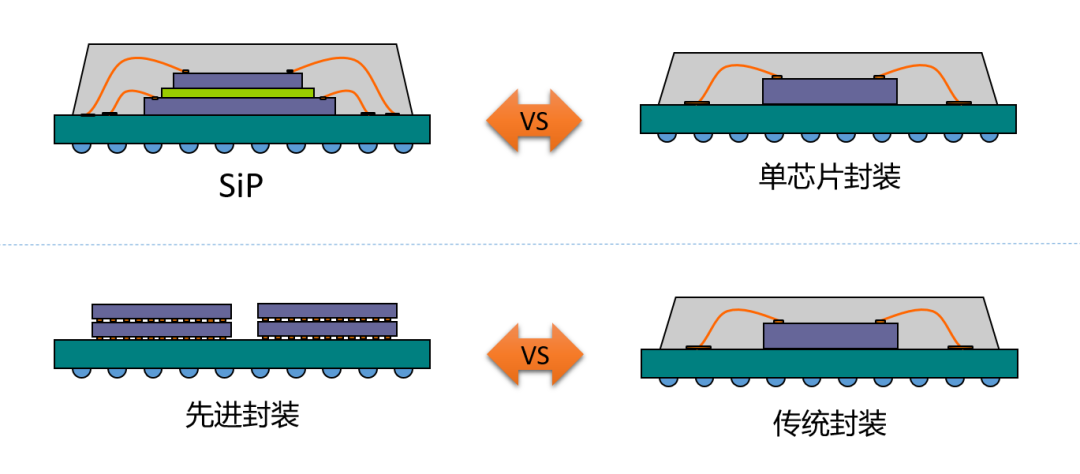

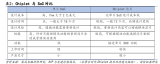

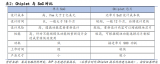

6763 SiP的關(guān)注點(diǎn)在于:系統(tǒng)在封裝內(nèi)的實(shí)現(xiàn),所以系統(tǒng)是其重點(diǎn)關(guān)注的對(duì)象,和SiP系統(tǒng)級(jí)封裝對(duì)應(yīng)的為單芯片封裝;先進(jìn)封裝的關(guān)注點(diǎn)在于:封裝技術(shù)和工藝的先進(jìn)性,所以先進(jìn)性的是其重點(diǎn)關(guān)注的對(duì)象,和先進(jìn)封裝對(duì)應(yīng)的是傳統(tǒng)封裝。

2021-03-15 10:31:53 8490

8490

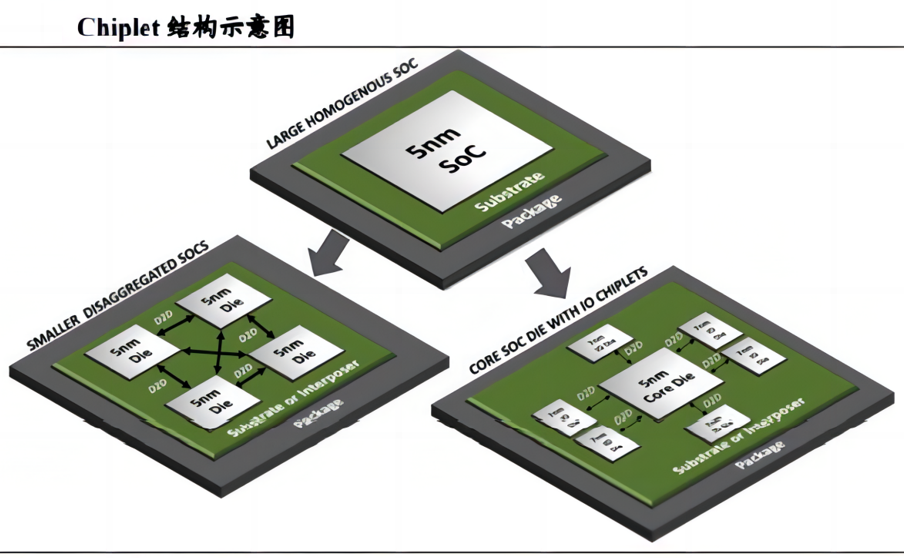

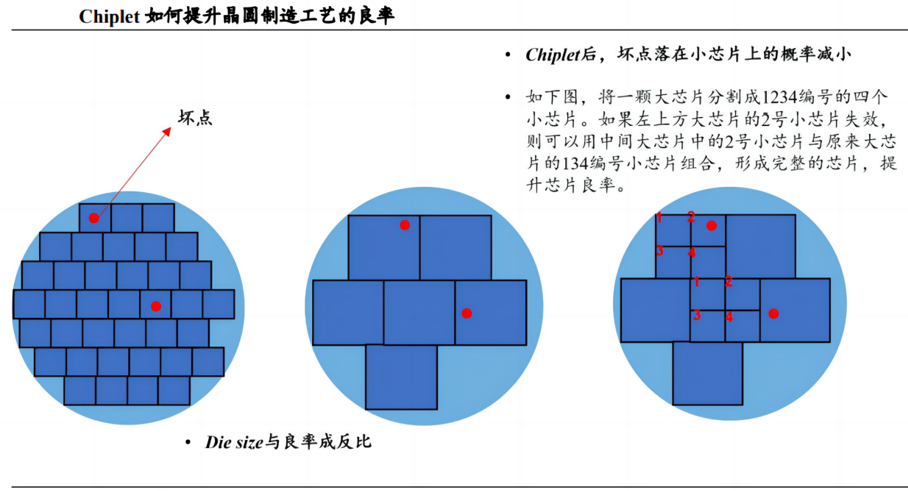

Chiplet可以使用更可靠和更便宜的技術(shù)制造。較小的硅片本身也不太容易產(chǎn)生制造缺陷。此外,Chiplet芯片也不需要采用同樣的工藝,不同工藝制造的Chiplet可以通過(guò)先進(jìn)封裝技術(shù)集成在一起。

2022-10-06 06:25:00 18480

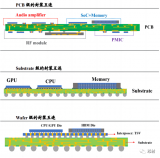

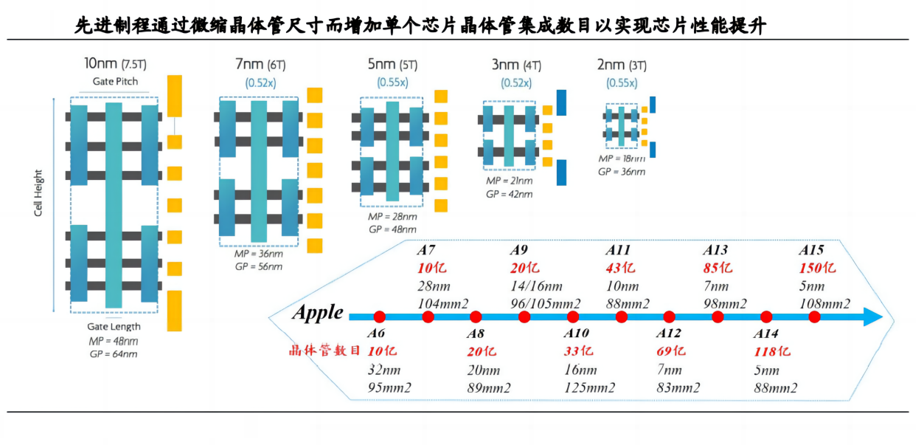

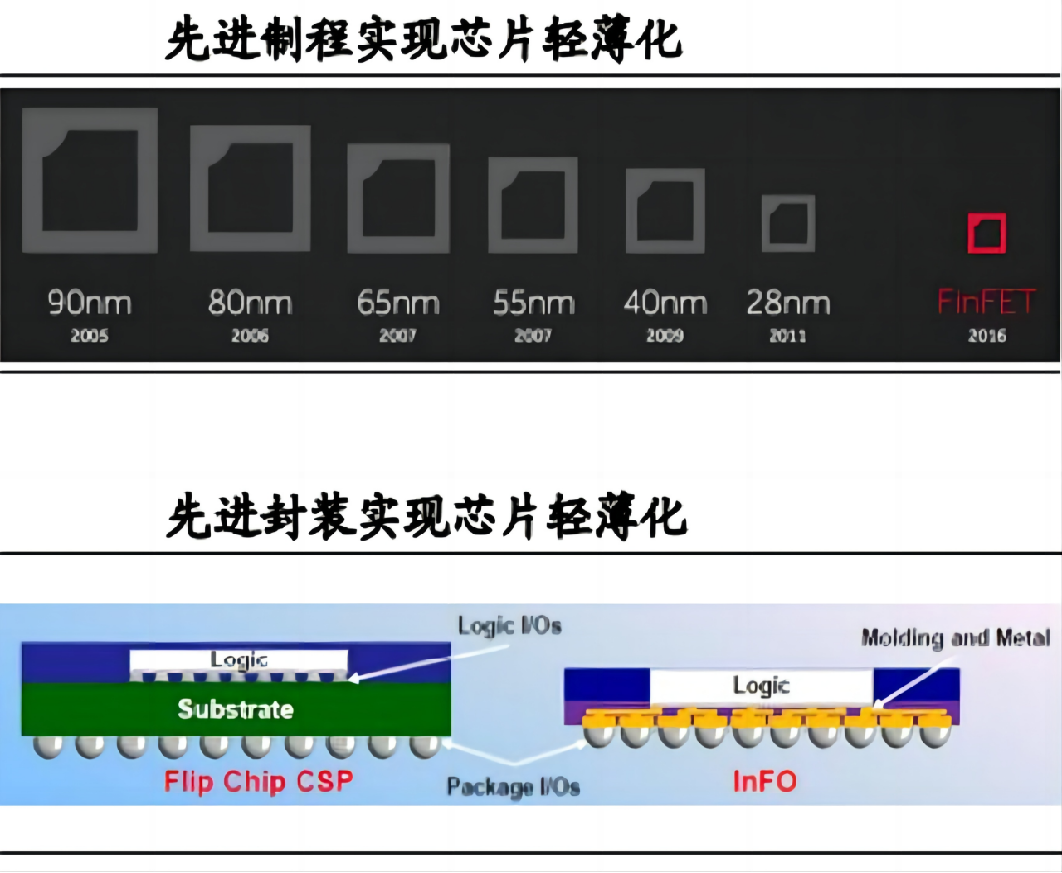

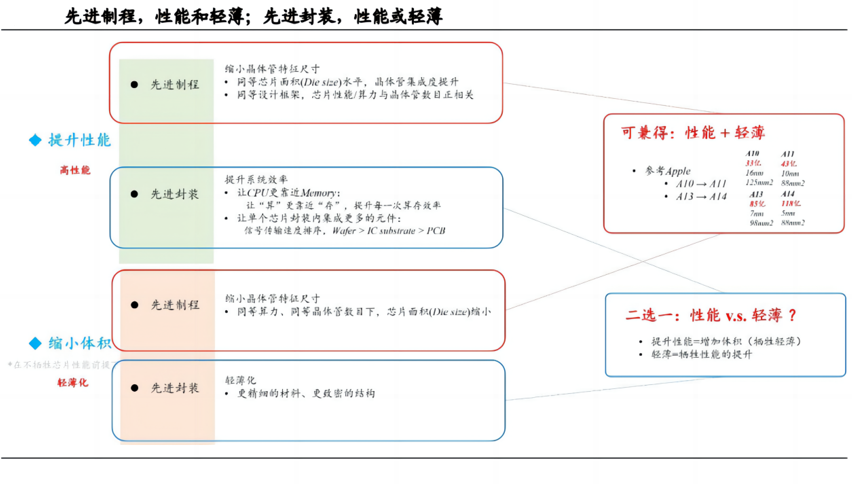

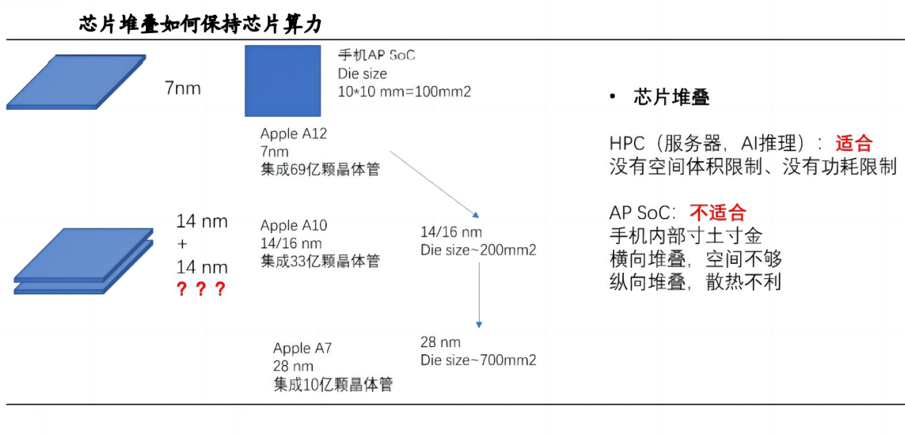

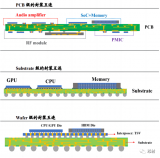

18480 芯片升級(jí)的兩個(gè)永恒主題:性能、體積/面積。芯片技術(shù)的發(fā)展,推動(dòng)著芯片朝著高性能和輕薄化兩個(gè)方向提升。而先進(jìn)制程和先進(jìn)封裝的進(jìn)步,均能夠使得芯片向著高性能和輕薄化前進(jìn)。

2023-02-14 10:43:02 1538

1538

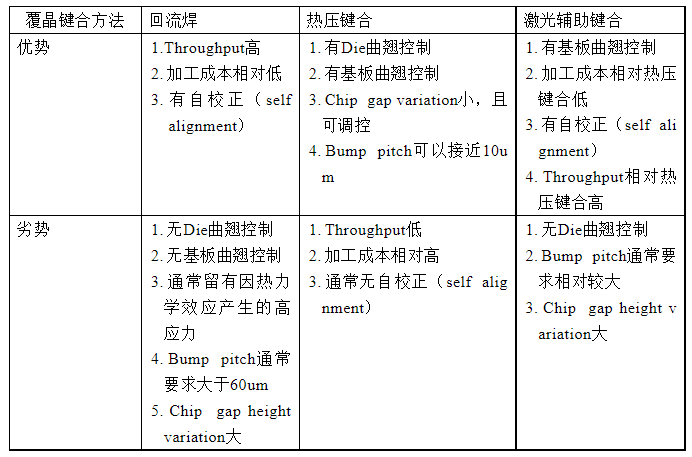

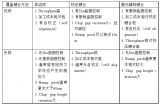

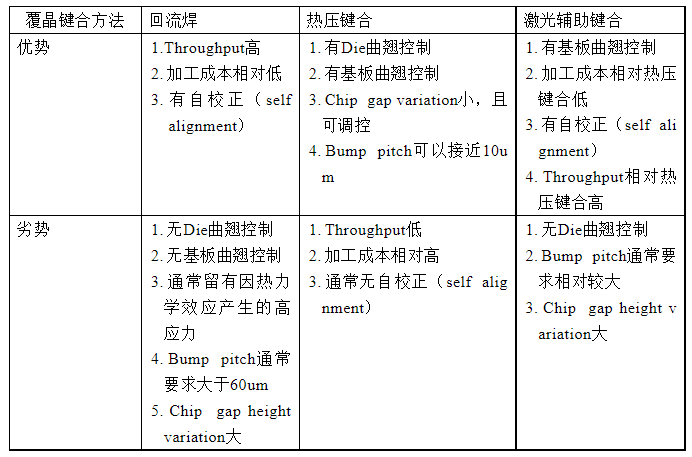

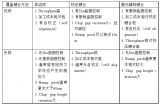

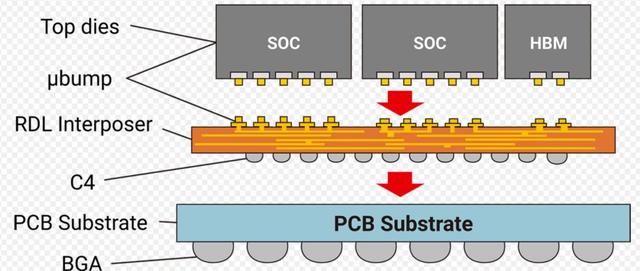

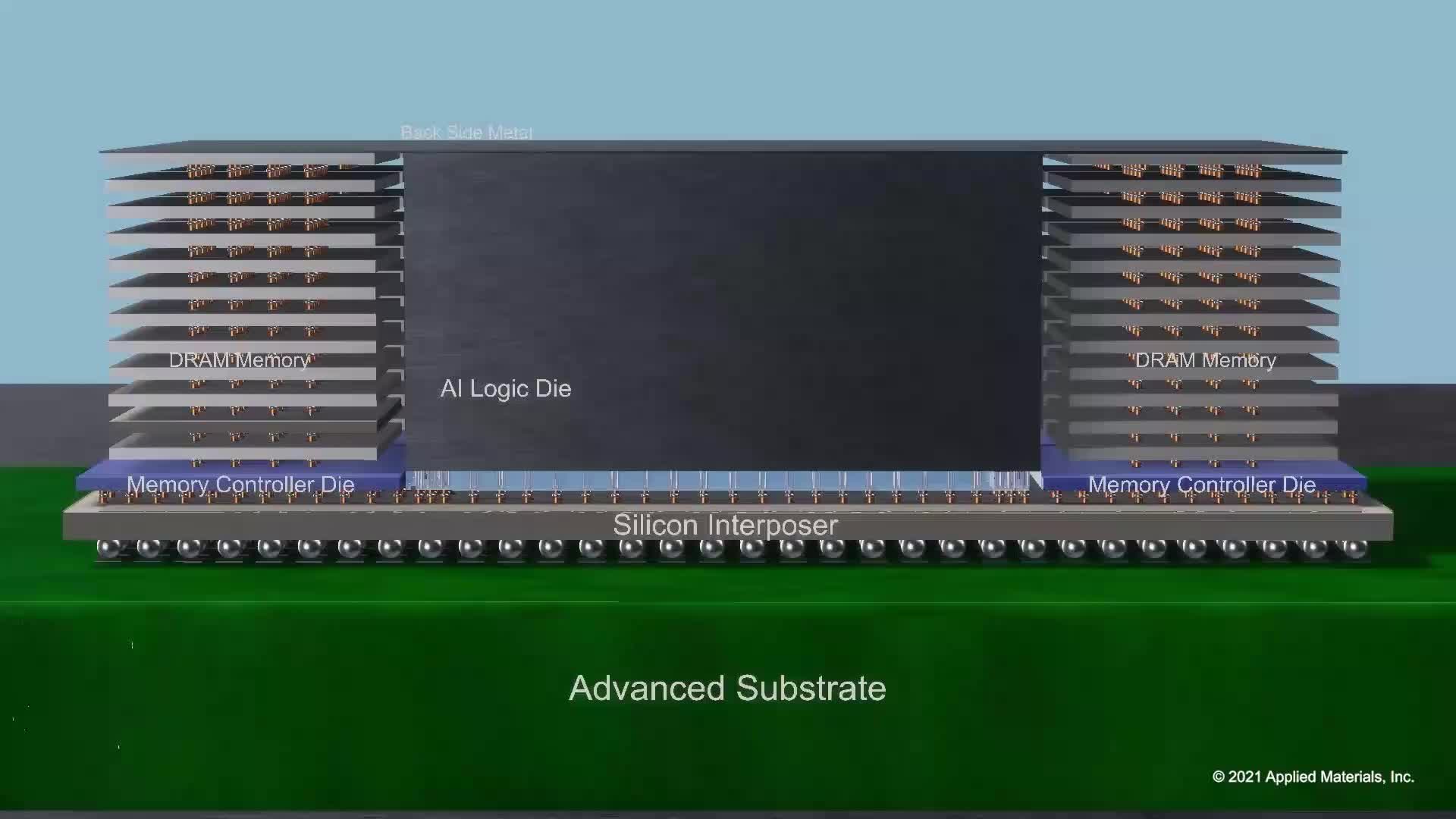

(858mm2)以及制程的縮小也變得非常艱難且性價(jià)比遇到挑戰(zhàn), 多芯片封裝技術(shù)來(lái)到了舞臺(tái)的中心成為進(jìn)一步提升芯片性能的關(guān)鍵。 覆晶鍵合技術(shù)已然成為先進(jìn)多芯片封裝最重要的技術(shù)之一。

2023-04-19 09:42:52 1011

1011

(858mm2)以及制程的縮小也變得非常艱難且性價(jià)比遇到挑戰(zhàn), 多芯片封裝技術(shù)來(lái)到了舞臺(tái)的中心成為進(jìn)一步提升芯片性能的關(guān)鍵。覆晶鍵合技術(shù)已然成為先進(jìn)多芯片封裝最重要的技術(shù)之一。

2023-05-11 10:24:38 615

615

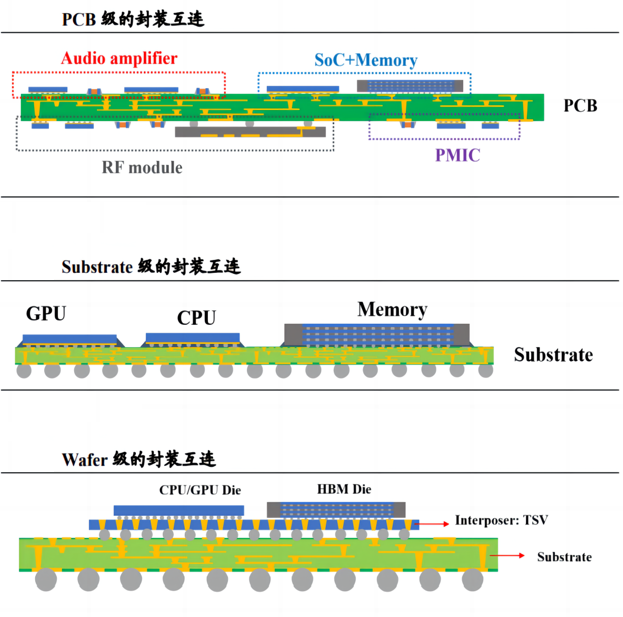

隨著電子產(chǎn)品趨向于功能化、輕型化、小型化、低功耗和異質(zhì)集成,以系統(tǒng)級(jí)封裝(System in Package, siP)、圓片級(jí)封裝( Wafer Level Package.WLP)、2.5D/3D 封裝等為代表的先進(jìn)封裝技術(shù)越來(lái)越多地應(yīng)用到電子產(chǎn)品中。

2023-05-11 14:39:38 451

451 先進(jìn)封裝是“超越摩爾”(More than Moore)時(shí)代的一大技術(shù)亮點(diǎn)。當(dāng)芯片在每個(gè)工藝節(jié)點(diǎn)上的微縮越來(lái)越困難、也越來(lái)越昂貴之際,工程師們將多個(gè)芯片放入先進(jìn)的封裝中,就不必再費(fèi)力縮小芯片了。本文將對(duì)先進(jìn)封裝技術(shù)中最常見的10個(gè)術(shù)語(yǔ)進(jìn)行簡(jiǎn)單介紹。

2023-07-12 10:48:03 625

625

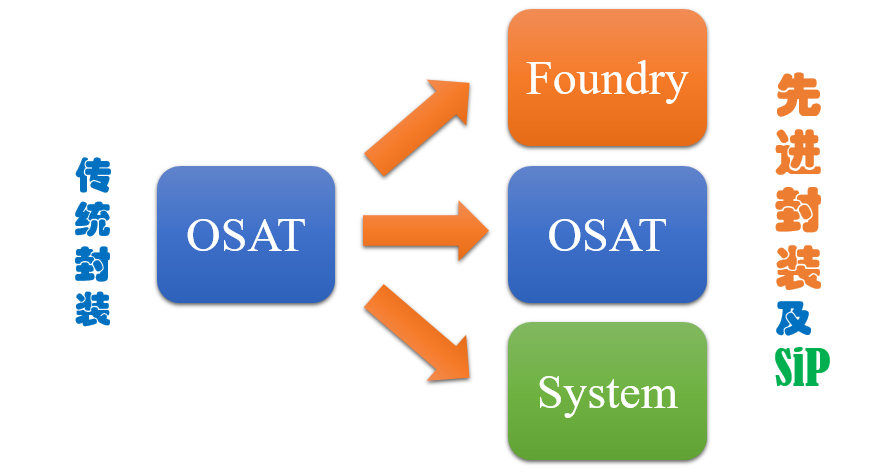

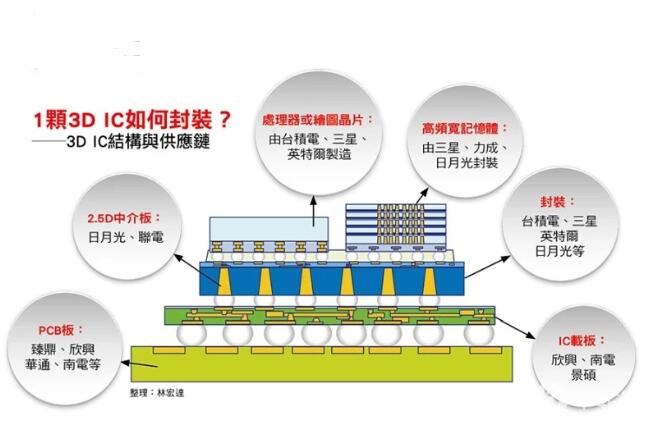

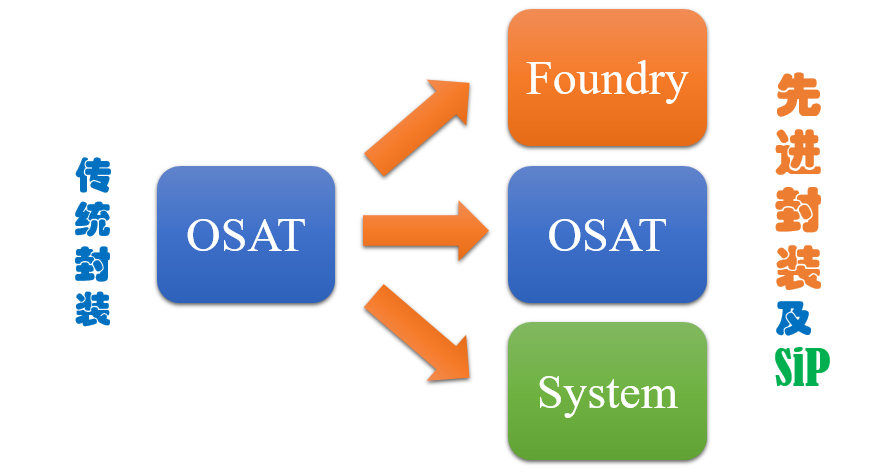

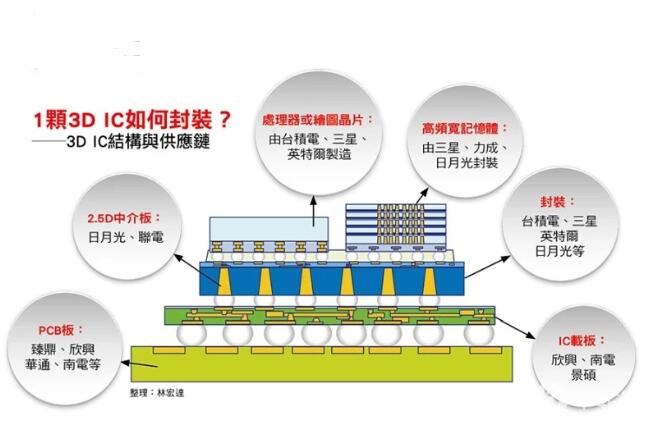

先進(jìn)封裝處于晶圓制造與封測(cè)的交叉區(qū)域 先進(jìn)封裝處于晶圓制造與封測(cè)制程中的交叉區(qū)域,涉及IDM、晶圓代工、封測(cè)廠商。先進(jìn)封裝要求在晶圓劃片前融入封裝工藝步驟,具體包括應(yīng)用晶圓研磨薄化、重布線(RDL

2023-08-07 10:59:46 852

852

? 半導(dǎo)體器件有許多封裝形式,按封裝的外形、尺寸、結(jié)構(gòu)分類可分為引腳插入型、表面貼裝型和高級(jí)封裝三類。從DIP、SOP、QFP、PGA、BGA到CSP再到SIP,技術(shù)指標(biāo)一代比一代先進(jìn)。總體說(shuō)來(lái)

2023-08-28 09:37:11 1072

1072

Chiplet也稱芯粒,通俗來(lái)說(shuō)Chiplet模式是在摩爾定律趨緩下的半導(dǎo)體工藝發(fā)展方向之一,是將不同功能芯片裸片的拼搭

2023-09-28 11:43:07 653

653

隨著晶圓級(jí)封裝技術(shù)的不斷提升,眾多芯片設(shè)計(jì)及封測(cè)公司開始思考并嘗試采用晶圓級(jí)封裝技術(shù)替代傳統(tǒng)封裝。其中HRP(Heat?Re-distribution?Packaging)晶圓級(jí)先進(jìn)封裝

2023-11-30 09:23:24 1124

1124

說(shuō)起傳統(tǒng)封裝,大家都會(huì)想到日月光ASE,安靠Amkor,長(zhǎng)電JCET,華天HT,通富微電TF等這些封裝大廠OSAT;說(shuō)起先進(jìn)封裝,當(dāng)今業(yè)界風(fēng)頭最盛的卻是臺(tái)積電TSMC,英特爾Intel,三星SAMSUNG等這些頂尖的半導(dǎo)體晶圓廠IC Foundry,這是為何呢?

2023-12-21 09:32:02 474

474

半導(dǎo)體器件有許多封裝形式,按封裝的外形、尺寸、結(jié)構(gòu)分類可分為引腳插入型、表面貼裝型和高級(jí)封裝三類。從DIP、SOP、QFP、PGA、BGA到CSP再到SIP,技術(shù)指標(biāo)一代比一代先進(jìn)。總體說(shuō)來(lái),半導(dǎo)體

2024-01-16 09:54:34 606

606

最近,在先進(jìn)封裝領(lǐng)域又出現(xiàn)了一個(gè)新的名詞“3.5D封裝”,以前聽?wèi)T了2.5D和3D封裝,3.5D封裝又有什么新的特點(diǎn)呢?還是僅僅是一個(gè)吸引關(guān)注度的噱頭?

2024-01-23 16:13:29 496

496

摘 要:先進(jìn)封裝技術(shù)不斷發(fā)展變化以適應(yīng)各種半導(dǎo)體新工藝和材料的要求和挑戰(zhàn)。在半導(dǎo)體封裝外部形式變遷的基礎(chǔ)上,著重闡述了半導(dǎo)體后端工序的關(guān)鍵一封裝內(nèi)部連接方式的發(fā)展趨勢(shì)。分析了半導(dǎo)體前端制造工藝的發(fā)展

2018-11-23 17:03:35

。如比較小的阻抗值、較強(qiáng)的抗干擾能力、較小的信號(hào)失真等等。芯片的封裝技術(shù)經(jīng)歷了好幾代的變遷,從DIP、QFP、PGA、BGA到CSP再到MCM。技術(shù)指標(biāo)和電器性能一代比一代先進(jìn)。

2011-10-28 10:51:06

有人又將其稱為圓片級(jí)-芯片尺寸封裝(WLP-CSP),以晶圓圓片為加工對(duì)象,在晶圓上封裝芯片。晶圓封裝中最關(guān)鍵的工藝為晶圓鍵合,即是通過(guò)化學(xué)或物理的方法將兩片晶圓結(jié)合在一起,以達(dá)到密封效果。如下

2021-02-23 16:35:18

先進(jìn)封裝發(fā)展背景晶圓級(jí)三維封裝技術(shù)發(fā)展

2020-12-28 07:15:50

MPU6050有軟件解算姿態(tài)和DMP解算姿態(tài),他們各自的優(yōu)缺點(diǎn)是什么呢?因?yàn)榇蠹叶贾赖氖荄MP可以減輕MCU的負(fù)擔(dān),但我看了好幾個(gè)微型四軸開源飛控的選擇都是用軟件解算,什么理由呢?

2019-05-29 04:36:05

的特性可通過(guò)改變其化學(xué)成分和工藝的控制調(diào)整來(lái)實(shí)現(xiàn),不僅可作為封裝的封蓋材料,它也是各種微電子產(chǎn)品重要的承載基板;陶瓷封裝的缺點(diǎn):1)與塑料封裝相比較,它的工藝溫度較高,成本較高;2)工藝自動(dòng)化與薄型化封裝

2019-12-11 15:06:19

8~12 英寸先進(jìn)封裝技術(shù)專用勻膠設(shè)備沈陽(yáng)芯源微電子設(shè)備有限公司沈陽(yáng)芯源微電子設(shè)備有限公司研制的8~12 英寸先進(jìn)封裝技術(shù)專用勻膠設(shè)備獲得“2007年中國(guó)半導(dǎo)體創(chuàng)新產(chǎn)

2009-12-14 10:42:38 8

8 論文綜述了自 1990 年以來(lái)迅速發(fā)展的先進(jìn)封裝技術(shù),包括球柵陣列封裝(BGA)、芯片尺寸封裝(CSP)、圓片級(jí)封裝(WLP)、三維封裝(3D)和系統(tǒng)封裝(SiP)等項(xiàng)新技術(shù);同時(shí),敘述了我國(guó)封

2009-12-14 11:14:49 28

28 Siemens 業(yè)務(wù)部門 Mentor 今天宣布推出業(yè)內(nèi)最全面和高效的針對(duì)先進(jìn) IC 封裝設(shè)計(jì)的解決方案 — Xpedition 高密度先進(jìn)封裝 (HDAP) 流程。

2017-06-27 14:52:20 1777

1777 SiP和Chiplet也是長(zhǎng)電科技重點(diǎn)發(fā)展的技術(shù)。“目前我們重點(diǎn)發(fā)展幾種類型的先進(jìn)封裝技術(shù)。首先就是系統(tǒng)級(jí)封裝(SiP),隨著5G的部署加快,這類封裝技術(shù)的應(yīng)用范圍將越來(lái)越廣泛。其次是應(yīng)用于

2020-09-17 17:43:20 9167

9167 什么是COB封裝? COB的優(yōu)缺點(diǎn)是啥子? 什么是綁定IC? Altiumdesigner 里面 如何繪制? 官方解答:COB封裝即chip On board,就是將裸芯片用導(dǎo)電或非導(dǎo)電膠粘附在互連

2020-09-29 11:15:00 11051

11051 (Waferlevelpackage),2.5D封裝(interposer,RDL等),3D封裝(TSV)等先進(jìn)封裝技術(shù)。 ▌ SoC vs.SiP ?SoC:全稱System-on-chip,系統(tǒng)級(jí)芯片

2020-10-21 11:03:11 28156

28156

今日,長(zhǎng)電科技中國(guó)區(qū)研發(fā)中心副總經(jīng)理李宗懌在中國(guó)集成電路設(shè)計(jì)業(yè)2020年會(huì)--封裝與測(cè)試分論壇上發(fā)表了主題為《先進(jìn)封裝的協(xié)同設(shè)計(jì)與集成開發(fā)》的演講。

2020-12-11 15:24:38 3063

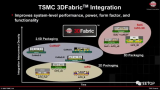

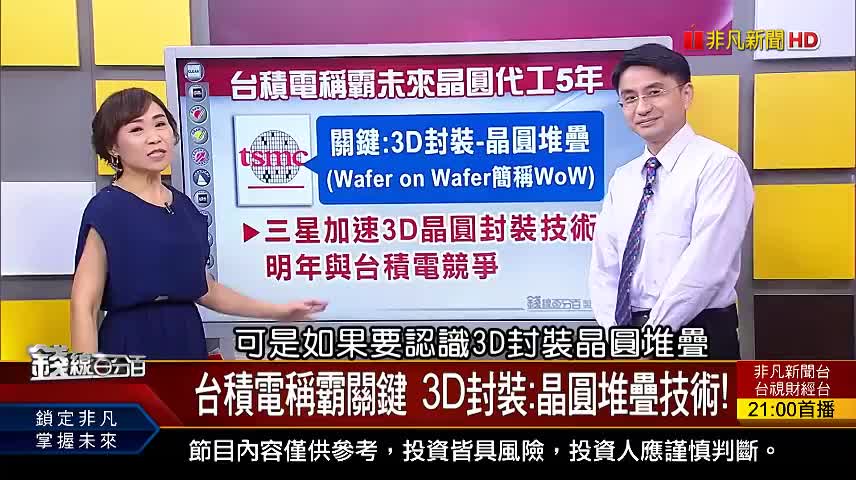

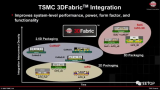

3063 臺(tái)積電和三星于先進(jìn)封裝的戰(zhàn)火再起。2020年,三星推出3D封裝技術(shù)品牌X-Cube,宣稱在7納米芯片可直接堆上SRAM內(nèi)存,企圖在先進(jìn)封裝拉近與臺(tái)積電的距離。幾天之后,臺(tái)積電總裁魏哲家現(xiàn)身,宣布推出自有先進(jìn)封裝品牌3D Fabric,臺(tái)積電最新的SoIC(系統(tǒng)集成芯片)備受矚目。

2021-01-04 10:37:09 1269

1269

據(jù)彭博社今日下午報(bào)道,繼赴美建設(shè)5nm晶圓代工廠后,全球晶圓代工龍頭臺(tái)積電正計(jì)劃赴日本建設(shè)先進(jìn)封裝廠。如果消息屬實(shí),這將是臺(tái)積電首座位于海外的封測(cè)廠。

2021-01-06 12:06:16 1804

1804 作為華天集團(tuán)晶圓級(jí)先進(jìn)封裝基地,華天昆山2008年6月落戶昆山開發(fā)區(qū),研發(fā)的晶圓級(jí)傳感器封裝技術(shù)、扇出型封裝技術(shù)、超薄超小型晶圓級(jí)封裝、晶圓級(jí)無(wú)源器件制造技術(shù)目前已達(dá)到世界領(lǐng)先水平。

2021-01-09 10:16:09 4166

4166 近日,蔣尚義在回歸中芯國(guó)際之后首次公開亮相,出席了第二屆中國(guó)芯創(chuàng)年會(huì),并發(fā)表演講。 據(jù)科創(chuàng)板日?qǐng)?bào)報(bào)道,蔣尚義此次演講提出了多個(gè)觀點(diǎn),如摩爾定律的進(jìn)展已接近物理極限;后摩爾時(shí)代的發(fā)展趨勢(shì)是研發(fā)先進(jìn)封裝

2021-01-19 10:25:02 2859

2859 先進(jìn)封裝大部分是利用「晶圓廠」的技術(shù),直接在晶圓上進(jìn)行,由于這種技術(shù)更適合晶圓廠來(lái)做,因此臺(tái)積電大部分的先進(jìn)封裝都是自己做的。

2021-02-22 11:45:21 2200

2200

一項(xiàng)技術(shù)能從相對(duì)狹窄的專業(yè)領(lǐng)域變得廣為人知,有歷史的原因,也離不開著名公司的推波助瀾,把SiP帶給大眾的是蘋果(Apple),而先進(jìn)封裝能引起公眾廣泛關(guān)注則是因?yàn)榕_(tái)積電(TSMC)。 蘋果

2021-04-01 16:07:24 32556

32556

最近,先進(jìn)封裝技術(shù)在臺(tái)灣地區(qū)掀起了新一波熱潮,焦點(diǎn)企業(yè)是AMD和臺(tái)積電。 AMD宣布攜手臺(tái)積電,開發(fā)出了3D chiplet技術(shù),并且將于今年年底量產(chǎn)相應(yīng)芯片。AMD總裁兼CEO蘇姿豐表示,該封裝

2021-06-18 11:17:26 1999

1999 最近,關(guān)于臺(tái)積電的先進(jìn)封裝有很多討論,讓我們透過(guò)他們的財(cái)報(bào)和最新的技術(shù)峰會(huì)來(lái)對(duì)這家晶圓代工巨頭的封裝進(jìn)行深入的介紹。 資料顯示,在張忠謀于2011年重返公司之后,就下定決定要做先進(jìn)封裝。而1994

2021-06-18 16:11:50 3699

3699 在之前舉辦的Computex上,AMD發(fā)布了其實(shí)驗(yàn)性的產(chǎn)品,即基于3D Chiplet技術(shù)的3D V-Cache。該技術(shù)使用臺(tái)積電的3D Fabric先進(jìn)封裝技術(shù),成功地將包含有64MB L3

2021-06-21 17:56:57 3244

3244 先進(jìn)封裝技術(shù)FC/WLCSP的應(yīng)用與發(fā)展分析。

2022-05-06 15:19:12 24

24 端

子引出互連等 3 種先進(jìn)互連技術(shù)及其封裝工藝的優(yōu)缺點(diǎn),討論了功率電子模塊封裝及互連技術(shù)所面臨的問(wèn)題與挑戰(zhàn)。

2022-05-06 15:15:55 6

6 2021年對(duì)于先進(jìn)封裝行業(yè)來(lái)說(shuō)是豐收一年,現(xiàn)在包括5G、汽車信息娛樂/ADAS、人工智能、數(shù)據(jù)中心和可穿戴應(yīng)用在內(nèi)的大趨勢(shì)繼續(xù)迫使芯片向先進(jìn)封裝發(fā)展。2021年先進(jìn)封裝市場(chǎng)總收入為321億美元,預(yù)計(jì)

2022-06-13 14:01:24 2047

2047 通富微電、華天科技也表示已儲(chǔ)備Chiplet相關(guān)技術(shù)。Chiplet是先進(jìn)封裝技術(shù)之一,除此以外,先進(jìn)封裝概念股也受到市場(chǎng)關(guān)注。4連板大港股份表示已儲(chǔ)備TSV、micro-bumping(微凸點(diǎn))和RDL等先進(jìn)封裝核心技術(shù)。

2022-08-08 12:01:23 1048

1048 因此,該行業(yè)已轉(zhuǎn)向使用chiplet來(lái)組合更大的封裝,以繼續(xù)滿足計(jì)算需求。將芯片分解成許多chiplet并超過(guò)標(biāo)線限制(光刻工具的圖案化限制的物理限制)將實(shí)現(xiàn)持續(xù)縮放,但這種范例仍然存在問(wèn)題。即使

2022-08-24 09:46:33 1935

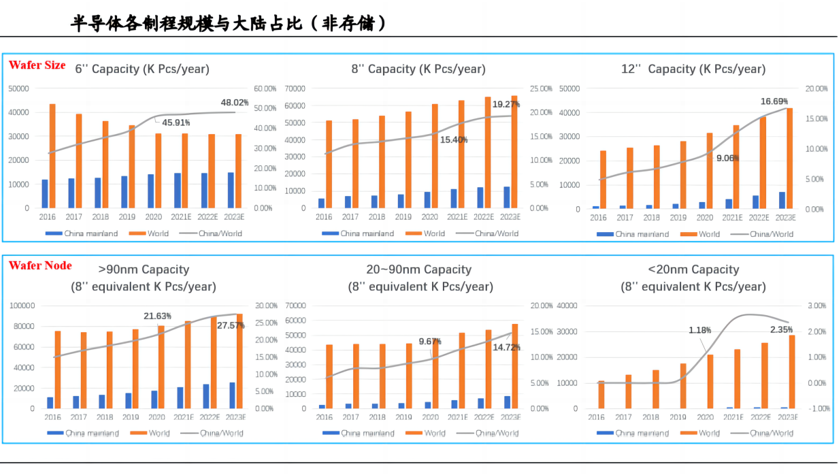

1935 墻”和“功能墻”)制約,以芯粒(Chiplet)異質(zhì)集成為核心的先進(jìn)封裝技術(shù),將成為集成電路發(fā)展的關(guān)鍵路徑和突破口。文章概述近年來(lái)國(guó)際上具有“里程碑”意義的先進(jìn)封裝技術(shù),闡述中國(guó)大陸先進(jìn)封裝領(lǐng)域發(fā)展的現(xiàn)狀與優(yōu)勢(shì),分析中國(guó)大陸先進(jìn)封裝關(guān)鍵技術(shù)與世界先進(jìn)水平的差距,最后對(duì)未來(lái)中國(guó)大陸先進(jìn)封裝發(fā)展提出建議。

2022-12-28 14:16:29 3295

3295 Chiplet 封裝領(lǐng)域,目前呈現(xiàn)出百花齊放的局面。Chiplet 的核心是實(shí)現(xiàn)芯片間的高速互 聯(lián),同時(shí)兼顧多芯片互聯(lián)后的重新布線。

2023-01-05 10:15:28 955

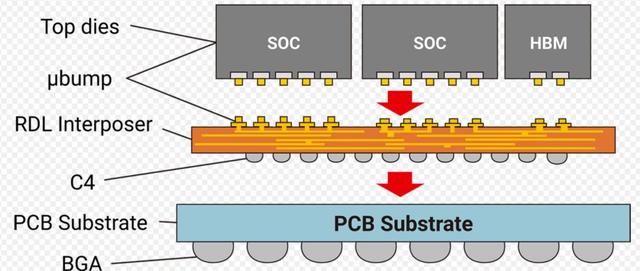

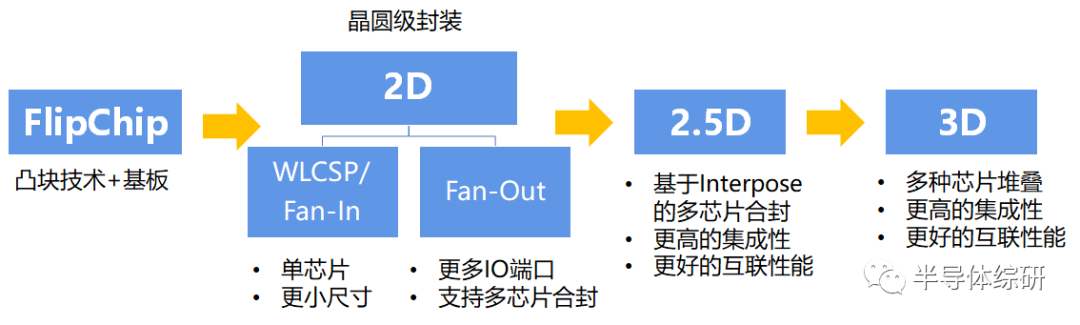

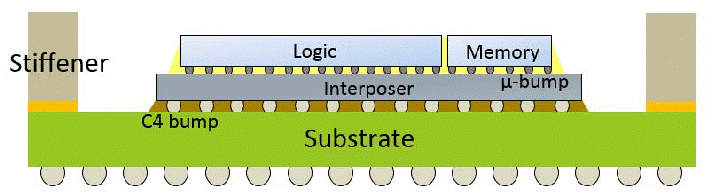

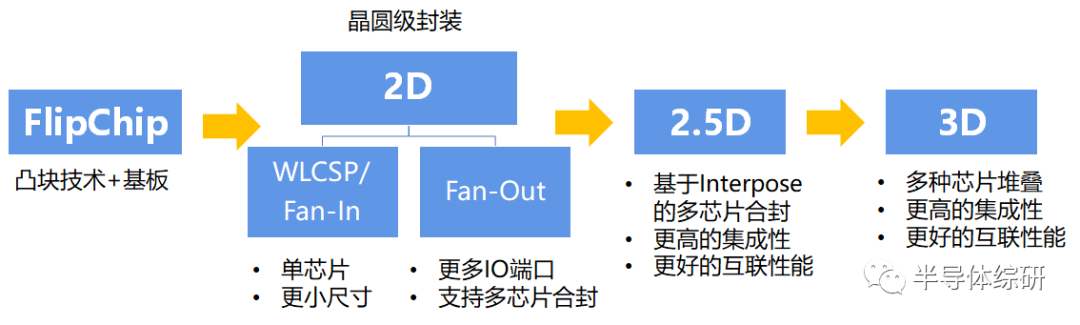

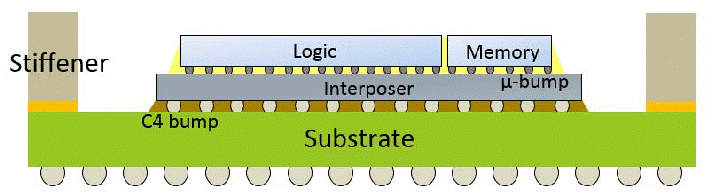

955 采用了先進(jìn)的設(shè)計(jì)思路和先進(jìn)的集成工藝、縮短引線互連長(zhǎng)度,對(duì)芯片進(jìn)行系統(tǒng)級(jí)封裝的重構(gòu),并且能有效提高系統(tǒng)功能密度的封裝。現(xiàn)階段的先進(jìn)封裝是指:倒裝焊(FlipChip)、晶圓級(jí)封裝(WLP)、2.5D封裝(Interposer、RDL)、3D封裝(TSV)

2023-01-13 10:58:41 1220

1220 隨著集成電路制程工藝逼近物理尺寸極限,2.5D/3D封裝,芯粒(Chiplet)、晶上系統(tǒng)(SoW)等先進(jìn)封裝成為了提高芯片集成度的新方向,并推動(dòng)EDA方法學(xué)創(chuàng)新。這也使得芯片設(shè)計(jì)不再是單芯片的問(wèn)題,而逐漸演變成多芯片系統(tǒng)工程。

2023-01-29 09:31:01 595

595 Promex Industries 首席執(zhí)行官 Dick Otte對(duì)先進(jìn)封裝中材料特性的未知數(shù)、對(duì)鍵合的影響,以及為什么環(huán)境因素在復(fù)雜的異質(zhì)封裝中如此重要等問(wèn)題進(jìn)行回答。以下是本次談話的節(jié)選。

2023-01-29 11:00:40 380

380 SiP是一個(gè)非常寬泛的概念,廣義上看,它囊括了幾乎所有多芯片封裝技術(shù),但就最先進(jìn)SiP封裝技術(shù)而言,主要包括 2.5D/3D Fan-out(扇出)、Embedded、2.5D/3D Integration,以及異構(gòu)Chiplet封裝技術(shù)。

2023-03-20 09:51:54 1037

1037

難以在全球化的先進(jìn)制程中分一杯羹,手機(jī)、HPC等需要先進(jìn)制程的芯片供應(yīng)受到嚴(yán)重阻礙,亟需另辟蹊徑。而先進(jìn)封裝/Chiplet等技術(shù),能夠一定程度彌補(bǔ)先進(jìn)制程的缺失,用面積和堆疊換取算力和性能。

2023-04-15 09:48:56 1953

1953 來(lái)源:Cadence楷登 2023年4月26日,楷登電子近日宣布基于臺(tái)積電 3nm(N3E)工藝技術(shù)的 Cadence? 16G UCIe? 2.5D 先進(jìn)封裝 IP 成功流片。該 IP 采用

2023-04-27 16:35:40 452

452

Chiplet即小芯片之意,指在晶圓端將原本一顆“大”芯片(Die)拆解成幾個(gè)“小”芯片(Die),因單個(gè)拆解后的“小”芯片在功能上是不完整的,需通過(guò)封裝,重新將各個(gè)“小”芯片組合起來(lái),功能上還原

2023-05-15 11:41:29 1457

1457

SiP系統(tǒng)級(jí)封裝(System in Package),先進(jìn)封裝HDAP(High Density Advanced Package),兩者都是當(dāng)今芯片封裝技術(shù)的熱點(diǎn),受到整個(gè)半導(dǎo)體產(chǎn)業(yè)鏈的高度關(guān)注

2023-05-19 09:54:26 1326

1326

臺(tái)積電對(duì)外傳內(nèi)部要擴(kuò)充CoWoS產(chǎn)能的傳言也相當(dāng)?shù)驼{(diào),以“不評(píng)論市場(chǎng)傳聞”回應(yīng),并強(qiáng)調(diào)公司今年4月時(shí)于法說(shuō)會(huì)中提及,關(guān)于先進(jìn)封裝產(chǎn)能的擴(kuò)充(包括CoWoS)均仍在評(píng)估中,目前沒有更新回應(yīng),間接證實(shí)公司短期內(nèi)暫無(wú)擴(kuò)產(chǎn)動(dòng)作。

2023-06-08 14:27:11 643

643 先進(jìn)封裝是對(duì)應(yīng)于先進(jìn)圓晶制程而衍生出來(lái)的概念,一般指將不同系統(tǒng)集成到同一封裝內(nèi)以實(shí)現(xiàn)更高效系統(tǒng)效率的封裝技術(shù)。

2023-06-13 11:33:24 282

282

一、核心結(jié)論 ?1、先進(jìn)制程受限,先進(jìn)封裝/Chiplet提升算力,必有取舍。在技術(shù)可獲得的前提下,提升芯片性能,先進(jìn)制程升級(jí)是首選,先進(jìn)封裝則錦上添花。 2、大功耗、高算力的場(chǎng)景,先進(jìn)封裝

2023-06-13 11:38:05 747

747

隨著摩爾定律的放緩以及前沿節(jié)點(diǎn)復(fù)雜性和成本的增加,先進(jìn)封裝正在成為將多個(gè)裸片集成到單個(gè)封裝中的關(guān)鍵解決方案,并有可能結(jié)合成熟和先進(jìn)的節(jié)點(diǎn)。

2023-06-16 17:50:09 340

340

Fab 6 是臺(tái)積電首個(gè)一體式先進(jìn)封裝測(cè)試工廠,是臺(tái)積電不斷增加的封裝投資的一部分。該晶圓廠已準(zhǔn)備好量產(chǎn)臺(tái)積電 SoIC 封裝技術(shù)。請(qǐng)記住,當(dāng)臺(tái)積電說(shuō)量產(chǎn)時(shí),他們指的是 Apple iPhone 尺寸的量產(chǎn),而不是工程樣品或內(nèi)部產(chǎn)品。

2023-06-19 11:25:56 219

219

緊密相連。在業(yè)界,先進(jìn)封裝技術(shù)與傳統(tǒng)封裝技術(shù)以是否焊線來(lái)區(qū)分。先進(jìn)封裝技術(shù)包括FCBGA、FCQFN、2.5D/3D、WLCSP、Fan-Out等非焊線形式。先進(jìn)

2022-04-08 16:31:15 641

641

先進(jìn)的半導(dǎo)體封裝既不是常規(guī)操作,目前成本也是相當(dāng)高的。但如果可以實(shí)現(xiàn)規(guī)模化,那么該行業(yè)可能會(huì)觸發(fā)一場(chǎng)chiplet革命,使IP供應(yīng)商可以銷售芯片,顛覆半導(dǎo)體供應(yīng)鏈。

2023-06-21 08:56:39 190

190 Chiplet俗稱“芯粒”或“小芯片組”,通過(guò)將原來(lái)集成于同一 SoC 中的各個(gè)元件分拆,獨(dú)立 為多個(gè)具特定功能的 Chiplet,分開制造后再通過(guò)先進(jìn)封裝技術(shù)將彼此互聯(lián),最終集成封裝 為一個(gè)系統(tǒng)芯片。

2023-06-25 15:12:20 1345

1345

組合成為特定功能的大系統(tǒng)。那么半導(dǎo)體Chiplet技術(shù)分別有哪些優(yōu)點(diǎn)和缺點(diǎn)呢? 一、核心結(jié)論 1. 先進(jìn)制程受限,先進(jìn)封裝/Chiplet提升算力,必有取舍。 在技術(shù)可獲得的前提下,提升芯片性能,先進(jìn)制程升級(jí)是首選,先進(jìn)封裝則錦上添花。 2. 大功耗、高算

2023-06-25 16:35:15 1686

1686

在異質(zhì)異構(gòu)的世界里,chiplet是“生產(chǎn)關(guān)系”,是決定如何拆分及組合芯粒的方式與規(guī)則;先進(jìn)封裝技術(shù)是“生產(chǎn)力”,通過(guò)堆疊、拼接等方法實(shí)現(xiàn)不同芯粒的互連。先進(jìn)封裝技術(shù)已成為實(shí)現(xiàn)異質(zhì)異構(gòu)的重要前提。

2023-06-26 17:14:57 601

601 Chiplet 俗稱“芯粒”或“小芯片組”,通過(guò)將原來(lái)集成于同一 SoC 中的各個(gè)元件分拆,獨(dú)立 為多個(gè)具特定功能的 Chiplet,分開制造后再通過(guò)先進(jìn)封裝技術(shù)將彼此互聯(lián),最終集成封裝 為一個(gè)系統(tǒng)芯片。

2023-07-04 10:23:22 630

630

AI訂單激增,影響傳至先進(jìn)封裝市場(chǎng)。

2023-07-05 18:19:37 776

776

Chiplet,就是小芯片/芯粒,是通過(guò)將原來(lái)集成于同一系統(tǒng)單晶片中的各個(gè)元件分拆,獨(dú)立為多個(gè)具特定功能的Chiplet,分開制造后再透過(guò)先進(jìn)封裝技術(shù)將彼此互聯(lián),最終集成封裝為一系統(tǒng)晶片組。

2023-07-06 11:28:23 522

522

提及先進(jìn)封裝,臺(tái)積電的CoWoS和InFO、三星的X-Cube以及英特爾的EMIB等晶圓級(jí)封裝是如今最為人所熟知的方案。在Chiplet熱潮的帶動(dòng)下,這些晶圓級(jí)封裝技術(shù)扶持著逼近極限的摩爾定律繼續(xù)向前,巨大的市場(chǎng)機(jī)遇面前,傳統(tǒng)的封測(cè)廠商也開始鉆研晶圓級(jí)技術(shù),意圖分一杯羹。

2023-07-11 16:19:09 443

443 Chiplet技術(shù)是一種利用先進(jìn)封裝方法將不同工藝/功能的芯片進(jìn)行異質(zhì)集成的技術(shù)。這種技術(shù)設(shè)計(jì)的核心思想是先分后合,即先將單芯片中的功能塊拆分出來(lái),再通過(guò)先進(jìn)封裝模塊將其集成為大的單芯片。

2023-07-17 09:21:50 2309

2309

根據(jù) LexisNexis 的數(shù)據(jù),中國(guó)臺(tái)灣芯片制造商臺(tái)積電開發(fā)了最廣泛的先進(jìn)芯片封裝專利庫(kù),其次是三星電子和英特爾。

2023-08-03 17:27:17 1067

1067 level package),2.5D封裝(interposer,RDL等),3D封裝(TSV)等先進(jìn)封裝技術(shù)。

2023-08-05 09:54:29 398

398

先進(jìn)封裝處于晶圓制造與封測(cè)制程中的交叉區(qū)域,涉及IDM、晶圓代工、封測(cè)廠商,市場(chǎng)格局較為集中,前6 大廠商份額合計(jì)超過(guò)80%。全球主要的 6 家廠商,包括 2 家 IDM 廠商(英特爾、三星),一家

2023-08-11 09:11:48 456

456

半導(dǎo)體器件有許多封裝形式,按封裝的外形、尺寸、結(jié)構(gòu)分類可分為引腳插入型、表面貼裝型和高級(jí)封裝三類。從DIP、SOP、QFP、PGA、BGA到CSP再到SIP,技術(shù)指標(biāo)一代比一代先進(jìn)。

2023-08-11 09:43:43 1796

1796

半導(dǎo)體器件有許多封裝形式,按封裝的外形、尺寸、結(jié)構(gòu)分類可分為引腳插入型、表面貼裝型和高級(jí)封裝三類。從DIP、SOP、QFP、PGA、BGA到CSP再到SIP,技術(shù)指標(biāo)一代比一代先進(jìn)。

2023-08-14 09:59:17 1086

1086

面對(duì)人工智能相關(guān)需求的激增,臺(tái)積電已無(wú)法滿足先進(jìn)封裝服務(wù)的需求,并一直在快速擴(kuò)大產(chǎn)能,其中包括在臺(tái)灣投資近 900 億新臺(tái)幣(28.1 億美元)的新工廠。

2023-09-20 17:31:00 669

669 先進(jìn)封裝增速高于整體封裝,將成為全球封裝市場(chǎng)主要增量。根據(jù)Yole的數(shù)據(jù),全球封裝市場(chǎng)規(guī)模穩(wěn)步增長(zhǎng),2021 年全球封裝 市場(chǎng)規(guī)模 約達(dá) 777 億美元。其中,先進(jìn)封裝全球市場(chǎng)規(guī)模約 350 億美元,占比約 45%, 2025 年,先進(jìn)封裝在全部封裝市場(chǎng)的 占比將增長(zhǎng)至 49.4%。

2023-09-22 10:43:18 1189

1189

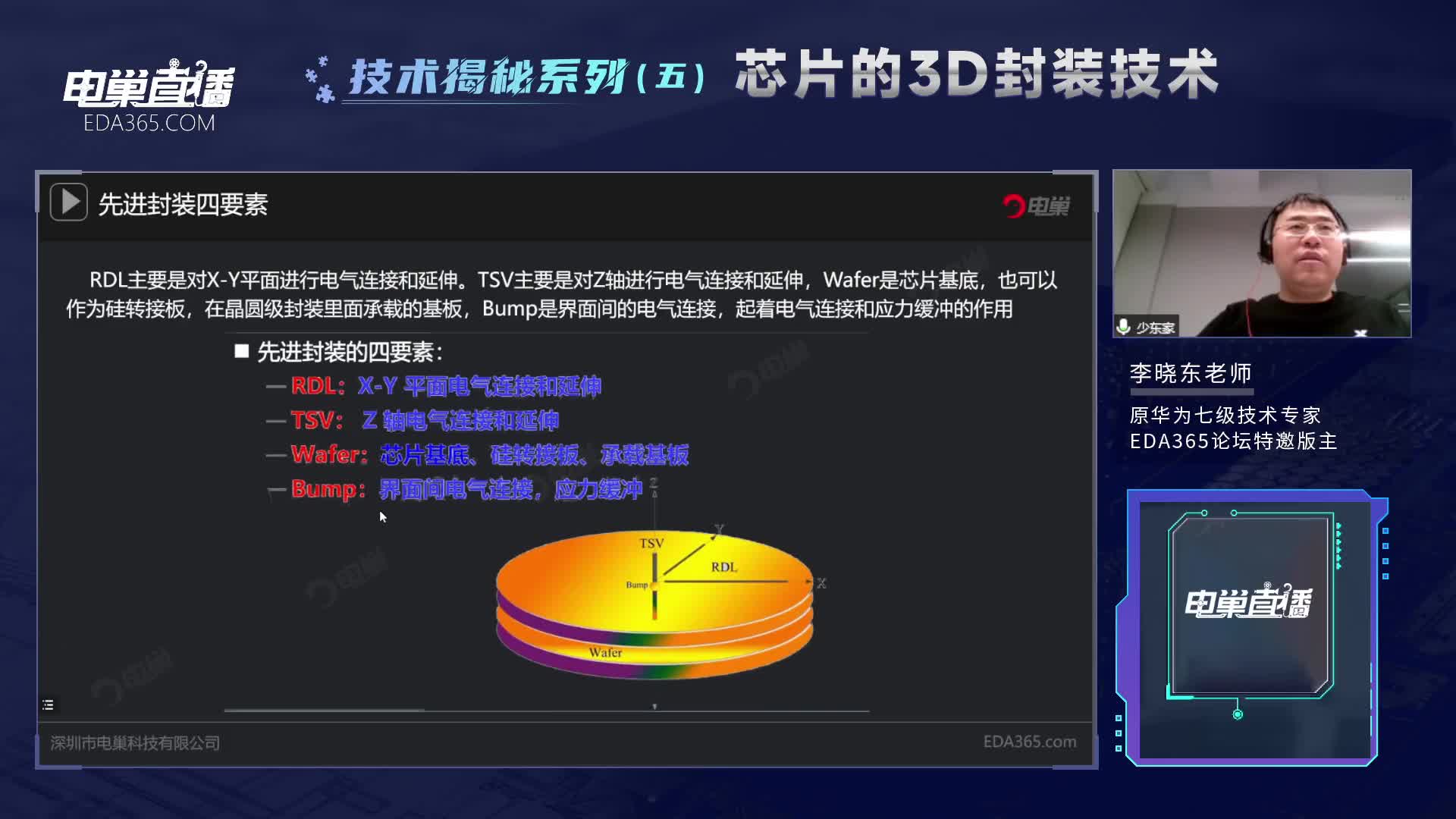

先進(jìn)封裝技術(shù)以SiP、WLP、2.5D/3D為三大發(fā)展重點(diǎn)。先進(jìn)封裝核心技術(shù)包括Bumping凸點(diǎn)、RDL重布線、硅中介層和TSV通孔等,依托這些技術(shù)的組合各廠商發(fā)展出了滿足多樣化需求的封裝解決方案,SiP系統(tǒng)級(jí)封裝、WLP晶圓級(jí)封裝、2.5D/3D封裝為三大發(fā)展重點(diǎn)。

2023-09-28 15:29:37 1614

1614

Chiplet主流封裝技術(shù)都有哪些?? 隨著處理器和芯片設(shè)計(jì)的發(fā)展,芯片的封裝技術(shù)也在不斷地更新和改進(jìn)。Chiplet是一種新型的封裝技術(shù),它可以將不同的芯片功能模塊制造在不同的芯片中,并通過(guò)

2023-09-28 16:41:00 1347

1347 此時(shí)先進(jìn)封裝開始嶄露頭角,以蘋果和臺(tái)積電為代表,開啟了一場(chǎng)新的革命,其主要分為兩大類,一種是基于XY平面延伸的先進(jìn)封裝技術(shù),主要通過(guò)RDL進(jìn)行信號(hào)的延伸和互連;第二種則是基于Z軸延伸的先進(jìn)封裝技術(shù),主要通過(guò)TSV進(jìn)行信號(hào)延伸和互連。

2023-10-10 17:04:30 573

573

半導(dǎo)體產(chǎn)品在由二維向三維發(fā)展,從技術(shù)發(fā)展方向半導(dǎo)體產(chǎn)品出現(xiàn)了系統(tǒng)級(jí)封裝(SiP)等新的封裝方式,從技術(shù)實(shí)現(xiàn)方法出現(xiàn)了倒裝(FlipChip),凸塊(Bumping),晶圓級(jí)封裝(Waferlevelpackage),2.5D封裝(interposer,RDL等),3D封裝(TSV)等先進(jìn)封裝技術(shù)。

2023-10-31 09:16:29 836

836

我們?yōu)槭裁葱枰私庖恍?b class="flag-6" style="color: red">先進(jìn)封裝?

2023-11-23 16:32:06 281

281

先進(jìn)封裝基本術(shù)語(yǔ)

2023-11-24 14:53:10 362

362

相比于晶圓制造,中國(guó)大陸封測(cè)環(huán)節(jié)較為成熟,占據(jù)全球封測(cè)接近40%的份額,但中國(guó)大陸先進(jìn)封裝的滲透率較低,2022年僅為14%,低于全球45%的滲透率。在制程工藝受到外部制裁的背景下

2023-11-25 15:44:25 740

740 、主流技術(shù)和應(yīng)用場(chǎng)景,以及面臨的挑戰(zhàn)和問(wèn)題。進(jìn)而提出采用Chiplet技術(shù),將不同的功能模塊獨(dú)立集成為獨(dú)立的Chiplet,并融合在一個(gè)AI芯片上,從而實(shí)現(xiàn)更高的計(jì)算能力。該設(shè)計(jì)不僅允許獨(dú)立開發(fā)和升級(jí)各個(gè)模塊,還可在封裝過(guò)程中將它們巧妙組合起

2023-12-08 10:28:07 281

281

先進(jìn)的封裝技術(shù)可以將多個(gè)半導(dǎo)體芯片和組件集成到高性能的系統(tǒng)中。隨著摩爾定律的縮小趨勢(shì)面臨極限,先進(jìn)封裝為持續(xù)改善計(jì)算性能、節(jié)能和功能提供了一條途徑。但是,與亞洲相比,美國(guó)目前在先進(jìn)封裝技術(shù)方面落后

2023-12-14 10:27:14 383

383

作為全球領(lǐng)先的芯片封測(cè)企業(yè),長(zhǎng)電科技深刻理解先進(jìn)的封裝設(shè)計(jì)能力對(duì)于確保半導(dǎo)體行業(yè)的產(chǎn)品性能、功能和成本至關(guān)重要。大規(guī)模高密度的集成電路為產(chǎn)品設(shè)計(jì)提供了極大的靈活性。例如Chiplet等前沿技術(shù)包含

2023-12-18 11:11:46 390

390 中國(guó)半導(dǎo)體行業(yè)協(xié)會(huì)副秘書長(zhǎng)兼封測(cè)分會(huì)秘書長(zhǎng)徐冬梅受邀出席大會(huì)并致辭,她表示,本次大會(huì)立足本土、協(xié)同全球,重點(diǎn)關(guān)注異構(gòu)集成Chiplet技術(shù)、先進(jìn)封裝與SiP的最新進(jìn)展,聚焦于HPC、AI、汽車等關(guān)鍵應(yīng)用領(lǐng)域,是Chiplet生態(tài)圈的一次重要聚會(huì)。

2023-12-29 16:36:34 311

311 組件。這種技術(shù)的核心思想是將大型集成電路拆分成更小、更模塊化的部分,以便更靈活地設(shè)計(jì)、制造和組裝芯片。Chiplet技術(shù)可以突破單芯片光刻面積的瓶頸,減少對(duì)先進(jìn)工藝制程的依賴,提高芯片的性能并降低制造成本。

2024-01-08 09:22:08 656

656 芯片的先進(jìn)封裝是一種超越摩爾定律的重要技術(shù),它可以提供更好的兼容性和更高的連接密度,使得系統(tǒng)集成度的提高不再局限于同一顆芯片。

2024-01-16 14:53:51 302

302 level package),2.5D封裝(interposer,RDL等),3D封裝(TSV)等先進(jìn)封裝技術(shù)。 審核編輯 黃宇

2024-02-21 10:34:20 178

178

因?yàn)锳I芯片需求的大爆發(fā),臺(tái)積電先進(jìn)封裝產(chǎn)能供不應(yīng)求,而且產(chǎn)能供不應(yīng)求的狀況可能延續(xù)到2025年;這是臺(tái)積電總裁魏哲家在法人說(shuō)明會(huì)上透露的。 而且臺(tái)積電一直持續(xù)的擴(kuò)張先進(jìn)封裝產(chǎn)能,但是依然不能滿足AI的強(qiáng)勁需求;這在一定程度會(huì)使得其他相關(guān)封裝廠商因?yàn)榻邮苻D(zhuǎn)單而受益。

2024-01-22 18:48:08 565

565 )和集成電路的飛速發(fā)展,人工智能芯片逐漸成為全球科技競(jìng)爭(zhēng)的焦點(diǎn)。在后摩爾時(shí)代,AI 芯片的算力提升和功耗降低越來(lái)越依靠具有硅通孔、微凸點(diǎn)、異構(gòu)集成、Chiplet等技術(shù)特點(diǎn)的先進(jìn)封裝技術(shù)。從 AI 芯片的分類與特點(diǎn)出發(fā),對(duì)國(guó)內(nèi)外典型先進(jìn)封裝技術(shù)

2024-03-04 18:19:18 582

582

臺(tái)積電計(jì)劃在嘉義科學(xué)園區(qū)投資超過(guò)5000億元新臺(tái)幣,建設(shè)六座先進(jìn)封裝廠,這一舉措無(wú)疑將對(duì)半導(dǎo)體產(chǎn)業(yè)產(chǎn)生深遠(yuǎn)影響。

2024-03-20 11:28:14 335

335 Bump Metrology system—BOKI_1000在半導(dǎo)體行業(yè)中,Bump、RDL、TSV、Wafer合稱先進(jìn)封裝的四要素,其中Bump起著界面互聯(lián)和應(yīng)力緩沖的作用。Bump是一種金屬凸

2023-09-06 14:26:09

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論