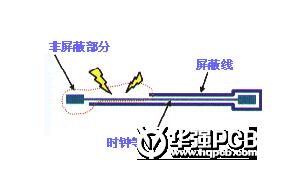

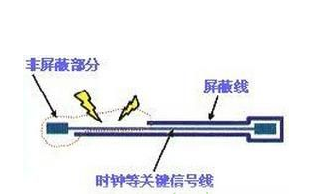

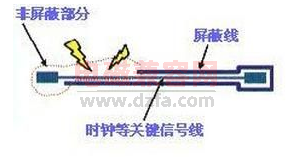

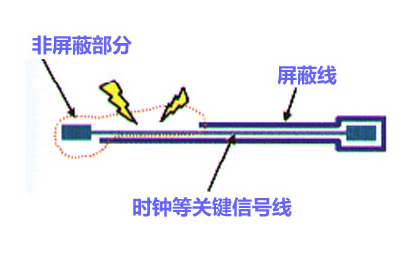

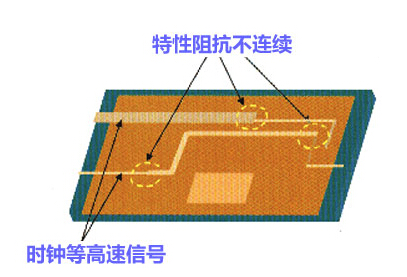

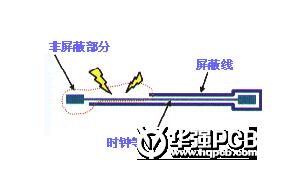

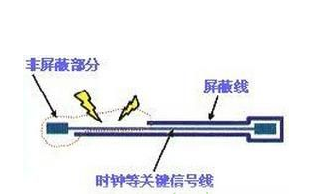

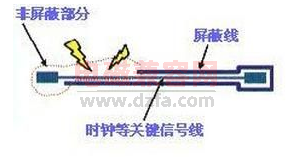

在高速的PCB設計中,時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。##在高速的PCB設計中,時鐘等關鍵

2016-04-26 14:00:01 5104

5104

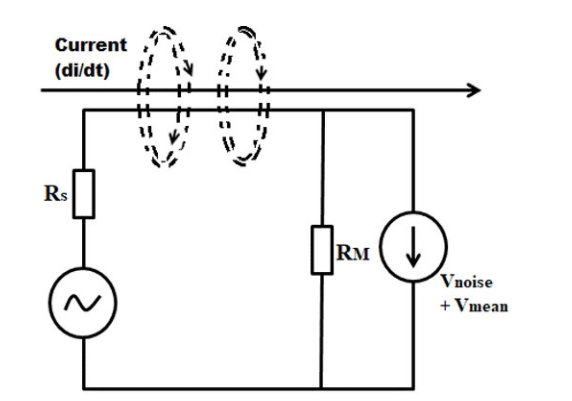

前面我們分析了EMI的產生情況,這節里我們將針對高速PCB設計,來分析如何進行EMI控制。

2012-03-31 11:07:14 1590

1590 隨著信號上升沿時間的減小及信號頻率的提高,電子產品的EMI問題越來越受到電子工程師的關注,幾乎60%的EMI問題都可以通過高速PCB來解決

2015-09-05 14:29:00 1691

1691

隨著信號上升沿時間的減小及信號頻率的提高,電子產品的EMI問題越來越受到電子工程師的關注,幾乎60%的EMI問題都可以通過高速PCB來解決。以下是高速PCB設計抗EMI干擾的九大規則: 規則一:高速

2018-04-13 08:20:00 1567

1567

本文主要詳解PCB設計高速模擬輸入信號走線,首先介紹了PCB設計高速模擬輸入信號走線方法,其次闡述了九大關于PCB設計高速模擬輸入信號走線規則,具體的跟隨小編一起來了解一下。

2018-05-25 09:06:44 8394

8394

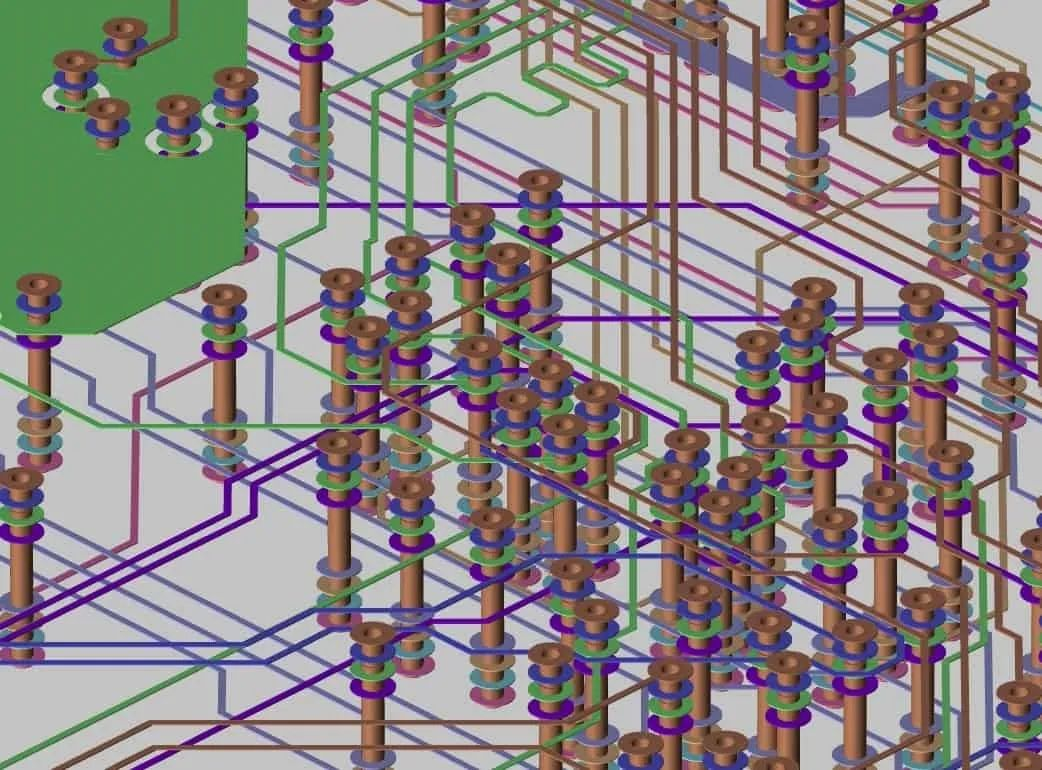

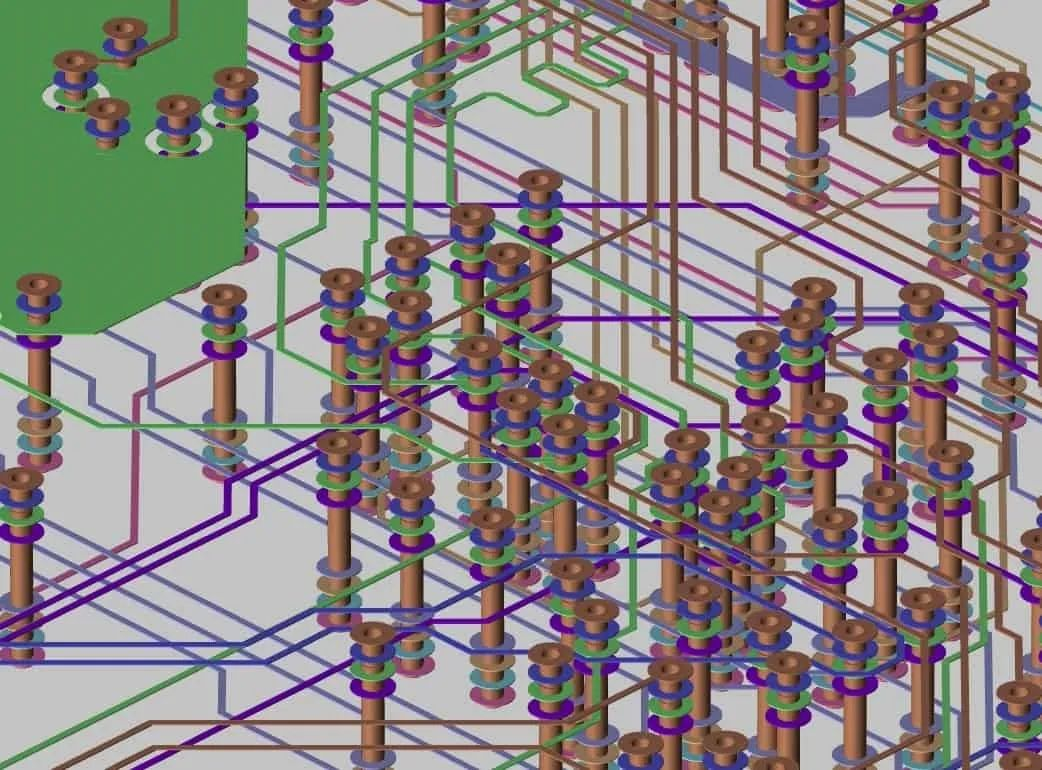

告訴大家在進行多層高速PCB設計過程中會遇到哪些坑,應該遵循哪些規則,應該使用什么樣的套路,最后讓大家不再談高速PCB而色變。

2019-10-24 09:35:50 0

0 隨著信號上升沿時間的減小及信號頻率的提高,電子產品的EMI問題越來越受到電子工程師的關注,幾乎60%的EMI問題都可以通過高速PCB來解決。

2022-11-04 10:10:41 708

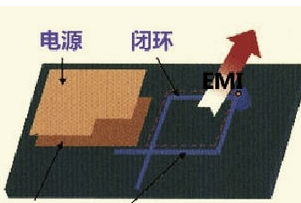

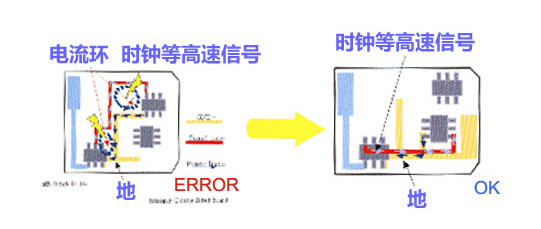

708 規則一:高速信號走線屏蔽規則在高速的PCB設計中,時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。圖1 高速

2018-11-28 11:14:18

、高速信號走線屏蔽規則如上圖所示:在高速的PCB設計中,時鐘等關鍵的高速信號線,則需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都是會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。2...

2021-12-31 06:22:08

@[TOC]PCB設計經驗(1)#PCB設計規則#PCB走線經驗#快捷鍵的使用#易犯錯誤匯總

2021-11-10 08:19:25

請問PCB設計規則怎樣設置?怎樣設置PCB的電氣規則檢查?比如說線寬,焊盤間的距離,線與線之間的間距,焊盤與線之間的間距怎樣定義設置?

2016-08-13 16:57:56

PCB設計規則你知幾何,20個PCB設計規則送給你。

2021-11-11 07:16:18

EMI問題是很多工程師在PCB設計遇到的最大挑戰,由于電子產品信號處理頻率越來越高,EMI問題日益顯著,雖然有很多書籍對EMI問題進行了探討,但是都不夠深入,《PCB設計中EMI控制原理與實戰

2011-05-19 15:58:44

結構,PCB介質層的電介質特性和介電常數以及每一布線層的電氣特性。現在已經有了抑制電子設備和儀表的EMI的國際標準,統稱為電磁兼容(EMC)標準,它們可以作為PCB設計者布線和布局時抑制電磁輻射和干擾

2014-12-22 11:52:49

,它不僅完成了導通孔的作用,還省出許多布線通道使布線過程完成得更加方便,更加流暢,更為完善,PCB 板的設計過程是一個復雜而又簡單的過程,要想很好地掌握它,還需廣大電子工程設計人員去自已體會,才能得到其中的真諦。那么大家還知道PCB設計中,有哪些布線規則嗎?掌握好規則是最重要的準備。

2019-08-01 08:04:25

PCB設計流程PCB規則設置設計規則的單位跟隨畫布屬性里設置的單位,此處單位是mil。導線線寬最小為10mil;不同網絡元素之間最小間距為8mil;孔外徑為24mil,孔內徑為12mil;線長不做

2022-01-11 06:14:06

PCB設計是指印制電路板設計。印制電路板的設計是以電路原理圖為根據,實現電路設計者所需要的功能。印刷電路板的設計主要指版圖設計,需要考慮外部連接的布局、內部電子元件的優化布局、金屬連線和通孔的優化

2017-06-03 16:55:26

PCB設計走線的規則是什么

2021-03-17 06:36:28

PCB設計解決EMI問題的九大規則 隨著信號上升沿時間的減小,信號頻率的提高,電子產品的EMI問題,也來越受到電子工程師的光注。高速PCB設計的成功,對EMI的貢獻越來越受到重視,幾乎60%的EMI問題可以

2022-04-18 15:22:08

的設計常常注意電路板的視覺效果,現在不一樣了。自動設計的電路板不比手動設計的美觀,但在電子特性上能滿足規定的要求,而且設計的完整性能得到保證。二:高速PCB設計解決EMI問題的九大規則隨著信號上升沿

2021-03-31 06:00:00

高速PCB設計系列課:入門篇:林超文PCB設計PADS和OrCAD實操指南http://t.elecfans.com/topic/22.html?elecfans_trackid=bbspost

2015-05-05 09:30:27

隨著信號上升沿時間的減小及信號頻率的提高,電子產品的EMI問題越來越受到電子工程師的關注,幾乎60%的EMI問題都可以通過高速PCB來解決。

2023-09-25 08:04:42

隨著信號上升沿時間的減小及信號頻率的提高,電子產品的EMI問題越來越受到電子工程師的關注,幾乎60%的EMI問題都可以通過高速PCB來解決。以下是九大規則:

2019-07-25 06:56:17

`請問高速PCB設計規則有哪些?`

2020-02-25 16:07:38

高速PCB設計之一 何為高速PCB設計電子產品的高速化、高密化,給PCB設計工程師帶來新的挑戰。PCB設計不再是產品硬件開發的附屬,而成為產品硬件開發中“前端IC,后端PCB,SE集成”3個環節中

2014-10-21 09:41:25

`請問高速PCB設計前期的準備工作有哪些?`

2020-04-08 16:32:20

。 問:在高速PCB設計中,串擾與信號線的速率、走線的方向等有什么關系?需要注意哪些設計指標來避免出現串擾等問題? 答:串擾會影響邊沿速率,一般來說,一組總線傳輸方向相同時,串擾因素會使邊沿速率變慢

2019-01-11 10:55:05

本帖最后由 eehome 于 2013-1-5 09:53 編輯

高速PCB設計已成為數字系統設計中的主流技術,PCB的設計質量直接關系到系統性能的好壞乃至系統功能的實現。針對高速PCB

2012-03-31 14:29:39

隨著信號上升沿時間的減小及信號頻率的提高,電子產品的EMI問題越來越受到電子工程師的關注,幾乎60%的EMI問題都可以通過高速PCB來解決。以下是九大規則: 高速PCB設計解決EMI問題的九大規則

2016-01-19 22:50:31

上一期我們介紹了高速PCB設計軟件allegro16.6差分信號的設定在高速PCB布線前需要對差分信號的規則進行設置因此本期重點介紹在電氣規則和物理規則下是如何建立差分信號的規則1、在電氣規則下建立

2017-01-06 09:46:41

高速PCB設計指南之(一~八 )目錄2001/11/21CHENZHI/LEGENDSILICON一、1、PCB布線2、PCB布局3、高速PCB設計二、1、高密度(HD)電路設計2、抗干擾技術3

2012-07-13 16:18:40

在高速PCB設計中,過孔有哪些注意事項?

2021-04-25 09:55:24

圖解在高速的PCB設計中的走線規則

2021-03-17 07:53:30

高速PCB設計的基本內容是什么高速PCB的設計方法是什么

2021-04-27 06:33:07

如何在PCB設計階段處理好EMC及其EMI的問題呢?有什么解決辦法嗎?

2023-04-06 15:52:59

解決高速PCB設計信號問題的全新方法

2021-04-25 07:56:35

的特殊疊層結構特性阻抗的控制

射頻PCB與數模混合類PCB的布線規則和技巧射頻PCB與數模混合類PCB布線完成后的收尾處理PCB板級的ESD處理方法和技巧

PCB板級的EMC/EMI處理方法和技巧PCB中的DFM 設計

FPC柔性PCB設計設計規范的必要性

2023-09-27 07:54:33

EMI的輻射干擾是PCB設計中的一大關鍵,更別說是高速PCB的設計了。而關于EMI的產生理論上工程師應該都是很清楚的,并且也都知道一些普遍的關于抑制EMI的手段和方式。這里將為大家分享的是針對高速

2019-05-20 08:30:00

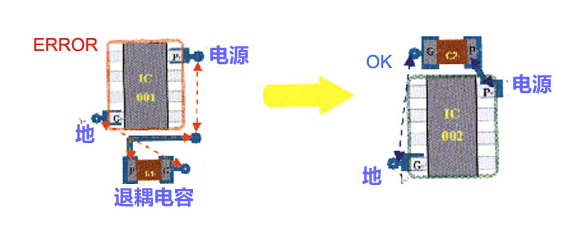

的進行干擾抑制呢?規則一:高速信號走線屏蔽規則在高速的PCB設計中,時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔

2016-07-07 15:52:45

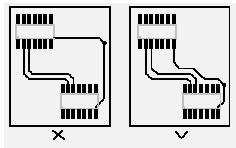

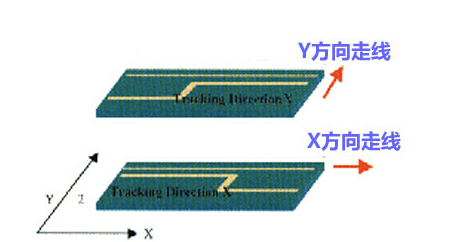

的連續,否則會增加EMI的輻射。也就是說,同層的布線的寬度必須連續,不同層的走線阻抗必須連續。 圖4 特性阻抗連續規則 規則五:高速PCB設計的布線方向規則 相鄰兩層間的走線必須遵循垂直走線的原則

2018-09-20 10:38:01

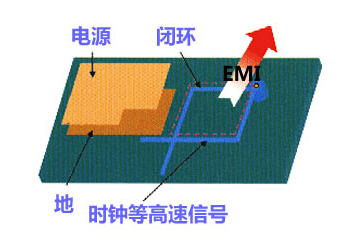

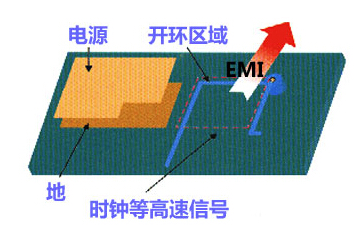

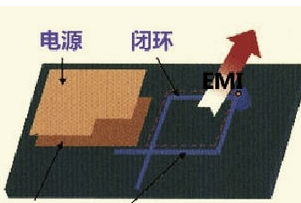

的PCB設計中,時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。規則二:高速信號的走線閉環規則由于PCB板的密度越來越高

2017-11-02 12:11:12

什么是高速pcb設計高速線總體規則是什么?

2019-06-13 02:32:06

高速PCB設計指南之(一~八 )目錄 2001/11/21 一、1、PCB布線2、PCB布局3、高速PCB設計

二、1、高密度(HD)電路設計2、抗干擾技術

2008-08-04 14:14:42 0

0 高速PCB設計的疊層問題

2009-05-16 20:06:45 0

0 PCB設計中20H規則的驗證方法:隨著電路工作頻率的上升,PCB設計面臨越來越多的電磁輻射問題。20H規則是減小電路板輻射的設計規則之一。

2009-09-26 08:30:43 0

0 PCB設計時應該遵循的規則

1) 地線回路規則:

環路最小

2007-12-12 14:48:15 1096

1096

高速PCB設計時應從哪些方面考慮EMC、EMI的規則

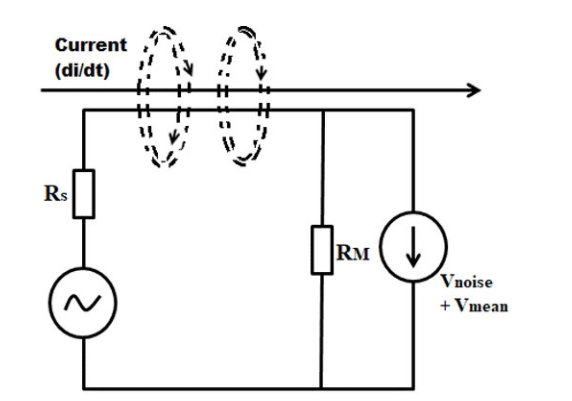

一般EMI/EMC 設計時需要同時考慮輻射(radiated)與傳導(conducted)兩個方面,前者歸屬于頻率較高的

2009-03-20 14:05:36 1360

1360 高速信號走線規則教程

隨著信號上升沿時間的減小,信號頻率的提高,電子產品的EMI問題,也來越受到電子工程師的關注。高速PCB設計的成功,對EMI

2009-04-15 08:49:27 2798

2798

高速PCB設計指南之八

第一篇 掌握IC封裝的特性以達到最佳EMI抑制性能

將去耦電容直接放在IC封裝內可以

2009-11-11 15:07:54 464

464 編寫PCB設計規則檢查器技巧

本文闡述了一種編寫PCB設計規則檢查器(DRC)系統方法。利用電路圖生成工具得到PCB設計后,即可運

2009-11-17 14:03:10 1019

1019 編寫屬于自己的PCB設計規則檢查器

編寫屬于自己的PCB設計規則檢查器具有很多優點,盡管設計檢查器并不那么簡單,但也并非高不可攀,因為任何熟悉現有編程或腳本

2009-12-27 13:31:01 811

811

目前,EMI問題是很多工程師在PCB設計遇到的最大挑戰,由于電子產品信號處理頻率越來越高,EMI問題日益顯著,雖然有很多書籍對EMI問題進行了探討,但是都不夠深入,《PCB設計中EMI控

2011-09-05 14:29:17 0

0 簡要闡述了高速PCB設計的主要內容, 并結合Cadence軟件介紹其解決方案比較了傳統高速設計方法與以Cadence為代表的現代高速PCB設計方法的主要差異指出在進行高速設計過程中必須借助于

2011-11-21 16:53:58 0

0 理論研究和實踐都表明,對高速電子系統而言,成功的PCB設計是解決系統EMC問題的重要措施之一.為了滿足EMC標準的要求,高速PCB設計正面臨新的挑戰,在高速PCB設計中,設計者需要糾正或放棄

2011-11-23 10:25:41 0

0 高速PCB設計指南.........................

2016-05-09 15:22:31 0

0 高速PCB設計指南............................

2016-05-09 15:22:31 0

0 EMI相關PCB布局布線規則,感興趣的小伙伴們可以看看。

2016-07-26 15:18:26 0

0 高速PCB設計指南,好資料,又需要的下來看看

2017-01-12 12:18:20 0

0 如何快速解決PCB設計EMI問題

2017-01-14 12:48:43 0

0 高速PCB設計電容的應用

2017-01-28 21:32:49 0

0 高速PCB設計規則 1)、線與線,線與元件焊盤,線與貫通孔,元件焊盤與貫通孔,貫通孔與貫通孔之間的距離是否合理,是否滿足生產要求。 (2)、電源線和地線的寬度是否合適,電源與地線之間是否緊耦合

2017-09-26 16:04:33 0

0 規則一:高速信號走線屏蔽規則 在高速的PCB設計中,時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有

2017-11-25 07:43:00 7511

7511

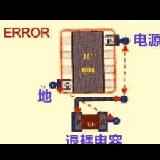

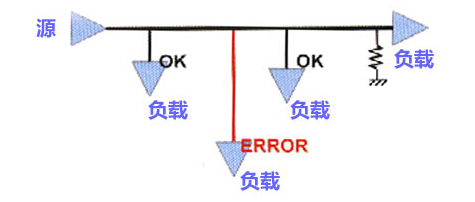

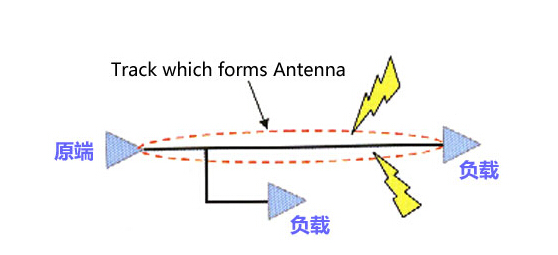

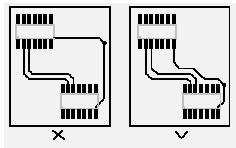

規則 由于PCB的密度越來越高,很多PCBlayout工程師在走線的過程中,很容易出現這樣的失誤,如圖2所示。 圖2 時鐘信號等高速信號網絡,在多層的PCB走線的時候產生了閉環現象,這種閉環現象會產生環形天線,增加EMI的輻射強度。 規則三、高速信號的走線開

2018-09-12 09:10:01 1157

1157 在高速的PCB設計中,時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。

2019-03-15 14:05:42 4494

4494

隨著,信號上升沿時間的減小,信號頻率的提高,電子產品的EMI問題,也來越受到電子工程師的光注。高速PCB設計的成功,對EMI的貢獻越來越受到重視,幾乎60%的EMI問題可以通過高速PCB來控制解決。

2019-06-05 14:56:36 587

587

在高速的PCB設計中,時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。

2019-05-06 18:08:15 3981

3981 低EMI DC/DC變換器PCB設計

2020-02-04 15:26:08 3835

3835 規則一:高速信號走線屏蔽規則 如上圖所示: 在高速的PCB設計中,時鐘等關鍵的高速信號線,走需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都是會造成EMI的泄漏。 建議屏蔽線,每1000mil,打孔

2020-02-14 11:53:40 11780

11780 隨著信號上升沿時間的減小,信號頻率的提高,電子產品的EMI問題,也來越受到電子工程師的重視。高速pcb設計的成功,對EMI的貢獻越來越受到重視,幾乎60%的EMI問題可以通過高速PCB來控制解決。

2020-03-25 15:55:28 1400

1400

如上圖所示:在PCB設計中,時鐘等關鍵的高速信號線,走需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都是會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。

2

2020-06-05 10:54:04 2839

2839 高速PCB設計是指信號的完整性開始受到PCB物理特性(例如布局,封裝,互連以及層堆疊等)影響的任何設計。而且,當您開始設計電路板并遇到諸如延遲,串擾,反射或發射之類的麻煩時,您將進入高速PCB設計領域。

2020-06-19 09:17:09 1537

1537 PCB設計布局被認為是促進EMI在電路中傳播的主要問題之一。這就是為什么在開關電源中降低EMI的普遍而通用的技術之一是布局優化。

2021-01-28 10:58:06 2089

2089

下文是硬件工程師在PCB設計早期容易忽略,卻很有用的幾個EMI設計指南,這些指南也在一些權威書刊中常常被提到。

2020-10-09 09:54:57 3137

3137 電子發燒友網為你提供圖解在高速的PCB設計中的走線規則資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-03-27 08:43:14 23

23 PCB設計之在真實世界里的EMI控制說明。

2021-06-23 14:53:34 0

0 PCB設計規則你知幾何,20個PCB設計規則送給你。

2021-11-06 15:36:00 63

63 在進行PCB設計時,我們經常會遇到各種各樣的問題,如阻抗匹配、EMI規則等。本文為大家整理了一些和高速PCB相關的疑難問答,希望對大家有所幫助。

2022-08-11 08:55:42 2133

2133 隨著信號上升沿時間的減小,信號頻率的提高,電子產品的EMI問題,也來越受到電子工程師的重視。高速pcb設計的成功,對EMI的貢獻越來越受到重視,幾乎60%的EMI問題可以通過高速PCB來控制解決。

2022-11-11 11:44:51 528

528 摘要: 隨著信號上升沿時間的減小,信號頻率的提高,電子產品的EMI問題,也來越受到電子工程師的重視。高速pcb設計的成功,對EMI的貢獻越來越受到重視,幾乎60%的EMI問題可以通過高速PCB來控制解決。 高速信號走線屏蔽規則

2023-04-10 09:53:49 1744

1744

一站式PCBA智造廠家今天為大家講講PCB設計布局規則有哪些?PCB設計布局規則及技巧。

2023-05-04 09:05:20 1554

1554 解決。 高速信號走線屏蔽規則 如上圖所示:在高速的PCB設計中,時鐘等關鍵的高速信號線,則需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都是會造成EMI的泄漏。 建議屏蔽線每1000mil打孔接地 。 高速信號的走線閉環規則 由于PCB板的密度越來越高,很多PCB

2023-05-22 09:15:58 836

836

一站式PCBA智造廠家今天為大家講講PCB設計元件排列有什么規則?PCB設計元件排列規則。PCB設計布局也有很大的學問蘊含其中,目前,在PCB設計中常見的原則有五個,分別是元件排列規則、按照信號

2023-05-24 08:58:38 1123

1123 高速PCB設計指南之七

2022-12-30 09:22:13 4

4 高速PCB設計指南之八

2022-12-30 09:22:14 5

5 高速PCB設計指南之六

2022-12-30 09:22:15 3

3 高速PCB設計指南之四

2022-12-30 09:22:15 4

4 高速PCB設計指南二

2022-12-30 09:22:16 5

5 高速PCB設計電容的應用

2022-12-30 09:22:16 29

29 高速PCB設計的疊層問題

2022-12-30 09:22:17 37

37 高速PCB設計電容的應用

2023-03-01 15:37:57 2

2 一站式PCBA智造廠家今天為大家講講 pcb設計常見布線規則有哪些?PCB設計常見布線規則。

2023-11-14 09:17:55 606

606

PCB設計中,如何使用規則高效管理過孔

2023-12-06 15:54:54 201

201

一站式PCBA智造廠家今天為大家講講pcb設計布局布線原則及規則有哪些?PCB設計六大布線規則。在PCB設計中,布線是至關重要的一步。合理有效的布線能夠保證電路的穩定性和可靠性,避免電路布線錯誤帶來

2024-01-22 09:23:53 498

498

電子發燒友App

電子發燒友App

評論