項目背景

直放站在現代通信系統中是必不可少的,但是如果直放站的收發天線隔離度不夠,整機增益偏大時,輸出信號經延時后反饋到輸入端,會使直放站輸出信號發生嚴重失真產生自激。在無線通信系統的同頻直放站中,為了減小產品體積以及縮短建站成本,收發天線常常放置在一起(或距離很近)。由于收發天線往往只存在方向角的不同,因此直放站的接收天線肯定會接收到其轉發天線所發送的經過放大的信號,而對所期望接收的有用信號產生干擾。如果不對干擾信號進行處理,干擾和期望信號的疊加信號會再次被送進功放,再進行放大轉發,干擾信號的強度會一直積累,最終使得直放站無法正常工作。這種正反饋式干擾(干擾信號與正常通信信號的調制參數和載波頻率是完全一致的,使得接收機收到疊加有同頻干擾的混合信號)還會對數字通信產生嚴重的電磁干擾,從而阻礙正常的通信。在上、下行鏈路中,往往都存在著這種反饋式干擾,如圖1所示。

干擾抵消是同頻直放站所必備的一項技術,也是信號處理領域一個非常重要的課題[1]。傳統上,克服自激現象的方法有:(1)借助建筑物阻擋在發射和接收天線間;(2)增加直放站的施主和重發天線的空間隔離度。垂直隔離度一般最好大于1m,水平隔離度可以在十幾米以上。如果沒有垂直隔離的話,那么水平隔離的距離幾乎達到200米;(3)降低直放站的增益:上行和下行按照比例,就是上下行鏈路平衡,直至消除自激。

雖然上述三種辦法都可以在一定程度上降低干擾的影響,但是在某些場合,受到環境或系統性能的要求,這些方法并不可行。因此,利用自適應干擾抵消器來減少直放站設備的同頻反饋干擾成為首選方案。在所有的自適應方案中,尤以頻域算法在性能和復雜度之間取得良好平衡。

本項目以WCDMA系統為例,討論數字頻域自適應干擾抵消技術的實現,并從功率譜密度和星座圖以及誤差向量幅度(EVM)等性能指標對方案進行評價。在設計中,為了驗證算法性能且保證接收端的正常工作,同時實現了WCDMA小區搜索的三步同步過程,并通過PC機對輸入輸出數據進行比對分析,驗證方案性能。

系統方案

完整的系統從數字下變頻后的基帶數據開始,至數字上變頻的前端為止,包括系統同步和干擾抵消兩大組成模塊,系統框圖如圖2所示,其簡要介紹如下:

(1)在沒有干擾的情況下,所采集的數據源從A點輸入,然后將其構造為WCDMA信源,作為頻域干擾抵消模塊的輸入。為了使干擾抵消模塊正確運轉,在本設計中的B點輸出信號為每個碼片4采樣。

(2)為體現頻域干擾抵消的作用,在系統中必須模擬一個干擾信號。本設計將D點的輸出經過功放(PA)作為干擾信號。

(3)將干擾信號經過多徑信道,反饋到B點與WCDMA信號疊加,再進入干擾抵消模塊。為了抵消干擾,將E點的輸出反饋到干擾抵消模塊作為參考信號。在下文中,將此反饋支路稱為輔鏈路;而干擾抵消+功放的鏈路稱為主鏈路。

(4)有干擾的信號經過頻域干擾抵消模塊,輸出抵消后的無干擾信號給同步模塊,即D點。同步模塊進行三步搜索,得到幀頭以及擾碼信息。對同步后的碼片信號進行解擾解擴后得到信息數據,如圖中G點輸出。

(5)在開關1處,可以選擇:有干擾的信號(C點)或者干擾抵消后的信號(D點)輸入同步模塊,并輸出顯示。

(6)在開關2處,可以選擇:數據源直接顯示(A點),或者是同步后解出的數據顯示(G點)。

算法設計

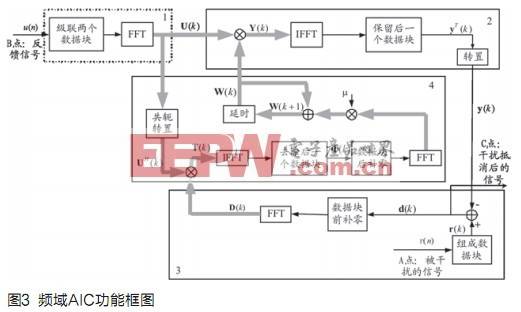

頻域自適應干擾抵消(AIC)模塊利用了頻域實現的LMS算法[2,3]。該算法通過1/2重疊保留法的快速傅立葉變換(FFT),在頻域以直接相乘的計算方式實現快速相關和快速卷積[4]。算法基本框圖如圖3,其中A點為被干擾的信號,B為反饋鏈路的信號,C點為干擾被抵消后的輸出。主要包括以下循環執行的操作流程,其中k表示第個k數據塊:

(1)對自適應濾波器的M個頻域抽頭系數W(k)作初始化設置;

(2)將濾波器的時域連續輸入信號u(n)每個M組成一個塊,然后級聯兩個數據塊做N點離散快速傅立葉變換,使其轉換為頻域信號U(k),并將此信號用作自適應濾波器的輸入;其中N是該濾波器抽頭個數M的2倍,即N=2M;

(3)將U(k)通過濾波器得到輸出信號Y(k),然后進行快速傅立葉逆變換(IFFT)處理,使其轉換為時域信號y(k),作為干擾的估計值;

(4)計算被干擾信號r(k)和y(k)的差值,即為干擾抵消后的信號d(k);再產生該期望信號的頻域值D(k)為下一次濾波器抽頭系數迭代所使用;

(5)利用頻域信號進行最小均方誤差LMS計算,即根據D(k)和U(k)對W(k)進行更新,并將此更新值返回到步驟(2)中使用。跳轉到步驟(2)進行反復迭代,直至干擾被抵消。

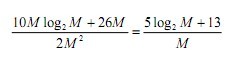

與傳統的時域LMS算法相比,利用頻域LMS算法可以降低計算復雜度。假設輸入為實信號,濾波器抽頭個數為。可以得到,頻域LMS和時域LMS的計算復雜度之比為 。實際中,干擾在空中傳輸的時延會比反饋信號的時延大得多,這時需要較大的抽頭個數才能抵消干擾。假設M=1024,則頻域LMS算法可以比時域LMS算法的速度提高大約16倍。為簡化起見,在本文檔中取M=64,利用頻域LMS算法,在計算量角度大約可以比時域LMS算法快1.5倍。

。實際中,干擾在空中傳輸的時延會比反饋信號的時延大得多,這時需要較大的抽頭個數才能抵消干擾。假設M=1024,則頻域LMS算法可以比時域LMS算法的速度提高大約16倍。為簡化起見,在本文檔中取M=64,利用頻域LMS算法,在計算量角度大約可以比時域LMS算法快1.5倍。

WCDMA同步算法

對于任何一個系統,要進行正常的運作都必須首先保證系統的同步。WCDMA的小區搜索分為三個階段,即主同步、輔同步和導頻搜索三個階段[5]。主同步利用PSC碼對接收到的主同步信道數據(PSCH)做相關,根據相關峰值的位置確定時隙頭。在主同步完成之后,輔同步階段可以確定幀頭位置和當前小區使用的擾碼組號。方法是用輔同步碼(SSC)去做相關。最后一個階段是導頻搜索,利用已經得到的擾碼組號和幀頭信息,遍歷一個主擾碼組所有的8個可能主擾碼,分別和導頻信道(CPICH)做相關。根據最大的相關值最終確定擾碼號。可見,經過WCDMA的三步同步,就可以得到當前小區的主擾碼號和幀同步信息。三步同步的流程圖如圖4所示。

由于同步模塊收到的信號為4采樣的,而同步模塊內部的搜索過程只需利用單采樣的數據,因此先要對過采樣的信號進行下采樣。另外,為了對發送信號源進行匹配,將接收到的信號首先經過根號升余弦匹配濾波器,然后再下采樣到碼片速率,如B點所示。

仿真和測試結果

仿真結果

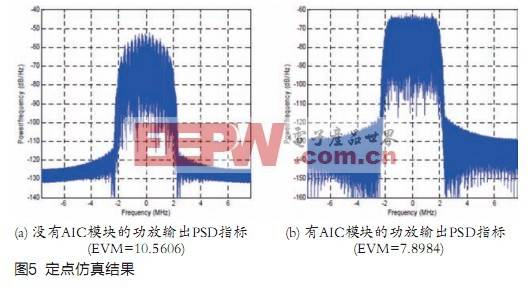

首先,經過功率譜密度圖(PSD)驗證,經過AIC的輸出信號PSD曲線和發送信源PSD曲線基本一致。圖5給出了信干比為-10dB時算法的定點仿真結果。

具體而言,在沒有AIC的情況下,輸出信號頻譜主瓣內的波動較大,而且主瓣下降dB值減小。采用AIC后,輸出信號頻譜主瓣內的波動基本得以改善,并且下降dB值也基本等于原來輸入信源的下降dB值,表明AIC性能良好。

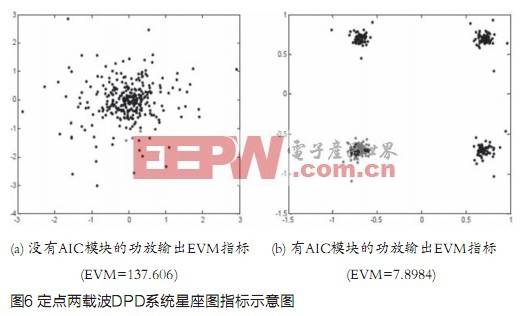

其次,通過量化指標EVM進行比較[3],圖6給出了信干比為-10dB時的EVM指標,可以看出,AIC算法可有效抵消干擾,改善星座圖。

硬件測試說明

在硬件實現時,利用的開發平臺為Virtex II Board。其中V2P30芯片FPGA具有136個硬核乘法器和塊RAM,可滿足自適應濾波算法以及大點數的FFT變換需要大量的乘法器和存儲器的需求。此外,大量的Slice可實現小區搜索模塊以及相關測試平臺的建立。

此外,對于簡易的視頻測試平臺,利用VGA接口完成測試平臺,進行最終的測試驗證。XUP Virtex II PRO板卡帶有高精度的DAC芯片FMS3818,能達到預期目的。軟件開發選用了ISE8.2.03i,相應的Chipscope為8.2版本。

硬件系統需要實現頻域AIC、小區同步搜索、WCDMA信源發生器、測試平臺4大模塊。其中AIC模塊可劃分為大點數的FFT變換以及相應的串并、并串轉換等主要功能。將設計分為5個大的模塊:頂層模塊、AIC處理模塊、信源發生器、小區搜索以及測試平臺。FFT模塊利用賽靈思公司的IP Core(知識產權核)來完成;串并、并串可以利用塊RAM實現;數據處理模塊盡可能地使用SRL16結構來實現,以節省資源。

系統測試按照由部分到整體的思路來完成,首先對各個模塊進行單獨測試,再將部分模塊組合起來完成測試,最后再對整體系統進行測試。這樣,可以將錯誤及早發現并將其消滅在起步階段。測試主要依靠ChipScope來完成,利用其采集數據,再把數據導入MATLAB中,和定點仿真、ModelSim輸出結果進行比較,完成數據分析,從而確保芯片的運行結果和仿真結果是相同的。在測試中,全部以方波測試平臺為基準。

電子發燒友App

電子發燒友App

評論