JK觸發(fā)器,JK觸發(fā)器是什么意思

JK觸發(fā)器,JK觸發(fā)器是什么意思

1.主從JK觸發(fā)器

主從結構觸發(fā)器也可以徹底解決直接控制,防止空翻。這里以性能優(yōu)良、廣泛使用的主從JK觸發(fā)器為例來討論。

(1).主從JK觸發(fā)器電路組成和符號

主從JK觸發(fā)器,簡稱JK觸發(fā)器,其邏輯圖和邏輯符號如圖4.12所示。 ???????????

???????????

(a)邏輯圖????? ?????????????????????(b)邏輯符號

圖4.12 主從JK觸發(fā)器

在圖4.12(a)所示邏輯圖中G1~G4門構成的同步RS觸發(fā)器稱為從觸發(fā)器;G5~G8門構成的同步RS觸發(fā)器稱為主觸發(fā)器。總稱主從觸發(fā)器。由于G9門的作用,主、從觸發(fā)器的時鐘脈沖剛好相反。

邊沿JK 觸發(fā)器:

電路結構:

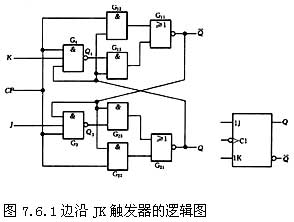

采用與或非電路結構,屬于下降沿觸發(fā)的邊沿JK觸發(fā)器,如圖7.6.1所示。

1.CP=0時,觸發(fā)器處于一個穩(wěn)態(tài)。

CP為0時,G3、G4被封鎖,不論J、K為何種狀態(tài),Q3、Q4均為1,另一方面,G12、G22也被CP封鎖,因而由與或非門組成的觸發(fā)器處于一個穩(wěn)定狀態(tài),使輸出Q、Q狀態(tài)不變。

2.CP由0變1時,觸發(fā)器不翻轉,為接收輸入信號作準備。

設觸發(fā)器原狀態(tài)為Q=0,Q=1。當CP由0變1時,有兩個信號通道影響觸發(fā)器的輸出狀態(tài),一個是G12和G22打開,直接影響觸發(fā)器的輸出,另一個是G4和G3打開,再經G13和G23影響觸發(fā)器的狀態(tài)。前一個通道只經一級與門,而后一個通道則要經一級與非門和一級與門,顯然CP的跳變經前者影響輸出比經后者要快得多。在CP由0變1時,G22的輸出首先由0變1,這時無論G23為何種狀態(tài)(即無論J、K為何狀態(tài)),都使Q仍為0。由于Q同時連接G12和G13的輸入端,因此它們的輸出均為0,使G11的輸出Q=1,觸發(fā)器的狀態(tài)不變。CP由0變1后,打開G3和G4,為接收輸入信號J、K作好準備。

3.CP 由1變0時觸發(fā)器翻轉

設輸入信號J=1、K=0,則Q3=0、Q4=1,G13和G23的輸出均為0。當CP 下降沿到來時,G22的輸出由1變0,則有Q=1,使G13輸出為1,Q=0,觸發(fā)器翻轉。雖然CP變0后,G3、G4、G12和G22封鎖,Q3=Q4=1,但由于與非門的延遲時間比與門長(在制造工藝上予以保證),因此Q3和Q4這一新狀態(tài)的穩(wěn)定是在觸發(fā)器翻轉之后。由此可知,該觸發(fā)器在CP下降沿觸發(fā)翻轉,CP一旦到0電平,則將觸發(fā)器封鎖,處于(1)所分析的情況。

總之,該觸發(fā)器在CP下降沿前接受信息,在下降沿觸發(fā)翻轉,在下降沿后觸發(fā)器被封鎖。

功能描述:

邊沿型JK觸發(fā)器的狀態(tài)轉移真值表、特征方程、狀態(tài)轉移圖及激勵表與主從JK觸發(fā)器完全一致,只不過在畫工作波形圖時,不用考慮一次變化現(xiàn)象。

脈沖工作特性:

該觸發(fā)器無一次變化現(xiàn)象,輸入信號可在CP 觸發(fā)沿由1變0時刻前加入。由圖7.6.1可知,該電路要求J、K信號先于CP 信號觸發(fā)沿傳輸?shù)紾3、G4的輸出端,為此它們的加入時間至少應比CP 的觸發(fā)沿提前一級與非門的延遲時間。這段時間稱為建立時間test。

輸入信號在負跳變觸發(fā)沿來到后就不必保持,原因在于即使原來的J、K信號變化,還要經一級與非門的延遲才能傳輸?shù)紾3和G4的輸出端,在此之前,觸發(fā)器已由G12、G13、G22、G23的輸出狀態(tài)和觸發(fā)器原先的狀態(tài)決定翻轉。所以這種觸發(fā)器要求輸入信號的維持時間極短,從而具有很高的抗干擾能力,且因縮短tCPH 可提高工作速度。

從負跳變觸發(fā)沿到觸發(fā)器輸出狀態(tài)穩(wěn)定,也需要一定的延遲時間tCPL。顯然,該延遲時間應大于兩級與或非門的延遲時間。即tCPL大于2.8tpd。

綜上所述,對邊沿JK 觸發(fā)器歸納為以下幾點:

1.邊沿JK 觸發(fā)器具有置位、復位、保持(記憶)和計數(shù)功能; 2.邊沿JK 觸發(fā)器屬于脈沖觸發(fā)方式,觸發(fā)翻轉只在時鐘脈沖的負跳變沿發(fā)生; 3.由于接收輸入信號的工作在CP下降沿前完成,在下降沿觸發(fā)翻轉,在下降沿后觸發(fā)器被封鎖,所以不存在一次變化的現(xiàn)象,抗干擾性能好,工作速度快。

主從JK 觸發(fā)器:

電路結構:

主從JK 觸發(fā)器是在主從RS觸發(fā)器的基礎上組成的,如圖7.5.1所示。 在主從RS觸發(fā)器的R端和S端分別增加一個兩輸入端的與門G11和G10,將Q端和輸入端經與門輸出為原S端,輸入端稱為J端,將Q端與輸入端經與門輸出為原R端,輸入端稱為K端。

工作原理

由上面的電路可得到S=JQ,R=KQ。代入主從RS觸發(fā)器的特征方程得到:

![]()

當 J=1,K=0時,Qn+1=1; J=0,K=1時,Qn+1=0; J=K=0時,Qn+1=Qn; J=K=1時,Qn+1=Qn;

由以上分析,主從JK 觸發(fā)器沒有約束條件。在J=K=1時,每輸入一個時鐘脈沖,觸發(fā)器翻轉一次。觸發(fā)器的這種工作狀態(tài)稱為計數(shù)狀態(tài),由觸發(fā)器翻轉的次數(shù)可以計算出輸入時鐘脈沖的個數(shù)。

功能描述:

特征方程:

![]()

狀態(tài)轉移真值表:

狀態(tài)轉換圖:

脈沖工作特性

建立時間:是指輸入信號應先于CP信號到達的時間,用tset表示。由圖7.5.5可知,J、K信號只要不遲于CP信號到達即可,因此有tset=0。保持時間:為保證觸發(fā)器可靠翻轉,輸入信號需要保持一定的時間。保持時間用tH表示。如果要求 CP=1期間J、K的狀態(tài)保持不變,而CP=1的時間為tWH,則應滿足:tH≥tWH。

傳輸延遲時間:若將從CP下降沿開始到輸出端新狀態(tài)穩(wěn)定地建立起來的這段時間定義為傳輸時間,則有:tPLH=3tpd tPHL=4tpd 最高時鐘頻率:因為主從觸發(fā)器都是由兩個同步RS 觸發(fā)器組成的,所以由同步RS觸發(fā)器的動態(tài)特性可知 ,為保證主觸發(fā)器的可靠翻轉,CP高電平的持續(xù)時間tWH應大于3tpd。同理,為保證從觸發(fā)器能可靠地翻轉, CP低電平的持續(xù)時間tWL也應大于3tpd。因此,時鐘信號的最小周期為:Tc(min)≥6tpd 最高時鐘頻率fc(max)≤1/6tpd。

如果把圖7.5.5的J、K觸發(fā)器接成T觸發(fā)器使用(即將J和K相連后接至高電平),則最高時鐘頻率還要低一些。因為從CP的下降沿開始到輸出端的新狀態(tài)穩(wěn)定建立所需要的時間為tPHL≥4tpd,如果CP信號的占空比為50%,那么CP信號的最高頻率只能達到fc(max)=1/2tPHL=1/8tpd

集成觸發(fā)器

集成JK觸發(fā)器的產品較多,以下介紹一種比較典型的高速CMOS雙JK觸發(fā)器HC76。該觸發(fā)器內含兩個相同的JK觸發(fā)器,它們都帶有預置和清零輸入,屬于負跳沿觸發(fā)的邊沿觸發(fā)器,其邏輯符號和引腳分布如下圖7.5.6 所示。其功能表如表7.5.1所示。如果在一片集成器件中有多個觸發(fā)器,通常在符號前面(或后面)加上數(shù)字,以表示不同觸發(fā)器的輸入、輸出信號,比如C1與1J、1K同屬一個觸發(fā)器。

綜上所述,對主從JK 觸發(fā)器歸納為以下的幾點:

1.主從JK觸發(fā)器具有置位、復位、保持(記憶)和計數(shù)功能;

2.主從JK觸發(fā)器屬于脈沖觸發(fā)方式,觸發(fā)翻轉只在時鐘脈沖的負跳變沿發(fā)生;

3.不存在約束條件,但存在一次變化現(xiàn)象。

4.產生一次變化的原因是因為在CP=1期間,主觸發(fā)器一直在接收數(shù)據(jù),但主觸發(fā)器在某些條件下(Q=0,CP=1期間J端出現(xiàn)正跳沿干擾或Q=1,CP=1期間K端出現(xiàn)正跳沿干擾),不能完全隨輸入信號的變化而發(fā)生相應的變化,以至影響從觸發(fā)器 狀態(tài)與輸入信號的不對應。

非常好我支持^.^

(6) 100%

不好我反對

(0) 0%

相關閱讀:

- [電子說] JK觸發(fā)器與T觸發(fā)器的Verilog代碼實現(xiàn)和RTL電路實現(xiàn) 2023-10-09

- [電子說] 觸發(fā)器激勵函數(shù)和輸出函數(shù)解析 2023-08-24

- [電子說] 觸發(fā)器有兩個互非的輸出端Q 2023-08-24

- [電子說] 如何用jk觸發(fā)器組成單脈沖發(fā)生器 2023-08-24

- [電子說] JK觸發(fā)器的工作原理及真值表 2023-06-29

- [電子說] 雙JK觸發(fā)器的工作原理和應用電路詳解 2023-05-05

- [電子說] 觸發(fā)器的類型介紹 2023-03-23

- [電子說] 一文詳解帶復位的SR觸發(fā)器和JK觸發(fā)器 2023-01-31

( 發(fā)表人:admin )