在Google發(fā)布TPU一年后,這款機(jī)器學(xué)習(xí)定制芯片的神秘面紗終于被揭開了。

昨日,Google資深硬件工程師Norman Jouppi刊文表示,Google的專用機(jī)器學(xué)習(xí)芯片TPU處理速度要比GPU和CPU快15-30倍(和TPU對(duì)比的是IntelHaswell CPU以及NVIDIA Tesla K80 GPU),而在能效上,TPU更是提升了30到80倍。

從這次發(fā)布的測(cè)試結(jié)果來看,TPU似乎已經(jīng)超出了業(yè)界的預(yù)期,但是藏在這一芯片背后的內(nèi)部架構(gòu)究竟有什么秘密呢?我們從Jouppi此前發(fā)布的論文當(dāng)中,可以找到答案。

據(jù)了解,早在四年前,Google內(nèi)部就開始使用消耗大量計(jì)算資源的深度學(xué)習(xí)模型。這對(duì)CPU、GPU組合而言是一個(gè)巨大的挑戰(zhàn),Google深知如果基于現(xiàn)有硬件,他們將不得不將數(shù)據(jù)中心數(shù)量翻一番來支持這些復(fù)雜的計(jì)算任務(wù)。

所以Google開始研發(fā)一種新的架構(gòu),Jouppi稱之為“下一個(gè)平臺(tái)”。Jouppi曾是MIPS處理器的首席架構(gòu)師之一,他開創(chuàng)了內(nèi)存系統(tǒng)中的新技術(shù)。三年前他加入Google的時(shí)候,公司上下正在用CPU、GPU混合架構(gòu)上來進(jìn)行深度學(xué)習(xí)的訓(xùn)練。

Jouppi表示,Google的硬件工程團(tuán)隊(duì)在轉(zhuǎn)向定制ASIC之前,早期還曾用FPGA來解決廉價(jià)、高效和高性能推理的問題。但他指出,F(xiàn)PGA的性能和每瓦性能相比ASIC都有很大的差距。

他解釋說,TPU可以像CPU或GPU一樣可編程,它可以在不同的網(wǎng)絡(luò)(卷積神經(jīng)網(wǎng)絡(luò),LSTM模型和大規(guī)模完全連接的模型)上執(zhí)行CISC指令,而不是為某個(gè)專用的神經(jīng)網(wǎng)絡(luò)模型設(shè)計(jì)的。

一言以蔽之,TPU兼具了CPU和ASIC的有點(diǎn),它不僅是可編程的,而且比CPU、GPU和FPGA擁有更高的效率和更低的能耗。

TPU的內(nèi)部架構(gòu)

該圖顯示了TPU上的內(nèi)部結(jié)構(gòu),除了外掛的DDR3內(nèi)存,左側(cè)是主機(jī)界面。指令從主機(jī)發(fā)送到隊(duì)列中(沒有循環(huán))。這些激活控制邏輯可以根據(jù)指令多次運(yùn)行相同的指令。

TPU并非一款復(fù)雜的硬件,它看起來像是雷達(dá)應(yīng)用的信號(hào)處理引擎,而不是標(biāo)準(zhǔn)的X86衍生架構(gòu)。

Jouppi說,盡管它有眾多的矩陣乘法單元,但是它比GPU更精于浮點(diǎn)單元的協(xié)處理。另外,需要注意的是,TPU沒有任何存儲(chǔ)的程序,它可以直接從主機(jī)發(fā)送指令。

TPU上的DRAM作為一個(gè)單元并行運(yùn)行,因?yàn)樾枰@取更多的權(quán)重以饋送到矩陣乘法單元(算下來,吞吐量達(dá)到了64,000)。Jouppi并沒有提到是他們是如何縮放并行結(jié)構(gòu)的,但他表示,使用的主機(jī)軟件加速器都將成為瓶頸。

從第一張圖片可以看出,TPU有兩個(gè)內(nèi)存單元,以及一個(gè)用于模型中參數(shù)的外部DDR3 DRAM。參數(shù)進(jìn)來后,可從頂部加載到矩陣乘法單元中。同時(shí),可以從左邊加載激活(或從“神經(jīng)元”輸出)。那些以收縮的方式進(jìn)入矩陣單元以產(chǎn)生矩陣乘法,它可以在每個(gè)周期中進(jìn)行64,000次累加。

毋庸置疑,Google可能使用了一些新的技巧和技術(shù)來加快TPU的性能和效率。例如,使用高帶寬內(nèi)存或混合3D內(nèi)存。然而,Google的問題在于保持分布式硬件的一致性。

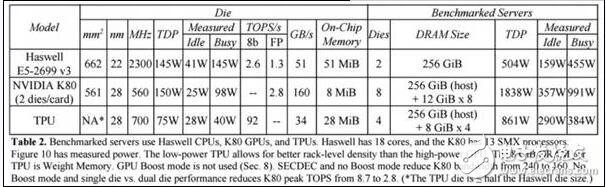

TPU對(duì)比Haswell處理器

在和Intel“Haswell”Xeon E5 v3處理器來的對(duì)比中,我們可以看到,TPU各方面的表現(xiàn)都要強(qiáng)于前者。

在Google的測(cè)試中,使用64位浮點(diǎn)數(shù)學(xué)運(yùn)算器的18核心運(yùn)行在2.3 GHz的Haswell Xeon E5-2699 v3處理器能夠處理每秒1.3 TOPS的運(yùn)算,并提供51GB/秒的內(nèi)存帶寬;Haswell芯片功耗為145瓦,其系統(tǒng)(擁有256 GB內(nèi)存)滿載時(shí)消耗455瓦特。

相比之下,TPU使用8位整數(shù)數(shù)學(xué)運(yùn)算器,擁有256GB的主機(jī)內(nèi)存以及32GB的內(nèi)存,能夠?qū)崿F(xiàn)34GB/秒的內(nèi)存帶寬,處理速度高達(dá)92 TOPS ,這比Haswell提升了71倍,此外,TPU服務(wù)器的熱功率只有384瓦。

除此之外,Google還測(cè)試了CPU、GPU和TPU處理不同批量大小的每秒推斷的吞吐量。

如上圖所示,在小批量任務(wù)中(16),Haswell CPU的響應(yīng)時(shí)間接近7毫秒,其每秒提供5482次推斷(IPS),其可以實(shí)現(xiàn)的最大批量任務(wù)(64)每秒則可以完成13194次推斷,但其響應(yīng)時(shí)間為21.3毫秒。相比之下,TPU可以做到批量大小為200,而響應(yīng)時(shí)間低于7毫秒,并提供225000個(gè)IPS運(yùn)行推理基準(zhǔn),是其峰值性能的80%,當(dāng)批量大小為250,響應(yīng)時(shí)間為10毫秒。

不過需要注意的是,Google所測(cè)試的Haswell Xeon處理器似乎也不能完全說明問題,IntelBroadwell Xeon E5 v4處理器和最新的“Skylake”Xeon E5,每核心時(shí)鐘(IPC)的指令比這款處理器提升了約5%。在Skylake是28核,而Haswell為18核,所以Xeon的總體吞吐量可能會(huì)上升80%。當(dāng)然,這樣的提升與TPU相比仍有差距。

最后需要強(qiáng)調(diào)的是,TPU是一個(gè)推理芯片,它并非是要取代GPU,可以確定的是,TPU與CPU一起使用對(duì)訓(xùn)練分析更加有益,但對(duì)于CPU制造商而言,如何研發(fā)出像ASIC一樣兼顧性能和能效的芯片是現(xiàn)在以及未來要做的。

Jouppi表示GoogleTPU已經(jīng)開始出貨,而Intel這些芯片商也將面臨更大的挑戰(zhàn)。

非常好我支持^.^

(0) 0%

不好我反對(duì)

(0) 0%

相關(guān)閱讀:

- [電子說] 怎樣解決霍爾搖桿耗電量大的問題?揭秘霍爾芯片的選型要求 2023-10-24

- [電子說] Blackwell GB100能否在超級(jí)計(jì)算機(jī)和AI市場(chǎng)保持領(lǐng)先優(yōu)勢(shì)? 2023-10-24

- [電子說] 淺析BUCK芯片在電路中的應(yīng)用及特點(diǎn) 2023-10-24

- [電子說] OTA語音芯片NV040C在智能電動(dòng)牙刷的應(yīng)用 2023-10-24

- [電子說] 新思科技面向臺(tái)積公司N5A工藝技術(shù)推出領(lǐng)先的廣泛車規(guī)級(jí)IP組合 2023-10-24

- [電子說] 使用半大馬士革工藝流程研究后段器件集成的工藝 2023-10-24

- [電子說] 國(guó)產(chǎn)運(yùn)放和溫度傳感器介紹 2023-10-24

- [電子說] 首批高通驍龍8 Gen3旗艦入網(wǎng) 2023-10-24

( 發(fā)表人:易水寒 )