構(gòu)建晶體管之間連接電路 - 沙子做的CPU憑什么賣那么貴?

13.構(gòu)建晶體管之間連接電路

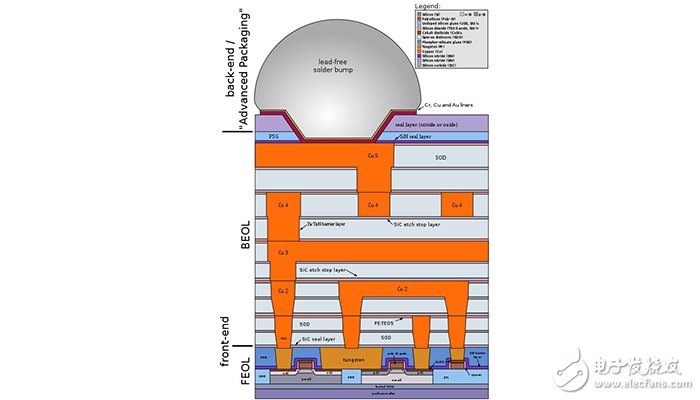

經(jīng)過漫長的工藝,數(shù)以十億計(jì)的晶體管已經(jīng)制作完成。剩下的就是如何將這些晶體管連接起來的問題了。同樣是先形成一層銅層,然后光刻掩模、蝕刻開孔等精細(xì)操作,再沉積下一層銅層。。。。。。這樣的工序反復(fù)進(jìn)行多次,這要視乎芯片的晶體管規(guī)模、復(fù)制程度而定。最終形成極其復(fù)雜的多層連接電路網(wǎng)絡(luò)。

由于現(xiàn)在IC包含各種精細(xì)化的元件以及龐大的互聯(lián)電路,結(jié)構(gòu)非常復(fù)雜,實(shí)際電路層數(shù)已經(jīng)高達(dá)30層,表面各種凹凸不平越來越多,高低差異很大,因此開發(fā)出CMP化學(xué)機(jī)械拋光技術(shù)。每完成一層電路就進(jìn)行CMP磨平。

另外為了順利完成多層Cu立體化布線,開發(fā)出大馬士革法新的布線方式,鍍上阻擋金屬層后,整體濺鍍Cu膜,再利用CMP將布線之外的Cu和阻擋金屬層去除干凈,形成所需布線。

大馬士革法多層布線

芯片電路到此已經(jīng)基本完成,其中經(jīng)歷幾百道不同工藝加工,而且全部都是基于精細(xì)化操作,任何一個(gè)地方出錯(cuò)都會(huì)導(dǎo)致整片晶圓報(bào)廢,在100多平方毫米的晶圓上制造出數(shù)十億個(gè)晶體管,是人類有文明以來的所有智慧的結(jié)晶。

后工程——從劃片到成品銷售

14. 晶圓級(jí)測試

前工程與后工程之間,夾著一個(gè)Good-Chip/Wafer檢測工程,簡稱G/W檢測。目的在于檢測每一塊晶圓上制造的一個(gè)個(gè)芯片是否合格。通常會(huì)使用探針與IC的電極焊盤接觸進(jìn)行檢測,傳輸預(yù)先編訂的輸入信號(hào),檢測IC輸出端的信號(hào)是否正常,以此確認(rèn)芯片是否合格。

由于目前IC制造廣泛采用冗余度設(shè)計(jì),即便是“不合格”芯片,也可以采用冗余單元置換成合格品,只需要使用激光切斷預(yù)先設(shè)計(jì)好的熔斷器即可。當(dāng)然,芯片有著無法挽回的嚴(yán)重問題,將會(huì)被標(biāo)記上丟棄標(biāo)簽。

非常好我支持^.^

(7) 87.5%

不好我反對(duì)

(1) 12.5%

相關(guān)閱讀:

- [電子說] 金川蘭新電子半導(dǎo)體封裝新材料生產(chǎn)線項(xiàng)目主體封頂 2023-10-24

- [電子說] 使用半大馬士革工藝流程研究后段器件集成的工藝 2023-10-24

- [電子說] ESD介紹及TVS的原理和應(yīng)用 2023-10-24

- [電子說] 怎樣延長半導(dǎo)體元器件的壽命呢? 2023-10-24

- [電子說] 瑞能半導(dǎo)體:碳化硅助力加速新能源汽車行業(yè)發(fā)展 2023-10-24

- [電子說] 氮化鎵充電器如何變得更快更強(qiáng) 2023-10-24

- [電子說] 射頻識(shí)別技術(shù)漫談(27)——CPU卡概述 2023-10-24

- [電子說] 講一講Apple Macintosh處理器過渡的故事 2023-10-24

( 發(fā)表人:方泓翔 )