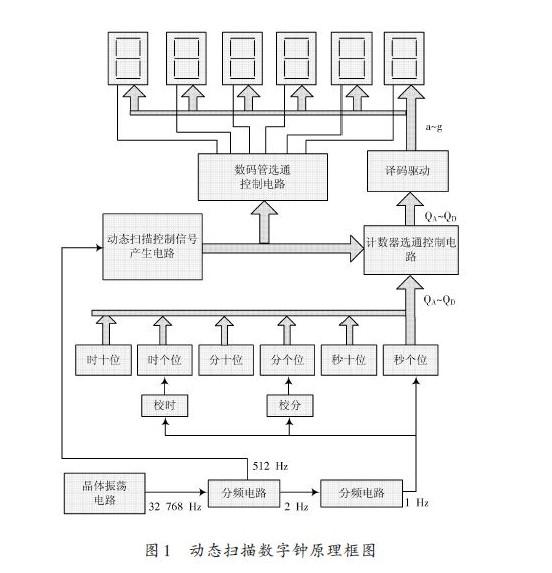

?

為了確保芯片在制作完成后的正確性,有關電路測試的這個問題越來越受重視。而且其測試的難度及成本也越來越高,于是如何有效地檢驗電路的正確性,并大幅度地降低測試成本,成為我們現在研究的熱點。通常我們在設計芯片的同時,可以根據芯片本身的特征,額外地把可測性電路設計(Design For Testability)在芯片里。談到可測性的電路設計,內建自測試(BIST)和基于掃描Scan—Based)的電路設計是常被提及的。

基于掃描的電路設計是可測性設計中最常用的一種方法。它是屬于Test—Per—Scan測試方法的電路。

目前的測試方法有兩種,一種是Test—Per—Scan,另一種是Test—Per—Clock,這兩種測試方法各有各的優缺點。所謂Test—Per—Scan的運作方式,就是我們將一個電路里的全部或部分寄存器串聯起來,形成一條掃描鏈,然后將測試序列在每個周期移入一個值,直到測試向量填滿整個掃描路徑為止,再經過一個周期后,我們將待測電路的測試結果傳到掃描鏈里。最后移出做壓縮分析。這種方法的優點是很容易運用在任何商業性的設計流程中,而且其硬件架構對系統功能的影響較小,控制硬件設計也較為簡單:缺點是要*較多的時間來產生測試向量,測試速度慢。所謂Test—Per一Clock,就是當我們在測試電路的時候,每一個周期都送進一個新的測試向量進入電路,同時在電路的輸出得到測試的結果,所以這種方式的電路測試時間較短,速度較快。

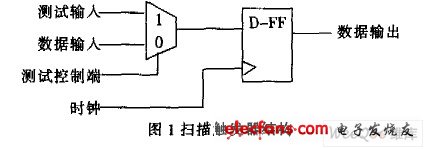

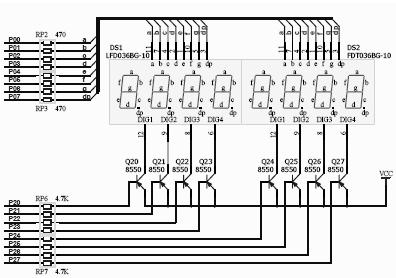

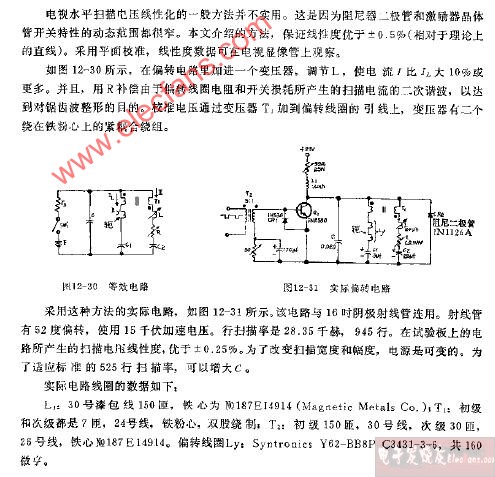

基于掃描的電路設計,主要是將待測電路內的寄存器,全部或部分用掃描寄存器來代替,讓我們在對電路進行測試的時候可以輕易地控制其輸入及輸出,掃描寄存器最常用的結構是多路掃描寄存器,它是在普通寄存器的輸入端口加上一個多路器, 如圖1所示。測試控制端即多路器的選擇端,數據輸入端為正常的功能輸入端。此外還有測試輸入端、時鐘輸入端和數據輸出端。當測試輸入端為“0”時,寄存器為正常的功能輸入,電路處于正常模式;當測試輸入端為“1”時,寄存器為掃描輸入。電路就轉換成掃描模式。很明顯。基于掃描的電路設計可以增加待測電路的可控制性和可觀察性。這種設計方式。優點是需要額外的硬件空間較少,而且測試的效果較好,缺點是測試時間太長。造成測試時間長的原因有多個方面,我們可以通過分析基于掃描的電路設計來得到。這個缺點,正是我們想要改進的部分。

?

2 基于掃描的電路的基本單元

2.1 線性反饋移位寄存器(LFSR)

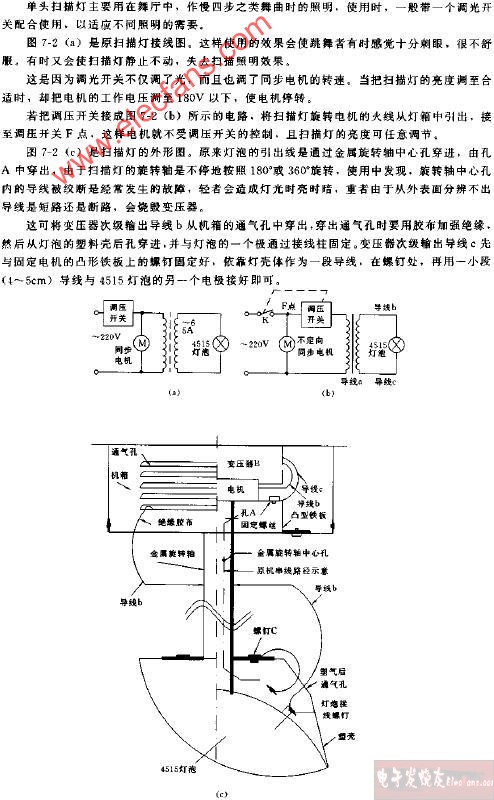

最簡單的測試向量產生器就是由線性反饋移位寄存器(Linear Feedback Shift Registers,LFSR)來組成的。因為當時鐘信號改變時,線性反饋移位寄存器內D觸發器的值就會改變,此時我們就可以將這些會一直改變的值當成測試向量,送給電路做測試。

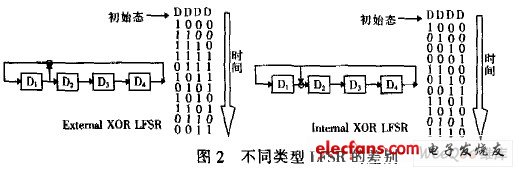

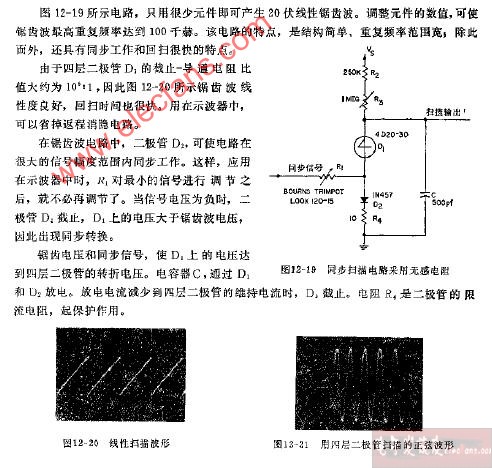

一般的線性反饋移位寄存器可以分為兩類,分別是Extemal XOR線性反饋移位寄存器和Internal XOR線性反饋移位寄存器,如圖2所示。這兩種線性反饋移位寄存器的主要差別在于External XOR線性反饋移位寄存器的modulo一2加法器是放在電路的反饋路徑上。而Internal XOR的線性反饋移位寄存器的加法器則是放在兩個寄存器之問。這兩種不同結構的線性反饋移位寄存器所產生出的測試向量也不一樣,ExternalXOR線性反饋移位寄存器所產生的測試向量有下列特性:每個向量與下個向量之問的關系,是向量中的位分別往右移了一位。而Internal XOR的線性反饋移位寄存器由于modulo一2加法器是在寄存器之問,所以產生的測試向量看起來比External XOR線性反饋移位寄存器有更隨機的特性,所以我們必須選擇InternalXOR LFSR作為測試向量產生器。

?

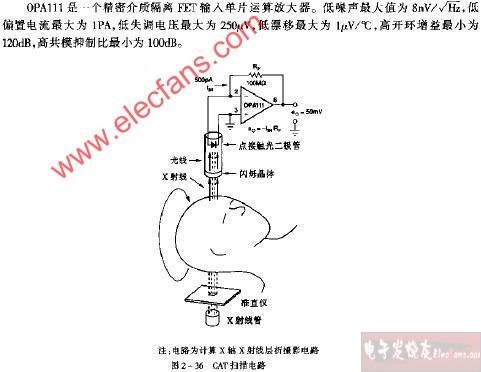

2.2 多輸入特征寄存器(MISR)

多輸入特征寄存器(Multiple Input Signature Reg—ister,MISR)是線性反饋移位寄存器的一種。如圖3所示,將待測電路的輸出部分加入線性反饋移位寄存器里,就成為一個多輸入特征寄存器。

多輸入特征寄存器最主要的特性是它的狀態。即其寄存器的值,不僅與現在的狀態有關,還與當時的輸入值有關,可以表示為:Next state=MISR(Cur—renLstate,Input),而其中MISR(……)可以代表特征式不同的多輸入特征寄存器。

?

3 基于掃描的測試架構的改進

為了減少基于掃描的電路設計的測試時間,就必須深入了解它的電路設計,了解為何其會消耗那么多的測試時間,然后來改進測試架構。

3.1 用向量壓縮來減少測試時間

在測試過程中,我們有時可以發現,我們將要傳入掃描鏈的測試向量,已經部分地包含在已經傳入的測試向量序列中了,如圖4所示。V1向量的后半部分剛好等于V2向量的前半部分“1010”,如果在傳輸向量的時候,先傳輸V1再傳輸V2,那么我們就只需要將V2的后半段向量信息傳入掃描鏈就可以讓V2原本的信息在掃描鏈中完整地呈現,如圖中V3所示。很明顯,我們原來要輸入的測試向量的長度為16位,壓縮后只有12位,節省了V2的前半部分傳入掃描鏈的時間,從而減少了測試的時間,而且測試信息也沒有減少,不會影響故障覆蓋率。

?

3.2 用Test—Per-Clock來縮短測試時間

我們對造成測試時間不夠理想的原因進行分析:

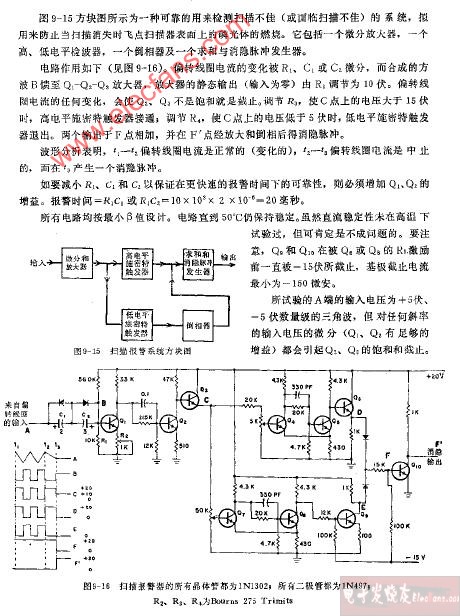

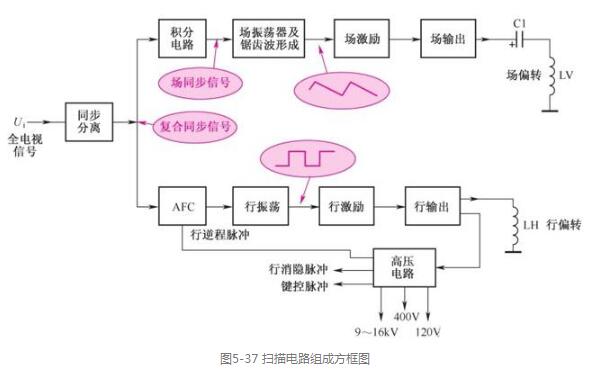

傳統的基于掃描的測試電路是采取Test—Per—Scan的方式來進行測試的,也就是說要先將測試向量掃描到電路內的由掃描寄存器所組成的掃描鏈內。然后才可以完成一次測試;將測試向量掃描到待測電路這個步驟是一位一位地進行的,所以如果一個電路需要長度較大的測試的向量時,那么在這整個測試過程里。將會花很多的時間在將測試向量輸入到掃描鏈的這個步驟上,從而增加了測試時間。這個結構的測試向量的產生是利用LFSR產生出的偽隨機向量,并將其送入電路做測試。用LFSR產生測試向量會產生出許多沒有作用的測試向量,而這些沒有作用的測試向量又會產生大量多余的時間將其送入掃描鏈中,造成測試時間更嚴重的浪費。如果采用Test—Per—Clock的方式做測試,在掃描鏈里原本的測試向量,在用一個時鐘的時間移進來一位之后,掃描鏈所含的值即是測試向量,對待測電路而言,其實都是一個新的測試向量,而且也具有偽隨機向量的特性,如果此測試向量是有效的,我們的測試時間就只用了一個時鐘的時間,而如果此測試向量無效,原本測試到沒有作用的測試向量時所需的付出的時間代價,由于用了新的測試向量填滿整個掃描鏈所需的時間,減少到只需一個時鐘移進一位的時間。

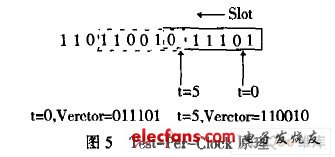

如圖5所示,每個時鐘周期。Slot會往左移動一位,即在Slot內產生一個新的測試向量,而Slot大小可以看成掃描鏈的大小。

?

不過,由于每個時鐘都要作測試,所以每個時鐘在測試后都會產生新的測試結果。傳統的基于掃描的測試環境里,電路輸出結果傳送出來的同時也將新的測試傳進掃描鏈里。

如果輸出的向量只有一位就不會有這樣的問題。

因為我們現在要產生一個新的測試向量所需要的時間只有一個時鐘周期,所以時問剛剛好。但是一般而言,待測電路的輸出向量都會超過一位。所以我們在觀察電路輸出結果這個步驟上就會有問題。為了解決這個問題,需要對傳統的基于掃描的測試電路做些修改。在待測電路的輸出部分,可以用MISR來取代原來的掃描鏈電路,也就是將輸出送到MISR做特征分析,如圖6所示。

?

但是由于電路越來越復雜,電路的主要輸入與輸出的個數就會很多,如果對這樣的待測電路加測試電路,將會出現外加電路面積過大的問題。所以我們針對MISR的部分提出一個方法,使得因測試而增加得MISR可以盡量地縮小。

縮小MISR的大小最直接的想法是將主要輸出經組合電路壓縮變小,但是這樣會使錯誤覆蓋率降低,使測試向量變多,這些問題在文獻中談到了。造成錯誤覆蓋率降低的原因是如果我們將有共同輸入向量的兩個主要輸出通過組合電路合并的話。將可能會造成原本可以測試到的錯誤,在合并后就測試不到了,所以造成了錯誤覆蓋率的降低。

為了避免這個情況的發生,我們在向量壓縮的過程中。只有將沒有共同輸入向量的主要輸出合并在一起,就不會有問題出現了。如圖6所示,兩個不同的待測電路的主要輸出經過合并以后輸出到MISR,這樣用一個與門代替了一個寄存器以便減少面積,而錯誤覆蓋率則因為兩兩合并的主要輸出端都沒有相同的主要輸出資料,所以就沒有錯誤覆蓋率降低的問題存在,即原來可以被偵測到的錯誤,在經過主要輸出端合并之后仍然可以被偵測到。

4 結論

經過改進后的基于掃描的測試架構,用向量壓縮來減少測試時間,并且將Test—Per-Scan的測試方式改成了Test—Per-Clock的測試方式,加快了測試的速度。

電子發燒友App

電子發燒友App

評論