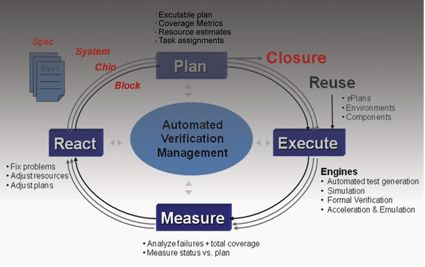

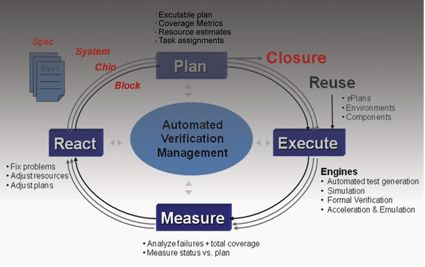

Cadence設計系統公司公布一個新版的尖端功能驗證平臺與方法學,擁有全套最新增強功能,與之前發布的版本相比,可將SoC驗證效率提高一倍。 Incisive ?12.2提供了兩倍性能,全新Incisive調試分析器產品,全新低功耗建模,以及當今復雜IP與SoC高效驗證所需的數百種其他功能。

2013-01-27 10:44:38 1437

1437

以下是筆者一些關于FPGA功耗估計和如何進行低功耗設計的知識。##關于FPGA低功耗設計,可從兩方面著手:1)算法優化;2)FPGA資源使用效率優化。

2014-12-17 09:27:28 9177

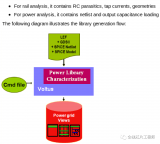

9177 Cadence功耗分析首先需生成power grid library

2023-09-06 09:47:50 859

859

設計靜態驗證,可以為集成電路(IC)工程師快速定位低功耗設計所帶來的可能的設計漏洞和缺陷。 應用驅動下的集成電路大趨勢 隨著人工智能、5G、大數據中心、汽車等應用帶來的IC功能和復雜度爆炸性增長,低功耗設計的重要性與日俱增。炬芯科技研發副總經理張賢鈞在發布會上的發言表示:

2022-11-03 10:29:15 735

735

2015 Cadence新技術研討會Cadence一致探索并研發EDA新技術,以加速設計并提高我們設計品質!2015 Cadence 新產品成員(OLB,OPE,EDM)如何助推我們的設計效率、全新

2015-05-19 10:19:07

描述此 TI 精密驗證設計可為單電源、低功耗信號調整電路提供原理、組件選擇和仿真,旨在將 +/-5 V 輸入信號轉換為單電源低功耗 16 位 ΔΣ ADC 的正確輸入范圍,例如,MSP430 內部

2018-11-15 10:13:26

數據透傳是選擇低功耗WiFi模塊還是低功耗藍牙模塊好?

2021-01-04 06:55:35

低功耗的加密產品有推薦嗎?用于一款智能設備上,對功耗有嚴格要求的。

2019-08-01 17:21:42

本文將探討這樣的低功耗系統的某些要求,如對于低功耗喚醒無線電產品的需求,并列舉應用示例和比較各種競爭技術。

2021-04-19 06:34:39

)希望在服務器節點藍牙(服務器節點的功耗不是問題)同時連接低功耗藍牙和普通藍牙,這樣可行嗎?

2)希望通過低功耗藍牙傳送語音是否可行?帶寬能達到1M嗎?如果能達到1M,其功耗和有效載荷各是多少?其中低功耗藍牙是間歇性傳送語音,傳送語音的時長和頻率都不是很高

2018-06-21 04:21:54

的使用對于低功耗藍牙來說是實現低功耗的關鍵,由于無線電處于發射及接收狀態時對于能量的使用和消耗是較多的,因此以下幾個方面對功耗也是大大的減少。 (1)高效率編碼高效率的編碼方式可以用更少的時間發送同等數量

2018-02-06 15:32:54

何謂低功耗藍牙?

2021-05-21 06:27:21

!在無線鍵盤、鼠標、多點觸控觸摸板、遙控、3D 眼鏡、游戲控制器、遙控玩具等領域均極大的潛力。小家電將BLE藍牙模塊內置在傳統小家電里面,例如豆漿機、電飯煲、電風扇等,增加低功耗藍牙控制,將其升級為

2019-03-18 02:25:12

低功耗設計

2020-12-31 06:09:30

YJ1329是一款低功耗,高效率,高頻1.2MHz同步升壓芯片。

2019-11-09 09:29:43

描述 此 TI 精密驗證設計可為單電源、低功耗信號調整電路提供原理、組件選擇和仿真,旨在將 +/-5 V 輸入信號轉換為單電源低功耗 16 位 ΔΣ ADC 的正確輸入范圍,例如,MSP430 內部

2022-09-20 06:02:09

程序使用定時喚醒采樣方式,每隔一段時間喚醒,進行AD采樣。問題在于,如果不使用內部2.5V基準電壓,進入低功耗時候,電流在20uA左右;使用內部2.5V基準電壓,進入低功耗前關閉(ADC12CTL0

2018-06-21 14:54:10

給大家推薦一款低功耗的MCU---Ambiq Micro。適用于可穿戴設備、物聯網、健康醫療、Sensor Hub、儀器儀表等領域Ambiq Micro是一家以研發低功耗芯片產品為主的公司,總部在

2015-04-28 17:20:14

K | RB_PWR_RAM2K); //只保留30+2K SRAM 供電HSECFG_Current(HSE_RCur_100); // 降為額定電流(低功耗函數中提升了HSE偏置電流)用IO口喚醒后,就搜不到

2022-09-07 06:36:24

F30如何實現低功耗,手冊上的能耗特性顯示sleep模式下可以達到2uA,simpleBLEproject中除了設置GPIO接地、連接參數和運行模式外,大家還有沒有其他的方案思路?不明白藍牙實現低功耗的途徑,請大佬們不吝賜教,感謝!

2023-10-12 09:31:01

“開放式合作”的形式,眾多用戶都在使用Cadence的高階綜合工具來提升設計效率和質量,并借助其最完備的功能驗證解決方案來確保設計的正確性。【詳細內容】

2013-04-17 11:20:14

結合采用低功耗元件和低功耗設計技術在目前比以往任何時候都更有價值。隨著元件集成更多功能,并越來越小型化,對低功耗的要求持續增長。當把可編程邏輯器件用于低功耗應用時,限制設計的低功耗非常重要。如何減小動態和靜態功耗?如何使功耗最小化?

2019-08-27 07:28:24

MCU怎么實現低功耗?

2021-03-10 07:47:31

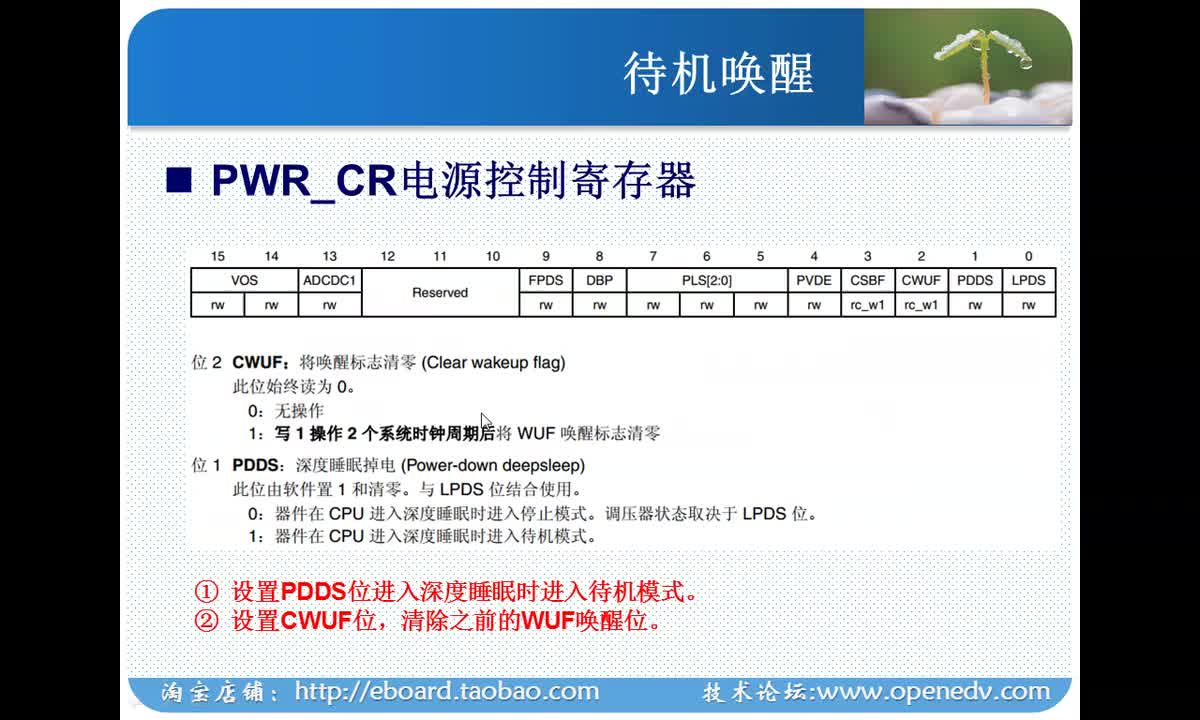

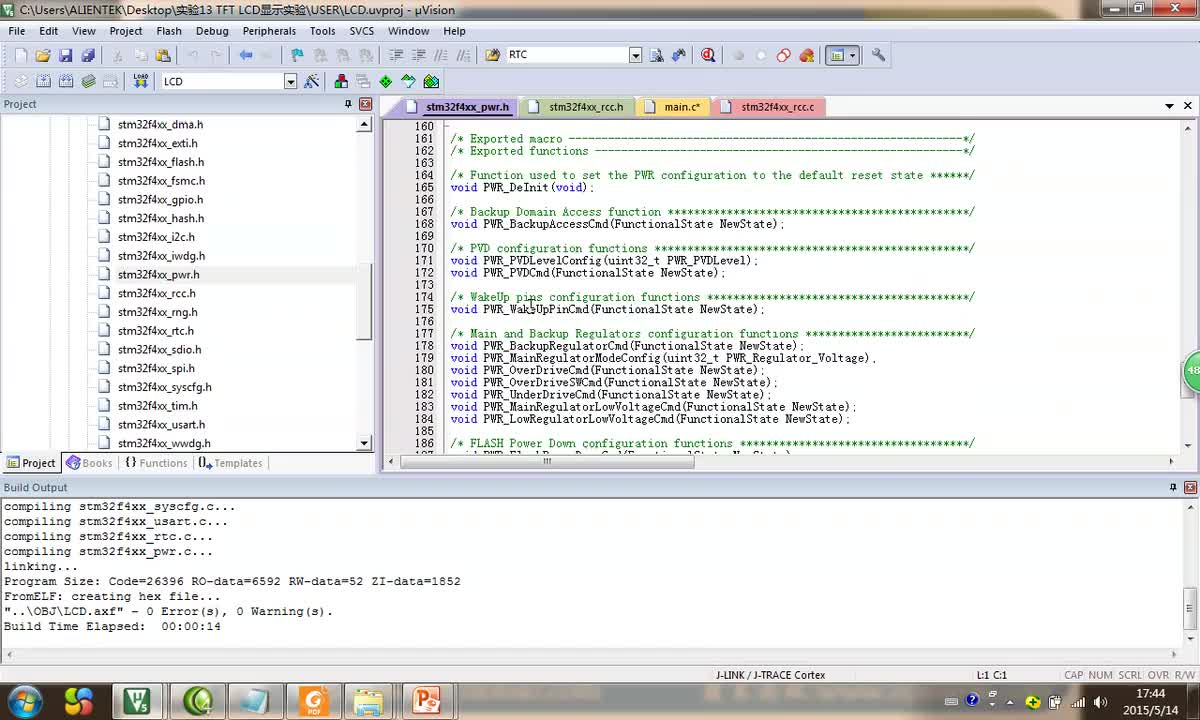

STM32是如何實現低功耗待機的?有哪些步驟?如何對STM32低功耗待機實現調試?

2021-10-11 06:08:06

TD MRR有哪些功能?TD MRR是如何提升網優效率的?

2021-05-28 07:25:48

TI bq25504高效率超低功耗能量采集解決方案

2018-08-29 17:45:35

TI針對能量采集和低功耗應用推出高效率電源轉換器_TPS6212075 mA DC/DC 降壓轉換器可支援 2 V 至 15 V 輸入電壓 靜態電流僅為 11 uA TI宣布針對能量采集和低功耗相關

2010-10-12 21:03:17

stm32進入低功耗之后外部iic連接的芯片不能工作是什么原因?求大神指點!!!順便有三種低功耗設置代碼可附上。謝謝!!!

2017-04-25 21:13:03

申請理由:目前需要板級驗證方案,驗證一些想法,并熟悉整個接收機的前端模塊的功能項目描述:目前的802.11abg等協議下,功耗依舊很高。因此需要考慮到低功耗的設計方案和思路。需要從電路級和系統級分別進行優化處理

2015-07-17 21:43:42

項目名稱:低功耗智能電表驗證 試用計劃:申請理由本人在嵌入式實時操作系統領域有五年多的工作和開發經驗,使用過uCOS、FreeRTOS、LiteOS等實時操作系統做項目開發,對實時操作系統技術有過

2020-03-11 15:35:19

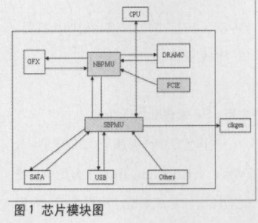

低功耗設計是芯片設計的關鍵技術,本視頻簡要介紹了SoC芯片設計中常見的低功耗設計技術,驗證難點。歡迎加入啟芯QQ群:275855756。 學習芯片設計,可以參考:啟芯SoC芯片設計系列課程

2013-11-03 08:44:06

什么是低功耗UPF?

2021-09-29 07:49:26

什么是低功耗廣域網?理想的低功耗廣域網屬性有哪些?

2021-05-14 06:09:36

高速、低功耗數據緩沖器為DDR5 DRAM及存儲類內存模塊提升速度與帶寬

2020-11-24 06:58:15

最近在開發一款單火取電的產品,通信模塊為Zigbee,大家有沒什么推薦的用于開態取電的效率高、低功耗芯片?

2016-06-15 17:17:07

單片機低功耗到底是什么?怎么才算是低功耗?

2021-11-01 06:02:49

芯片,選擇低電壓(低功耗器件)并聯調節器。調節器最好選用并聯調節器(噪聲低),適合小功率場所。或者使用開關電源芯片降壓,再使用LDO調節器減低噪聲,提高能量轉換效率(…)。選擇低電壓的并聯調節...

2021-11-10 08:04:40

1 單片機的低功耗設計技術1.1 高集成度的完全單片化設計將很多外圍硬件集成到了CPU芯片中,增大硬件冗余。內部以低功耗、低電壓的原則設計,這給單片機的低功耗設計提供了很強的支持。1.2 內部電路

2019-07-11 08:12:49

低功耗時產生線程調度能喚醒低功耗嗎(沒有中斷也能喚醒嗎)?大家一般在用操作系統的情況下怎么將低功耗喚醒的?感謝大家的幫助。

2020-07-24 08:01:28

在微功耗場景下,使用RCC是否比低功耗芯片的效率更高?設計例子:單火取電項目,從AC線取電取電,交流220V轉直流12V,再通過DC-DC方案,將12V轉為3.3V供Zigbee工作,該Zigbee

2016-06-17 13:50:42

結合采用低功耗元件和低功耗設計技術在目前比以往任何時候都更有價值。隨著元件集成更多功能,并越來越小型化,對低功耗的要求持續增長。當把可編程邏輯器件用于低功耗應用時,限制設計的低功耗非常重要。本文將討論減小動態和靜態功耗的各種方法,并且給出一些例子說明如何使功耗最小化。

2019-07-12 06:38:08

的高效率架構集成的硬件可在既不影響數據完整性或可靠性,又可降低功耗的情況下降低軟件復雜性,簡化安全系統設計。這樣,我們就可在低成本下將低功耗應用的安全性提升到全新的高度。作者簡介:Jacob

2014-09-01 17:44:09

根據電動口罩,紅外測溫儀以及血氧濃度儀這3個熱門應用提出了一種高效率的供電方案。解決方案主要針對1~2節干電池或單節鋰電池輸入的場景,提供了TI高效率低功耗的升壓解決方案。該方案可以提供低至

2022-11-08 08:04:20

作者:Monica Redon在物聯網(IoT)的推動下,業界對各種電池供電設備產生了巨大需求。這反過來又使業界對微控制器和其他系統級器件的能源效率要求不斷提高。因此,超低功耗(ULP)已成為一個

2019-07-22 08:29:36

現在我手上有一塊STM32L452RE的NUCLEO的板子,怎么驗證其在睡眠模式下的功耗是多少

2024-03-13 08:16:11

為什么需要低功耗設計?如何實現數字IC低功耗的設計?

2021-11-01 06:37:46

和傳統藍牙技術相比,低功耗藍牙技術的低功耗是如何實現的?

2021-05-18 06:23:30

如何設計一個高效率低功耗低噪聲的直流3V升壓到30V的電路?

電流1ma之內即可。

2023-11-16 06:36:14

隨著黑科技的發展,對便攜電子的功耗要求越來越高,相對于單片機性能要求它的功耗越來越低,很多單片機廠商都說自己的產品的低功耗單片機,又或者是超低功耗單片機,但是很多無法達到產品開發的低功耗需求

2021-01-19 16:21:33

在物聯網的推動下,業界對各種電池供電設備產生了巨大需求。這反過來又使業界對微控制器和其他系統級器件的能源效率要求不斷提高。因此超低功耗MCU與功耗相關的很多指標都不斷得刷新記錄。在選擇合適的超低功耗

2020-12-28 07:12:40

在物聯網的推動下,業界對各種電池供電設備產生了巨大需求。這反過來又使業界對微控制器和其他系統級器件的能源效率要求不斷提高。因此超低功耗MCU與功耗相關的很多指標都不斷得刷新記錄。在選擇合適的超低功耗

2021-11-04 07:07:56

??大家好,我是小政。本篇文章我將針對STM8L Active-halt模式下的低功耗進行詳細的講解,讓準備做低功耗產品的小伙伴能夠更好的理解在STM8L低功耗模式下運行,低功耗模式主要在各類

2022-02-21 07:32:21

電源封裝是TI 在此設計過程的重要組成部分。我們的創新封裝技術可用于改善成本、性能以及中低功耗應用,為 TI 以及我們的客戶實現差異化產品。例如,TI 最近推出的兩款反激式電源解決方案

2022-11-22 06:32:07

終端節點關閉低功耗模式和開啟低功耗模式,功耗有何區別?功耗相差多少?

2018-05-22 08:42:02

低功耗藍牙有哪些特性?低功耗藍牙有哪些技術?

2021-05-14 07:08:40

請問Cortex-M7內核的Cache是如何提升訪問效率的?

2022-01-26 08:23:55

FPGA Editor如何提升設計效率?如何利用CTRL / Shift快捷鍵進行放大縮小?如果利用F11鍵放大選定的項目?

2021-04-08 06:40:00

stm32進入低功耗模式,必須用中斷來喚醒,現在就是不用這種模式,如何通過程序來降低功耗啊

2019-05-06 18:43:22

在物聯網的推動下,業界對各種電池供電設備產生了巨大需求。這反過來又使業界對微控制器和其他系統級器件的能源效率要求不斷提高。因此,超低功耗(ULP)已成為一個過度使用的營銷術語,特別是用于描述微控制器

2019-07-18 07:42:18

本章介紹dsPIC30F器件系列的看門狗定時器(WDT)和低功耗模式。dsPIC DSC 器件有兩種低功耗模式,可以通過執行PWRSAV指令進入:• 休眠模式:CPU、系統時鐘源和任何依靠系統

2009-01-13 08:41:33 51

51 Tensilica 日前宣布與Cadence 合作,根據Tensilica 的330HiFi 音頻處理器和388VDO 視頻引擎,為其多媒體子系統建立一個通用功耗格式(CPF)的低功耗參考設計流程。Cadence 和Tensilica公司的工

2009-12-04 13:54:39 32

32 Cadence推出首個TLM驅動式設計與驗證解決方案

Cadence設計系統公司今天推出首個TLM驅動式協同設計與驗證解決方案和方法學,使SoC設計師們可以盡享事務級建模(TLM)的好處。

2009-08-07 07:32:00 674

674 Cadence推出首個TLM驅動式設計與驗證解決方案提升基于RTL流程的開發效率

Cadence設計系統公司推出首個TLM驅動式協同設計與驗證解決方案和方法學,使SoC設計師們可以盡

2009-08-11 09:12:18 499

499 Cadence為PCI Express 3.0推出首款驗證解決方案

Cadence設計系統公司宣布其已經開發了基于開放驗證方法學(OVM)的驗證IP(VIP)幫助開發者應用最新的PCI Express Base Specification

2009-11-04 16:59:59 1142

1142 中芯國際(SMIC)和Cadence共同推出用于65納米的低功耗解決方案Reference Flow 4.0

全球電子設計創新領先企業Cadence設計系統公司今天宣布推出一款全面的低功耗設計流程,面向

2009-11-04 17:05:17 589

589 SpringSoft運用先進的低功耗設計偵錯解決方案簡化低功耗芯片的驗證工作

全新的Verdi Power-aware Debug Module實現運用RTL與UPF/CPF低功耗設計

2010-02-08 19:17:37 779

779 芯邦采用Cadence Incisive Xtreme III系統提升SoC驗證實效

全球電子設計創新領先企業Cadence設計系統公司今天宣布,位于中國深圳的、無晶圓廠集成電路設計領先企業芯邦科

2010-03-02 10:32:47 573

573 Cadence設計系統公司600多種新功能擴展了指標驅動型驗證(MDV)的范圍,幫助工程師實現更快、更全面的驗證閉合與硅實現。

2011-01-13 11:26:17 768

768 Cadence Incisive Conformal ASIC是Incisive驗證平臺等效檢查解決方案的一部分,設計者無需測試向量就能驗證和調試數百萬門的設計。它組合了業界最優的等效檢查工具和擴展功能檢查,數據路

2011-04-13 23:40:45 17

17 電子設計創新企業Cadence設計系統公司(NASDAQ: CDNS)今天宣布,中國科學院計算技術研究所(簡稱計算所)采用了Cadence? Incisive?Xtreme Ⅲ? 系統,來加速其下一代6400萬門以上龍芯3號高級多

2011-05-27 10:49:34 646

646 Giantec最近采用Cadence軟件設計并成功流片了一款用于低功耗微控制器的存儲器產品,這款低功耗微控制器應用于智能卡、智能電表和消費電子產品。

2011-09-22 18:08:05 896

896 Cadence 設計系統公司日前宣布,汽車零部件生產商Denso公司在改用了Cadence定制/模擬與數字流程之后,在低功耗混合信號IC設計方面實現了質量與效率的大幅提升。將Cadence Encounter RTL-to-G

2012-09-04 09:31:59 811

811 電子設計創新企業Cadence設計系統公司,今天宣布使用ARM AMBA協議類型的Cadence驗證IP(VIP)實現多個成功驗證項目,這是業界最廣泛使用的AMBA協議系列驗證解決方案之一。頂尖客戶,包括

2012-11-07 08:21:52 997

997 9月24日——全球電子設計創新領先企業Cadence設計系統公司(NASDAQ: CDNS)今天宣布,Silicon Labs采用完整的Cadence? 混合信號低功耗設計流程,使其最新款節能型

2013-09-25 09:59:51 913

913 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ: CDNS)今天發布了新版 Incisive? 功能驗證平臺,再一次為整體驗證性能和生產率設定新標準。

2014-01-16 17:36:13 1047

1047 美國加州圣何塞,2014年9月30日 ─ 全球知名的電子設計創新領導者Cadence設計系統公司(NASDAQ: CDNS)今日宣布其豐富的IP組合與數字和定制/模擬設計工具可支持臺積電全新的超低功耗(ULP)技術平臺。

2014-10-08 19:24:35 907

907 “我們與 Cadence 密切合作開發參考流程,幫助我們的客戶加快其差異化的低功耗、高性能芯片的設計,”中芯國際設計服務中心資深副總裁湯天申博士表示,“Cadence創新的數字實現工具與中芯國際28納米工藝的緊密結合,能夠幫助設計團隊將28納米設計達到更低的功耗以及更快的量產化。”

2016-06-08 16:09:56 2242

2242 效率。Protium S1與Cadence? Palladium? Z1企業級仿真平臺前端一致,初始設計啟動速度較傳統FPGA原型平臺提升80%。

2017-03-02 11:13:11 2744

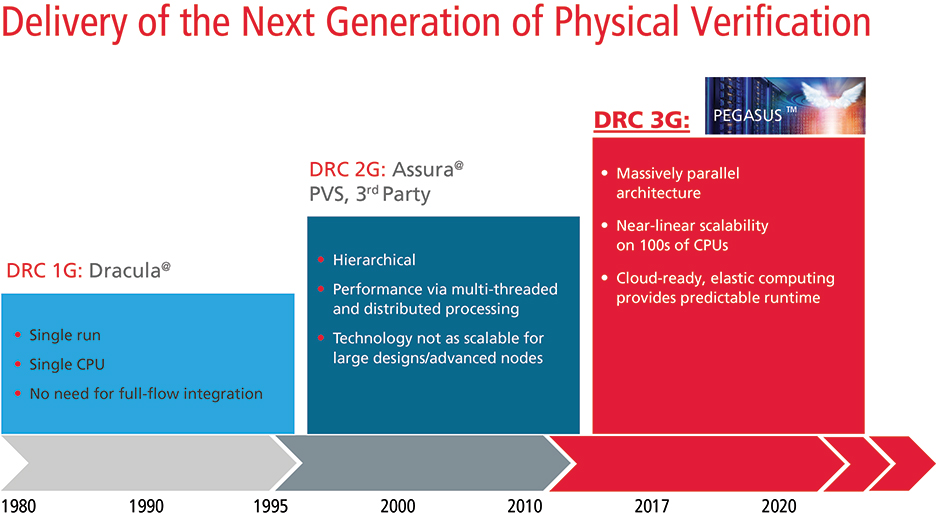

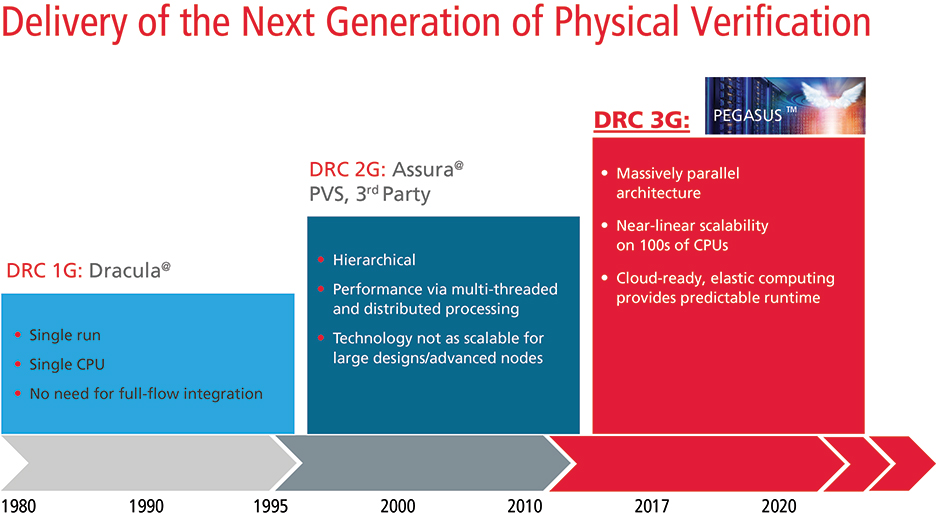

2744 將助工程師縮短先進節點IC的上市時間。Pegasus?驗證系統解決方案是全流程Cadence數字設計與簽核套件的新成員,可擴展至數百CPU,設計規則檢查(DRC)性能最高可提升10倍,周轉時間較上一代Cadence? 解決方案由數日降至數小時。

2017-04-14 15:42:44 1294

1294

功能驗證正成為IP 驗證的瓶頸,并影響到整個設計團隊。設計工程師想方設法提高驗證效率,以實現整個芯片設計的最佳利益。在這里,我們提供10 個簡單技巧,顯著提升您的IP 驗證效率。 1.參與驗證計劃

2017-10-19 09:17:23 8

8 Cadence Low-Power Solution是用于低功耗芯片的邏輯設計、驗證和實現的完全集成的、標準化的流程,將領先的設計、驗證和實現技術與Si2Common Power Format

2018-11-13 11:30:03 1357

1357 為了延長電子便攜式產品的電池使用時間,降低設計功耗變得越來越重要。在IC設計流程中,多種電源管理技術逐漸被應用,如clockgating,MSV(Multiple Supply Voltage),PSO(Power ShutOff)。然而這些低功耗技術的引入,對驗證工作帶來了很大的挑戰性。

2019-09-06 07:53:00 5313

5313

Spectre FX Simulator 仿真器采用全新架構,為加速存儲器和片上系統設計的驗證提供了變革性的創新。

2021-05-24 10:02:21 5703

5703 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布,SK hynix Inc. 已部署 Cadence? Spectre? FX Simulator 仿真器,用于對其面向 PC 和移動應用的 DDR4 和 DDR5 DRAM 進行基于 FastSPICE 的功能驗證。

2022-04-08 14:49:00 1565

1565 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布推出 Xcelium Apps,該系列技術基于 Cadence? Xcelium? Logic Simulator 內核原生實現,可為汽車電子、移動設備和超算系統等特定領域設計團隊帶來最強的驗證性能提升。

2022-06-30 10:27:52 1858

1858 在智能、移動等應用的驅動下,功耗帶來的問題日益突顯。多電壓、多電源、動態電源電壓控制等低功耗設計已是IC設計中采用的主流技術。低功耗設計方法學的不斷更新同時也帶來更多設計、驗證和實現上的挑戰

2022-11-02 18:13:46 469

469 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布,瑞薩電子(Renesas Electronics)已采用全新的人工智能(AI)驅動的 Cadence Verisium 驗證

2023-03-15 09:07:00 539

539 了 Cadence 在面對 SoC 設計驗證挑戰下的應對之法。 隨著 SoC 設計的發展,如何在有限的時間內盡可能發現更多的 bug 和實現更多的溯源分析,讓項目各方面的投資都做到物盡其用,這是驗證工作所面臨

2023-06-07 00:20:03 466

466

,NASDAQ:CDNS)近日宣布,DB GlobalChip 部署了 Cadence Spectre FX Simulator, 該工具與 Spectre AMS Designer 集成,用于驗證其關鍵的模擬

2023-06-25 12:25:02 512

512 。這些針對特定領域的應用可幫助客戶管理不斷增加的系統設計復雜性,提高系統級精度,并可加速低功耗驗證,尤其適用于一些先進的芯片領域,如人工智能和機器學習(AI/ML)、超大規模和移動通信。

2024-01-19 10:10:45 271

271

電子發燒友App

電子發燒友App

評論