隨著信號上升沿時間的減小及信號頻率的提高,電子產(chǎn)品的EMI問題越來越受到電子工程師的關(guān)注,幾乎60%的EMI問題都可以通過高速PCB來解決。以下是高速PCB設(shè)計抗EMI干擾的九大規(guī)則: 規(guī)則一:高速

2018-04-13 08:20:00 1567

1567

本文主要詳解PCB設(shè)計高速模擬輸入信號走線,首先介紹了PCB設(shè)計高速模擬輸入信號走線方法,其次闡述了九大關(guān)于PCB設(shè)計高速模擬輸入信號走線規(guī)則,具體的跟隨小編一起來了解一下。

2018-05-25 09:06:44 8394

8394

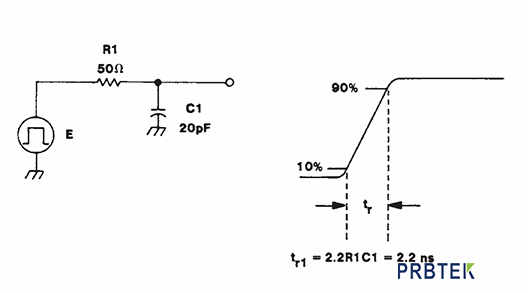

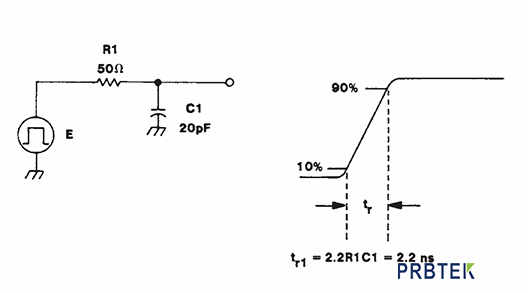

如果傳輸線阻抗50Ω,Cin=3pf,則τ10-90=0.33ns。如果信號的上升時間小于0.33ns,電容的充放電效應將會影響信號的上升時間。如果信號的上升時間大于0.33ns,這個電容將使信號上升時間增加越0.33ns

2022-06-28 15:51:47 4138

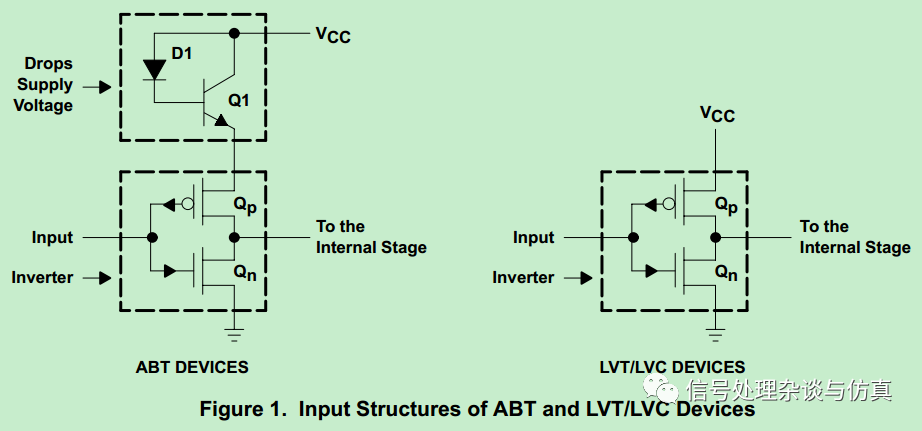

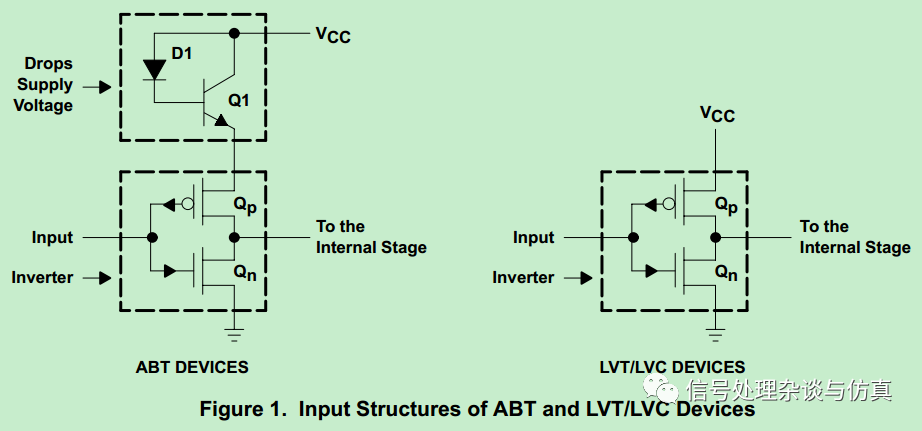

4138 CMOS器件的輸入信號上升時間或下降時間統(tǒng)稱為輸入轉(zhuǎn)換時間,輸入轉(zhuǎn)換時間過長也稱為慢CMOS輸入。如果輸入信號上升時間過長,超過器件手冊允許的最大輸入轉(zhuǎn)換時間,則有可能在器件內(nèi)部引起大的電流浪涌,造成器件損壞或引起器件輸出電平翻轉(zhuǎn)(輸入原本為0,輸出為1;或者相反情況)。

2023-10-31 10:39:53 560

560

,又如何判斷傳播延時是否大于20%驅(qū)動端的信號上升時間呢?信號上升時間的典型值一般可通過器件手冊查出,而信號的傳播時間在PCB設(shè)計中由實際布線長度和傳播速度決定。例如,“FR4”板上信號傳播速度大約

2018-11-27 15:21:01

PCB設(shè)計中跨分割的處理高速信號布線技巧

2021-02-19 06:27:15

請問大伙PCB設(shè)計中,常見的串口通訊線(TX、RX)是否屬于高速信號線?然后高速信號的標準到底是什么?在網(wǎng)上瀏覽了一些相關(guān)知識,感覺始終不太理解。

2023-01-26 20:39:13

傳輸線效應發(fā)生的前提條件,但是如何得知線延時是否大于1/2驅(qū)動端的信號上升時間? 一般地,信號上升時間的典型值可通過器件手冊給出,而信號的傳播時間在PCB設(shè)計中由實際布線長度決定。下圖為信號上升時間

2014-11-19 11:10:50

我們定義了傳輸線效應發(fā)生的前提條件,但是如何得知線延時是否大于1/2驅(qū)動端的信號上升時間? 一般地,信號上升時間的典型值可通過器件手冊給出,而信號的傳播時間在PCB設(shè)計中由實際布線長度決定。下圖為信號

2015-05-05 09:30:27

隨著信號上升沿時間的減小及信號頻率的提高,電子產(chǎn)品的EMI問題越來越受到電子工程師的關(guān)注,幾乎60%的EMI問題都可以通過高速PCB來解決。以下是九大規(guī)則:

2019-07-25 06:56:17

導讀:在目前的高速電路中,信號的上升時間已經(jīng)小于0.25ns,所以Len為0.25in,一般來說,PCB上走線的距離很容易大于這個值,所以,必須對電路進行端接設(shè)計。一般來說,當傳輸線很短時,傳輸延時

2015-01-23 13:58:45

高于多少MHZ以上就是高速。專家會告訴你,高速和信號上升沿有關(guān)系,當信號的上升時間和信號的傳輸延時可以比擬的時候,這就是高速設(shè)計。我們能找到各種公式,常見的有信號的上升時間小于6倍的傳輸延時,也有寫2

2014-10-21 09:41:25

高速PCB設(shè)計常見問題問: 高速系統(tǒng)的定義?/ 答: 高速數(shù)字信號由信號的邊沿速度決定,一般認為上升時間小于4 倍信號傳輸延遲時可視為高速信號。而平常講的高頻信號是針對信號頻率而言的。設(shè)計開發(fā)高速

2019-01-11 10:55:05

上升時間?一般地,信號上升時間的典型值可通過器件手冊給出,而信號的傳播時間在PCB設(shè)計中由實際布線長度決定。下圖為信號上升時間和允許的布線長度(延時)的對應關(guān)系。 PCB 板上每單位英寸的延時為

2018-08-24 17:07:55

和互連工具可以幫助設(shè)計師解決部分難題,但高速PCB設(shè)計也更需要經(jīng)驗的不斷積累及業(yè)界間的深入交流。 >>焊盤對高速信號的影響 在PCB中,從設(shè)計的角度來看,一個過孔主要由兩部分組成:中間

2012-10-17 15:59:48

本帖最后由 eehome 于 2013-1-5 09:53 編輯

高速PCB設(shè)計已成為數(shù)字系統(tǒng)設(shè)計中的主流技術(shù),PCB的設(shè)計質(zhì)量直接關(guān)系到系統(tǒng)性能的好壞乃至系統(tǒng)功能的實現(xiàn)。針對高速PCB

2012-03-31 14:29:39

`請問高速PCB設(shè)計規(guī)則有哪些?`

2020-02-25 16:07:38

隨著信號上升沿時間的減小及信號頻率的提高,電子產(chǎn)品的EMI問題越來越受到電子工程師的關(guān)注,幾乎60%的EMI問題都可以通過高速PCB來解決。以下是九大規(guī)則: 高速PCB設(shè)計解決EMI問題的九大規(guī)則

2016-01-19 22:50:31

在高速pcb設(shè)計中,經(jīng)常聽到要求阻抗匹配。而設(shè)計中導致阻抗不匹配的原因有哪些呢?一般又對應著怎么的解決方案?歡迎大家來討論

2014-10-24 13:50:36

、DSP系統(tǒng)的降噪技術(shù)2、POWERPCB在PCB設(shè)計中的應用技術(shù)3、PCB互連設(shè)計過程中最大程度降低RF效應的基本方法六、1、混合信號電路板的設(shè)計準則2、分區(qū)設(shè)計3、RF產(chǎn)品設(shè)計過程中降低信號耦合

2012-07-13 16:18:40

你好,如果跡線長度小于1/6等效長度的上升和下降時間,串聯(lián)終止。不需要。我需要知道我是否需要阻抗匹配的數(shù)據(jù)和控制線。我無法從數(shù)據(jù)表中找出GPIFII的上升時間。當做,阿薩夫 以上來自于百度翻譯

2019-05-28 14:46:26

能不能有大神 幫寫一個簡單測試上升時間的小程序。。

2017-09-20 14:47:33

PP7 引腳的上升時間

2023-04-21 08:01:32

嗨,我在一個自定義板上使用了一個UB2517i集線器。我的問題是關(guān)于電源上升時間:在數(shù)據(jù)表(第8.2章)中,Microchip指定最大電源上升時間為400。我不能保證這個上升時間在我的設(shè)計中。我只能

2018-11-20 15:32:54

本帖最后由 7七同學 于 2015-5-8 10:25 編輯

哪位大神知道怎樣使用labview編程算出如圖所示信號上升時間

2015-05-07 16:40:08

與理想方波越接近。同理降低信號帶寬如刪除高頻分量,其上升時間會變長。有兩種損耗機理:導體損耗和介質(zhì)損耗。這兩種損耗對高頻分量的衰減大于對低頻分量的衰減。這種選擇性衰減使得在互連線中傳播的信號的帶寬降低

2017-12-01 09:55:07

使用LABview如何計算一個波形的上升時間,初學好多控件不清楚,請大神指點

2017-09-06 15:44:45

各位大神好: 小弟現(xiàn)在想使用Labview計算階躍信號響應的上升時間和穩(wěn)定時間,不知道該從哪下手,有知道的請指教一二,多謝啊!

2017-03-16 13:50:34

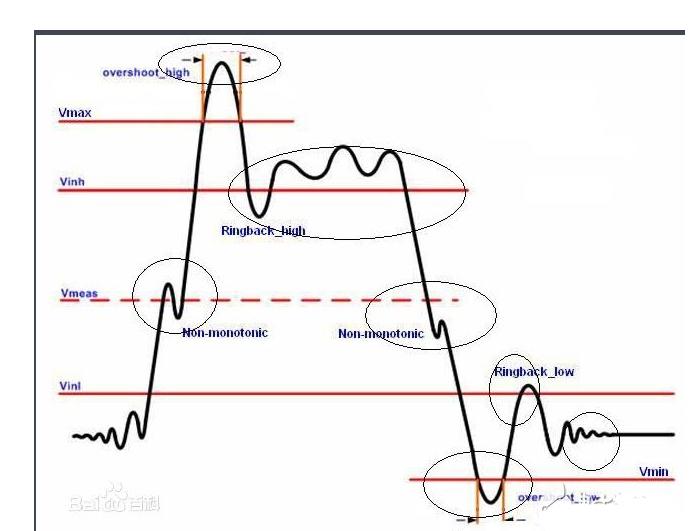

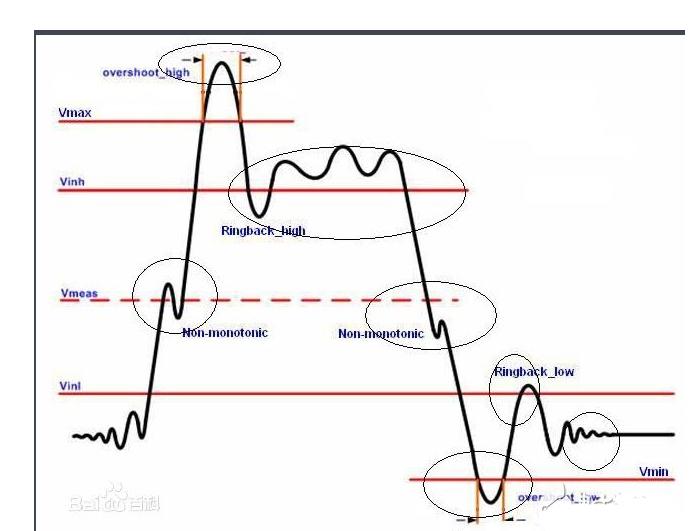

的時延有關(guān),《信號完整性分析》中描述說,“當傳輸線延時Td>信號上升時間的20%時,就要開始考慮由于導線沒有終端端接而產(chǎn)生的振鈴噪聲。當時延大于上升時間的20%時,振鈴會影響電路功能,,必須加以控制,否則這是造成信號完整性問題的隱患。吐過Td

2019-05-22 06:07:06

在高速PCB設(shè)計中,PCB的層數(shù)多少取決于電路板的復雜程度,從PCB的加工過程來看,多層PCB是將多個“雙面板PCB”通過疊加、壓合工序制造出來的,但多層PCB的層數(shù)、各層之間的疊加順序及板材選擇

2017-03-01 15:29:58

在高速PCB設(shè)計中,過孔有哪些注意事項?

2021-04-25 09:55:24

圖解在高速的PCB設(shè)計中的走線規(guī)則

2021-03-17 07:53:30

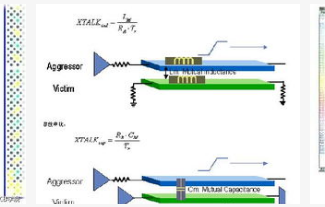

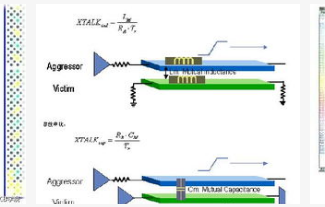

要盡可能減小不同性質(zhì)信號線之間的并行長度,加寬它們之間的間距,改變某些線的線寬和高度。當然,影響串擾的因素還有許多,比如電流流向、干擾源信號頻率上升時間等,應綜合考慮。結(jié)語在本次控制單元高速PCB設(shè)計中

2015-01-07 11:30:40

或是超過45MHz至50MHz,而且工作在這個頻率之上的電路已經(jīng)占到了整個系統(tǒng)的三分之一,就稱為高速電路.另外從信號的上升與下降時間考慮,當信號的上升時間小于6倍信號傳輸延時時即認為信號是高速信號

2018-11-22 16:03:30

解決高速PCB設(shè)計信號問題的全新方法

2021-04-25 07:56:35

高速數(shù)字PCB設(shè)計信號完整性解決方法

2021-03-29 08:12:25

我想要在信號之間進行一些串擾計算,并且我試圖找到STM32F768IIT6的最小上升時間 - 我看到的是指定測試條件下的最大上升/下降時間。我查看了數(shù)據(jù)表和參考手冊,但我能找到的最大上升/下降時間

2018-09-27 14:21:17

1 示波器探頭的上升時間和帶寬示波器主要的限制為三個方面:靈敏性的不足、輸入電壓的幅度不夠大、帶寬限制。只要數(shù)字測試中的靈敏度不是特別的高,一般示波器的靈敏度是滿足要求的。在高電平時,數(shù)字信號一般

2018-04-19 10:42:59

對于高速信號,pcb的設(shè)計要求會更多,因為高速信號很容易收到其他外在因素的干擾,導致實際設(shè)計出來的東西和原本預期的效果相差很多。 所以在高速信號pcb設(shè)計中,需要提前考慮好整體的布局布線,良好

2023-04-12 14:22:25

關(guān)于PCB布線的臨界長度,查到經(jīng)驗數(shù)據(jù)是:當信號在pcb走線上的時延高于信號上升沿的20%時,信號會產(chǎn)生明顯的振鈴。然后還有個例子:對于上升時間為1ns的方波信號來說,pcb走線長度為0.2*6

2016-06-29 15:19:01

在一般的非高速PCB設(shè)計中,我們都是認為電信號在導線上的傳播是不需要時間的,就是一根理想的導線,這種情況在低速的情況下是成立的,但是在高速的情況下,我們就不能簡單的認為其是一根理想的導線了,電信號

2019-05-30 06:59:24

怎么測量 信號的上升時間?

2015-03-15 08:36:34

,top_threshold_pct)來通過瞬態(tài)模擬來測量信號的上升時間。我想掃描輸入頻率并測量每個輸出的上升時間。使用掃描時,此功能似乎失敗。有解決方法嗎?我意識到,雖然滲透頻率,我的數(shù)據(jù)輸出是一個二維數(shù)組,如果我通過使用y

2018-09-26 15:12:33

我用信號發(fā)生器產(chǎn)生了一個1MHz 上升時間5ns的脈沖,用示波器測出來上升時間已經(jīng)10+ns,是什么原因造成的呢

2016-07-17 12:17:15

與帶寬選擇依據(jù)類似。在帶寬中,由于當前信號擁有超高速率,并不能一直實現(xiàn)這種經(jīng)驗法則。注意,示波器上升時間越快,捕獲快速跳變關(guān)鍵細節(jié)的精度越高。 在某些應用中,您可能知道信號的上升時間。有一個常數(shù),可以把

2016-04-11 14:38:38

如圖本仿真電路,設(shè)定上升時間為100ns,仿真結(jié)果可以看出兩個輸出波形上升沿差出100ns,這正是我們設(shè)計出本電路預期達到的效果,但是在用洞洞板焊接測試版后,發(fā)現(xiàn)上升沿相差變?yōu)樵瓉淼?/2,信號

2017-07-19 10:35:05

隨著信號上升沿時間的減小及信號頻率的提高,電子產(chǎn)品的EMI問題越來越受到電子工程師的關(guān)注,幾乎60%的EMI問題都可以通過高速PCB來解決。以下是九大規(guī)則:規(guī)則一:高速信號走線屏蔽規(guī)則在高速

2017-11-02 12:11:12

什么是高速pcb設(shè)計高速線總體規(guī)則是什么?

2019-06-13 02:32:06

時間和頻率的關(guān)系是什么輸入電容對上升時間和噪聲的影響是什么進行電平測量時需要考慮的速度問題

2021-04-15 06:24:37

在我看來,當我增加驅(qū)動強度時,例如:更改以下約束:NET“net_name”drive = 2;至NET“net_name”drive = 16;信號的上升時間會減少。我通過DSO(數(shù)字式振蕩器

2019-07-10 08:05:28

摘要:包含2線總線(例如:I²C或SMBus™)的應用需要在上升時間、電源損耗、噪聲抑制等參數(shù)之間做出折中。這種漏極開路總線從低電平跳變到高電平的上升時間由上拉電阻和總

2009-04-27 14:29:58 22

22 高速信號走線規(guī)則教程

隨著信號上升沿時間的減小,信號頻率的提高,電子產(chǎn)品的EMI問題,也來越受到電子工程師的關(guān)注。高速PCB設(shè)計的成功,對EMI

2009-04-15 08:49:27 2798

2798

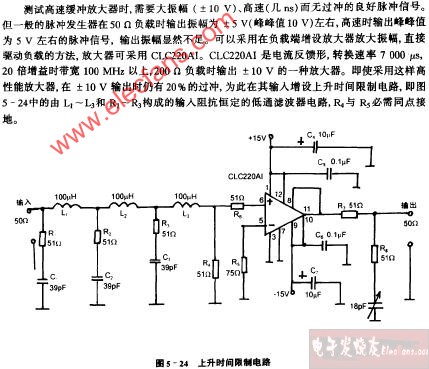

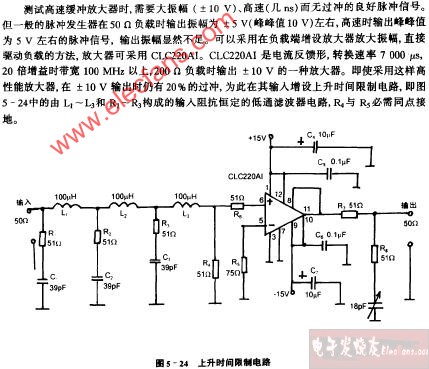

上升時間限制電路圖

2009-07-15 16:43:39 519

519

基于Cadence的高速PCB設(shè)計

隨著人們對通信需求的不斷提高,要求信號的傳輸和處理的速度越來越快.相應的高速PCB的應用也越來越廣,設(shè)計也越來越

2009-12-12 17:50:27 954

954 BOB購買了一臺標稱300MHZ的示波器,探頭的標稱值是300MHZ,兩個指標均為3DB帶寬。問:對于上升時間為2NS的信號,這個組合信號的影響如何?

2010-06-03 16:20:14 779

779

BOB購買了一臺標稱300MHZ的示波器,探頭的標稱值是300MHZ,兩個指標均為3DB帶寬。問:對于上升時間為2NS的信號,這個組合信號的影響如何?

2010-07-05 11:44:24 2072

2072

隨著信號上升時間(下降時間)越來越短, PCB 的RE越來越嚴重,已逐步成為影響產(chǎn)品EMC性能的重要因素之一,PCB設(shè)計過程中必須采取綜合措施抑制RE。從高速高密度PCB設(shè)計的角度,總結(jié)

2011-08-15 10:41:53 0

0 本文就談談一個基礎(chǔ)概念:信號上升時間和信號帶寬的關(guān)系。對于數(shù)字電路,輸出的通常是方波信號。方波的上升邊沿非常陡峭,根據(jù)傅立葉分析,任何信號都可以分解成一系列不同頻

2011-11-30 15:48:44 3607

3607

信號完整性分析及其在高速PCB設(shè)計中的應用,教你如何設(shè)計高速電路。

2016-04-06 17:29:45 15

15 快速上升時間多諧振蕩器原理圖都是值得參考的設(shè)計。

2016-05-11 17:00:47 18

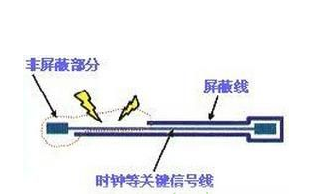

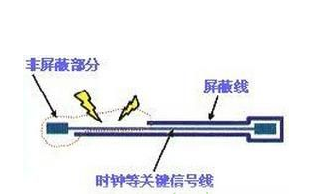

18 規(guī)則一:高速信號走線屏蔽規(guī)則 在高速的PCB設(shè)計中,時鐘等關(guān)鍵的高速信號線,走線需要進行屏蔽處理,如果沒有

2017-11-25 07:43:00 7511

7511

超過45MHz至50MHz,而且工作在這個頻率之上的電路已經(jīng)占到了整個系統(tǒng)的三分之一,就稱為高速電路.另外從信號的上升與下降時間考慮,當信號的上升時間小于6倍信號傳輸延時時即認為信號是高速信號,此時考慮的與信號的具體頻率無關(guān). 2 高速

2017-12-01 12:35:47 233

233

信號上升時間并不是信號從低電平上升到高電平所經(jīng)歷的時間,而是其中的一部分。業(yè)界對它的定義尚未統(tǒng)一,最好的辦法就是跟隨上游的芯片廠商的定義,畢竟這些巨頭有話語權(quán)。

2018-04-11 11:16:00 8090

8090

信號上升時間并不是信號從低電平上升到高電平所經(jīng)歷的時間,而是其中的一部分。業(yè)界對它的定義尚未統(tǒng)一,最好的辦法就是跟隨上游的芯片廠商的定義,畢竟這些巨頭有話語權(quán)。通常有兩種:第一種定義為10-90

2019-06-26 15:40:06 1515

1515

關(guān)注的問題,當時TTL足夠快,路徑變長。這就是我們?nèi)绾卧?b class="flag-6" style="color: red">信號完整性方面定義高速度;當信號路徑相對于上升時間較長時,PCB是高速的,當信號從開放端反射并導致問題時,路徑變長。

2019-07-28 10:08:13 3799

3799 GHz速率級別的信號算高速? 傳統(tǒng)的SI理論對于高速信號有經(jīng)典的定義。 SI:Signal Integrity ,即信號完整性。 SI理論對于PCB互連線路的信號傳輸行為理解,信號邊沿速率幾乎完全決定了信號中的最大頻率成分,通常當信號邊沿時間小于4~6倍的互連傳輸延時的情況

2019-11-05 11:27:17 10310

10310

隨著信號上升沿時間的減小,信號頻率的提高,電子產(chǎn)品的EMI問題,也來越受到電子工程師的重視。高速pcb設(shè)計的成功,對EMI的貢獻越來越受到重視,幾乎60%的EMI問題可以通過高速PCB來控制解決。

2020-03-25 15:55:28 1400

1400

高速PCB設(shè)計是指信號的完整性開始受到PCB物理特性(例如布局,封裝,互連以及層堆疊等)影響的任何設(shè)計。而且,當您開始設(shè)計電路板并遇到諸如延遲,串擾,反射或發(fā)射之類的麻煩時,您將進入高速PCB設(shè)計領(lǐng)域。

2020-06-19 09:17:09 1537

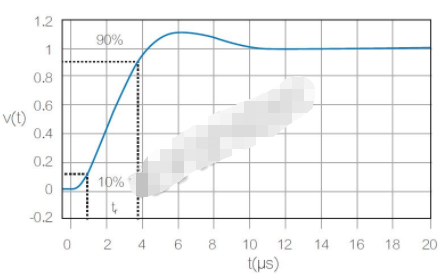

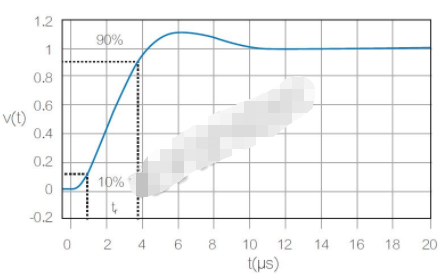

1537 我們先來看一下壓擺率,壓擺率的概念與上升時間類似,但有一些重要區(qū)別。如圖1所示,階躍響應的上升時間被定義為波形從終值的10%變?yōu)?0%所需的時間。(有時上升時間被定義為20/80%。)請注意,上升時間通過波形大小的百分比來定義,與所涉及的電壓無關(guān)。例如圖1中的波形具有大約3μs的上升時間。

2020-09-29 11:54:10 1858

1858

振蕩上升時間(start up time)是指IC電源啟動時,從振蕩過渡的狀態(tài)向恒定區(qū)移動所需的時間,村田的規(guī)定是達到恒定狀態(tài)的振蕩水平的90%的時間。 振蕩上升時間受振蕩電路中使用的元件的影響,與晶體諧振器相比較的話,CERALOCK的振蕩上升時間會快1位數(shù)到2位數(shù)。 編輯:hfy

2021-03-31 10:21:05 2667

2667 在高速PCB設(shè)計中,“信號”始終是工程師無法繞開的一個知識點。不管是在設(shè)計環(huán)節(jié),還是在測試環(huán)節(jié),信號質(zhì)量都值得關(guān)注。

2020-11-20 10:55:07 3418

3418 在高速PCB設(shè)計中,差分信號的應用越來越廣泛,這主要是因為和普通的單端信號走線相比,差分信號具有抗干擾能力強、能有效抑制EMI、時序定位精確的優(yōu)勢。

2021-03-23 14:40:47 2760

2760 EE-71:ADSP-21x1/21x5上關(guān)鍵中斷和時鐘信號的最小上升時間規(guī)格

2021-04-22 15:09:42 3

3 高速電路信號完整性分析與設(shè)計—PCB設(shè)計1

2022-02-10 17:31:51 0

0 高速電路信號完整性分析與設(shè)計—PCB設(shè)計2

2022-02-10 17:34:49 0

0 至50MHz,而且工作在這個頻率之上的電路已經(jīng)占到了整個系統(tǒng)的三分之一,就稱為高速電路。另外從信號的上升與下降時間來考慮,當信號的上升時間小于6倍信號傳輸延時時即認為信號是高速信號,此時考慮的與信號的具體頻率無關(guān)。

2022-05-27 16:45:11 0

0 如果傳輸線阻抗50Ω,Cin=3pf,則τ10-90=0.33ns。如果信號的上升時間小于0.33ns,電容的充放電效應將會影響信號的上升時間。如果信號的上升時間大于0.33ns,這個電容將使信號上升時間增加越0.33ns

2022-06-06 14:39:34 3638

3638 隨著信號頻率或轉(zhuǎn)換速率提高,阻抗的電容成分變成主要因素。結(jié)果,電容負荷成為主要問題。特別是電容負荷會影響快速轉(zhuǎn)換波形上的上升時間和下降時間及波形中高頻成分的幅度,那么示波器探頭對測量電容負荷有哪些影響呢?

2022-06-28 16:18:20 3058

3058

您是否在準確測定氮化鎵器件的皮秒量級上升時間?

2022-11-04 09:51:25 0

0 在高速信號的設(shè)計中,一般考慮的并不是信號的周期頻率F,一般是有效頻率F1,T代表信號的時鐘周期,T1代表信號的10%-90%的上升時間。

2022-12-26 10:50:42 1992

1992 包含2-Wire總線的應用(如I2C或SMBus?)需要在上升時間、功耗和抗擾度之間進行權(quán)衡。由于這種漏極開路總線上從低到高轉(zhuǎn)換的上升時間由上拉電阻和總線電容決定,因此在添加外設(shè)、布線走線和連接器

2023-01-16 11:09:10 817

817

由信號頻率升高、上升時間減小所引起PCB互連線上的所有信號質(zhì)量問題都屬于信號完整性的研究范疇。本論文的主要研究可概括為傳輸線在PCB設(shè)計制造過程中所產(chǎn)生的信號完整性問題,具體分為三個方面

2023-03-27 10:40:30 0

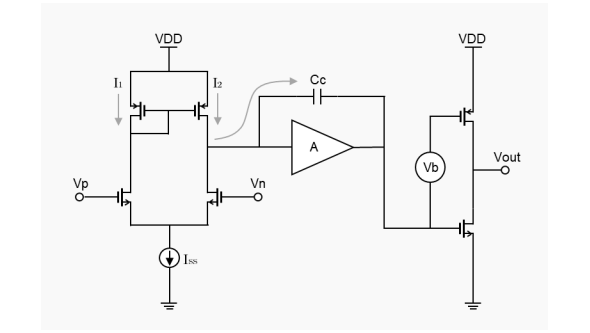

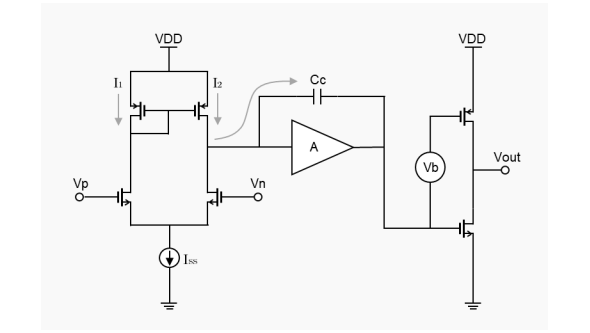

0 本文介紹了運放電路帶寬增益積 和壓擺率 對運放輸出電壓上升時間的影響,評估運放輸出電壓的上升時間,一般采用輸出電壓的 10% ~ 90% 這一段時間作為上升時間。

2023-04-27 09:26:25 510

510

在現(xiàn)代電子設(shè)計中,高速信號的傳輸已成為不可避免的需求。高速信號傳輸?shù)某晒εc否,直接影響整個電子系統(tǒng)的性能和穩(wěn)定性。因此,PCB設(shè)計中的高速信號傳輸優(yōu)化技巧顯得尤為重要。本文將介紹PCB設(shè)計中的高速信號傳輸優(yōu)化技巧。

2023-05-08 09:48:02 1143

1143 在電路選型運算放大器時,用戶經(jīng)常比較關(guān)心運放輸出電壓的上升時間是如何計算的,上升時間到底與運放的帶寬增益積GBW有關(guān),還是與運放的壓擺率SR有關(guān),還是某些時候與兩者同時都存在一定的約束關(guān)系?

2023-05-18 11:37:58 901

901

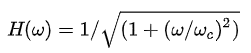

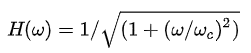

對于任意一個LTI系統(tǒng),都有自己的瞬態(tài)響應過程,響應的快慢取決于系統(tǒng)帶寬,一般使用上升時間衡量。

2023-06-12 15:54:39 701

701

可以很好的決定布線的走向和結(jié)構(gòu),電源與地之間的分割,以及電磁干擾和噪聲的控制。 不過在理解高速PCB設(shè)計前,需要知道什么是高速信號。 一般如果符合以下幾點,那它就可以被認為是高速信號(cadence公司做的定義): (1)頻率大于

2023-11-06 10:04:04 341

341

信號頻率和上升時間的關(guān)系? 信號頻率和上升時間是電子領(lǐng)域中兩個常用的概念。它們之間的關(guān)系是比較密切的,一個信號的頻率越高,它的上升時間就會越短。在本文中,我將會詳細介紹信號頻率和上升時間的相關(guān)知識

2023-11-06 11:01:07 1546

1546 在高速PCB設(shè)計中,信號層的空白區(qū)域可以敷銅,而多個信號層的敷銅在接地和接電源上應如何分配? 在高速PCB設(shè)計中,信號層的空白區(qū)域可以敷銅,而多個信號層的敷銅在接地和接電源上應該經(jīng)過合理分配。接地

2023-11-24 14:38:21 635

635

電子發(fā)燒友App

電子發(fā)燒友App

評論