芯片近些年來一直是風口,幾乎所有有實力的上市公司都要蹭下這個熱度:自研芯片。這也誕生了很多工作崗位,相對于硬件工程師,軟件開發工程師能做的事情有限,但是也是非常重要的,而且跟著風口喝口湯也是可以的。整體來說:需求、架構、驗證是需要軟件參與的,本文結合自己的部分經驗,從最基本的芯片設計流程進行介紹,其中會涉及一些可能你經常聽到的卡脖子技術。

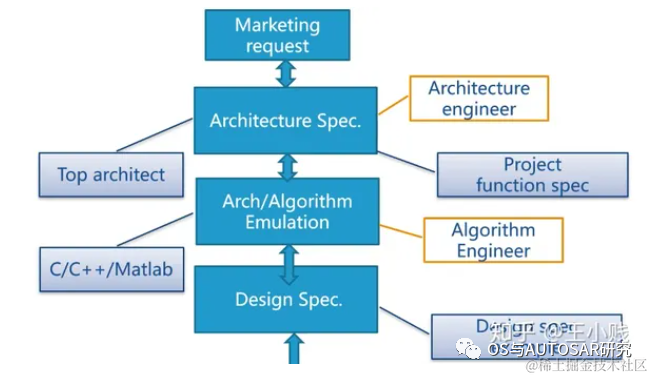

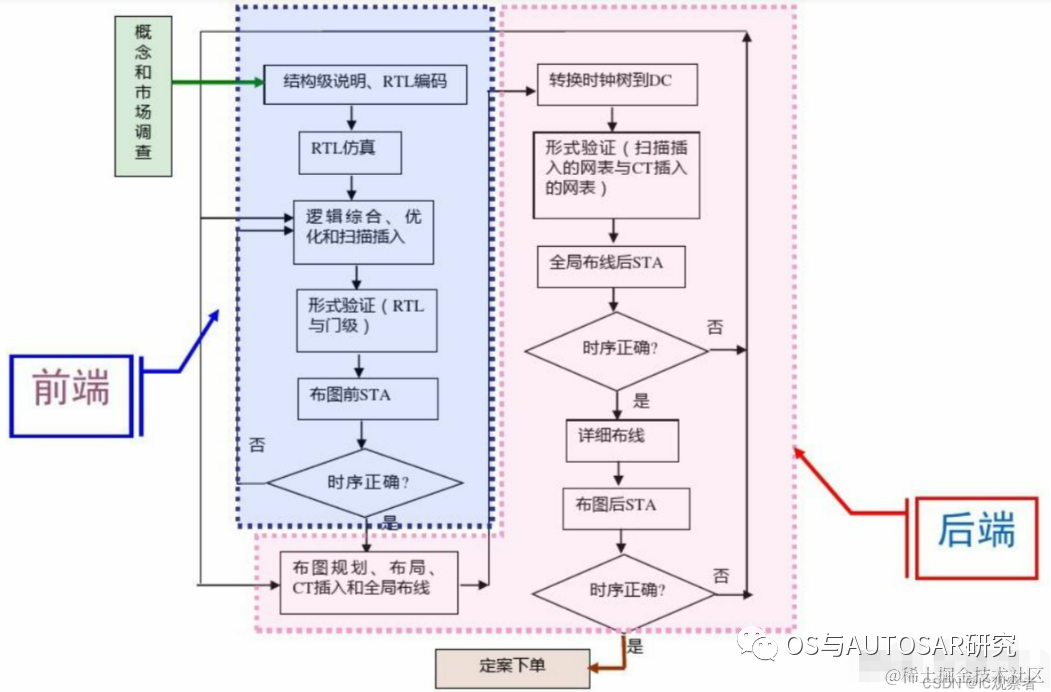

芯片設計的四個步驟,如上圖,我們只關注需求和設計,制造和封裝不是我們軟件工程師能左右的。

1. 市場需求

要做一個芯片,首先得有需求,也就是應用場景,有市場去買單。當前科技時代,電子技術在各方面都有應用,可以說有電路板的地方就有芯片需求。例如手機、電腦、智能家具,我們的衣食住行用等方方面面。

有了需求,就可以根據需求梳理出來我們硬件上需要那些模塊功能和性能指標,以及軟硬件上要用的技術。這些需要軟硬件的架構師進行設計,最終形成Spec。 Spec會確定所有的功能和要求,之后才可以進行芯片設計。

軟件在做架構設計的時候,有時候需要進行一些驗證,看軟件是否支持,可以使用qemu模擬運行的方式看應用能支持不。

軟硬件在做架構設計的時候,可以使用很多IC廠商提供的IP集成工具來模擬SoC,就是用純軟件的方式把SoC上的各個IP都添加模擬出來,例如VDK(Virtualizer Development Kit)工具。

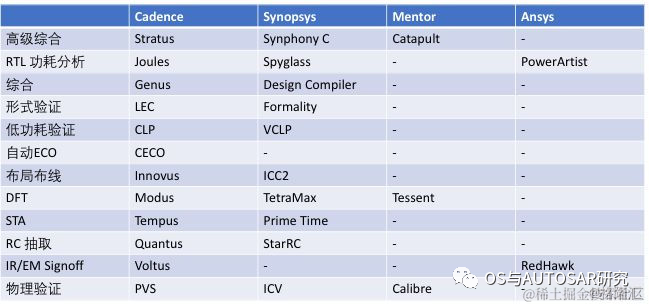

這里說的VDK工具,其實就是一種電子設計自動化EDA(Electronics Design Automation)工具,也就是我們俗稱的EDA工具。這是我們卡脖子的技術之一,很復雜,而在芯片設計中非常的重要,貫穿設計、驗證和制造,特別是驗證可以大力減少出錯成本和縮短研發周期。可謂“沒有金剛鉆,不攬瓷器活”。詳細可以參考:淺談EDA驗證工具,芯片開發到底有多難?

VDK與qemu的區別就是qemu支持的芯片型號有限,自己添加很麻煩,要修改qemu的源碼。而在VDK圖形界面上點一點就可以添加一個IP,而且很多IP是不出名的,廠商私有的不會廣泛支持,就需要自己加。所以IP廠商基本會有自己的集成驗證工具供客戶使用。

芯片開發的周期很漫長,在最開始需求階段,一些應用上的軟件也許就具備開發條件了,例如在qemu上進行app應用的開發,一些依賴于SoC上IP的應用,可以使用VDK做一些數據流的通路開發,并不支持具體的業務,這樣后續拿到真正芯片后就可以省略很多一部分研發任務,并且可以提前驗證軟件技術方案的可行性。 如果軟件技術方案不可行需要修改SoC硬件也可以及早的修改。因為芯片研發越到后期修改的成本越大,如果流片了還需要修改,那就快game over了,巨額資金打水漂。所以寧愿先投入研發人員去慢慢磨,也不愿意在硬件上去試錯,人可沒芯片生產值錢。

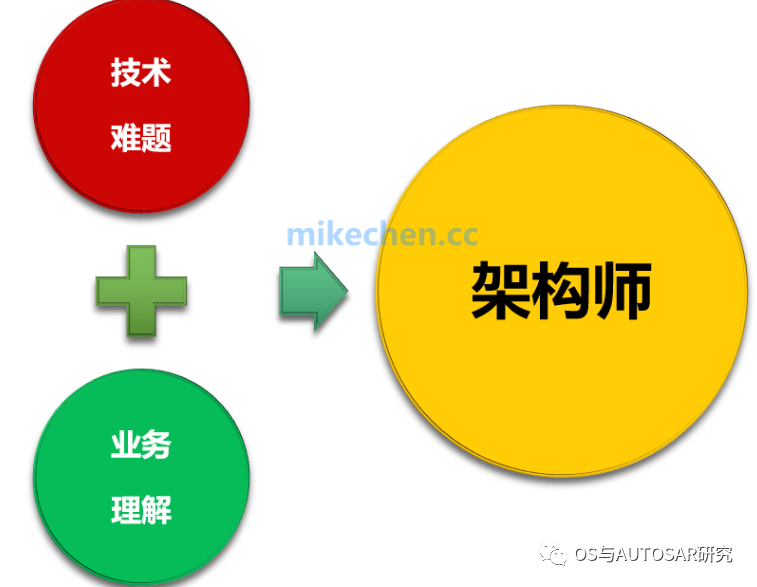

1.2 關于架構師

數字集成電路設計實現流程是個相當漫長的過程,拿手機基帶芯片為例,對于3G, 4G, 5G, 工程師最初見到的是無數頁的協議文檔。

架構師要根據協議來確定:協議的哪些部分可以用軟件實現,哪些部分需要用硬件實現;

算法工程師要深入研讀協議的每一部分,并選定實現所用算法;

芯片設計工程師,需要將算法工程師選定的算法,描述成RTL;

芯片驗證工程師,需要根據算法工程師選定的算法設計測試向量,對RTL 做功能、效能驗證;

數字實現工程師,需要根據算法工程師和設計工程師設定的目標PPA 將RTL 揉搓成GDS;

芯片生產由于太過復雜,完全交由代工廠完成,封裝亦是;

對于測試,大部分公司都是租借第三方測試基臺由自己的測試工程師完成,只有少部分土豪公司才會有自己的測試基臺。

架構師是芯片靈魂的締造者,是食物鏈的最頂端,是牛逼閃閃的存在。

2. 芯片設計概述

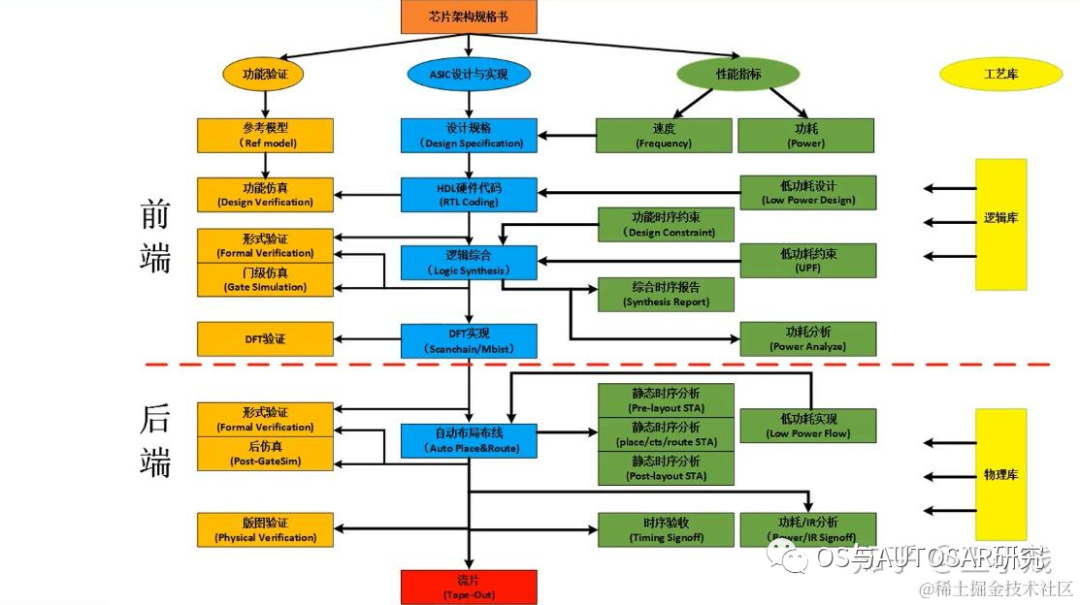

芯片設計分為兩部分,前端(邏輯設計)和后端(物理設計)。

?

? 這其中很多流程看似高大上,但是有IP供應商提供的工具以后,其實就是界面上點點的事情。 芯片設計中涉及的工具繁多,基本都是老外的,這需要國內芯片公司的崛起,有自己的很多IP后才可以投入到這些工具的研發中去。

有一個說法就是老外掌握一項新技術,首先就是加密做界面化,不提供源碼然后商業賣錢。而這個周期要延遲一兩年到市場上,而中國則直接推給自己的客戶,客戶有能力抄的就抄跑了,大家都不太注重商業保密,可能技術比較low不用藏著掖著,大家都是抄的。。。這就是中國速度。

3. 芯片前端設計

RTL設計

驗證

靜態時序分析

覆蓋率

ASIC邏輯綜合

3.1 RTL設計

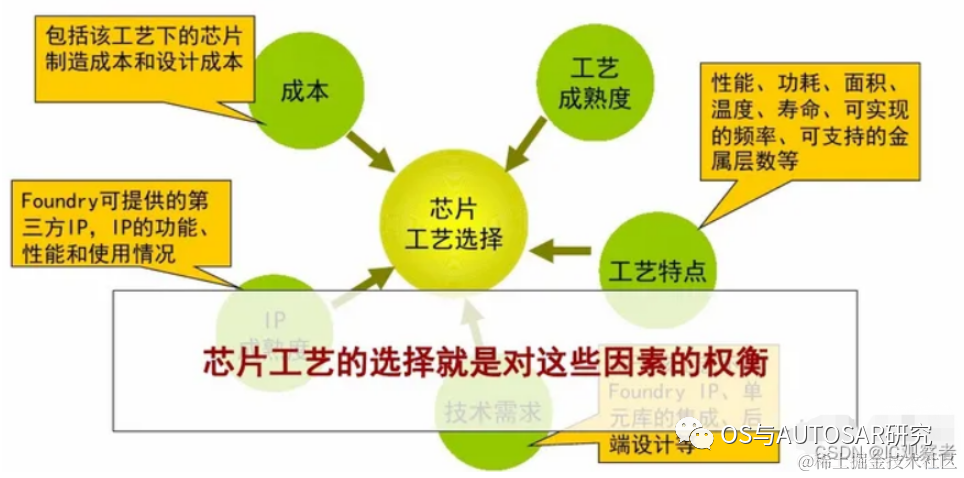

首先要確定芯片的工藝,如下圖:

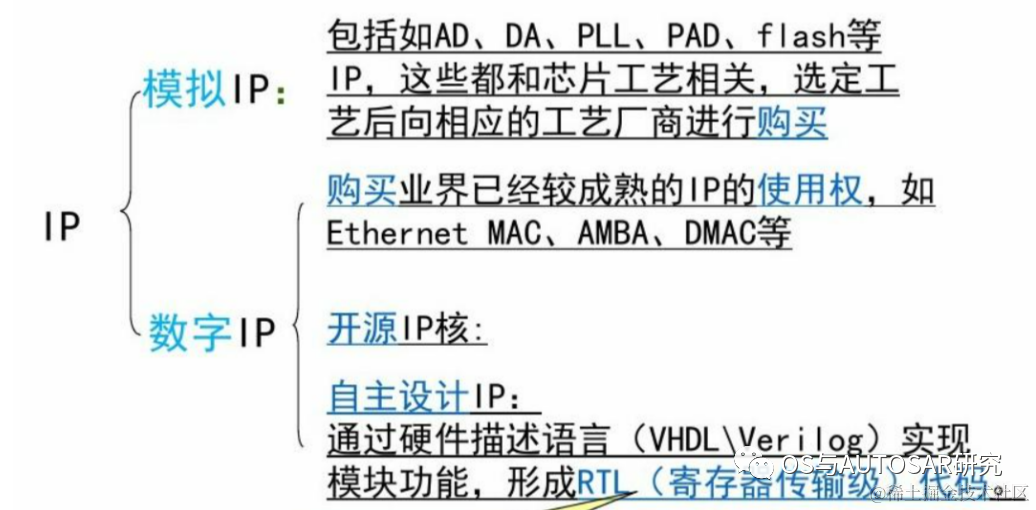

RTL(register transfer level) 設計:利用硬件描述語言,如VHDL,Verilog,System Verilog, 對電路以寄存器之間的傳輸為基礎進行描述。 RTL使用代碼編寫,來實現功能模塊,就是一個個IP。這些IP分為數字IP和模擬IP:

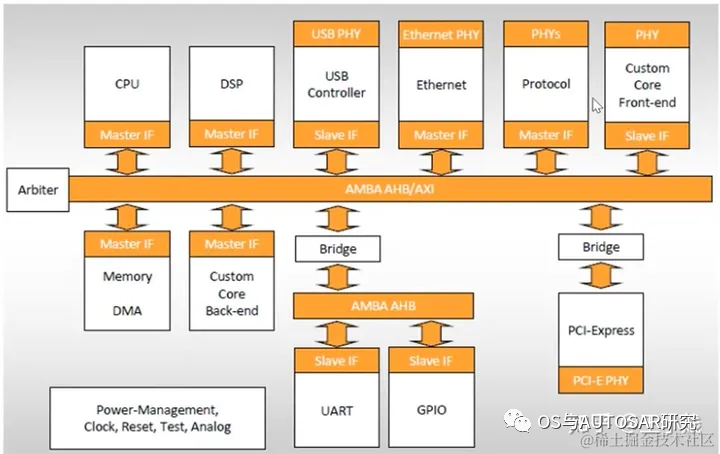

SOC芯片最終由SOC integration工程師把各個IP集成到一起。

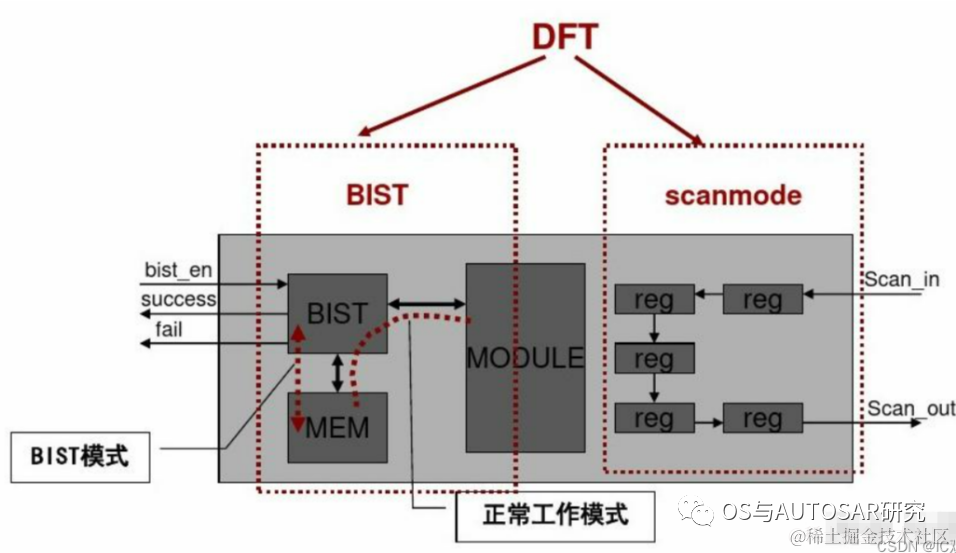

上圖中我們可以看到一個典型的SoC有那些IP,例如CPU,DSP,USB外設,memory等。 對于RTL還需要進行支持BIST(自測試),設計的時候也需要做可測性設計DFT(Design For Test)

除了對功能測試,還需要對代碼進行自動檢查:通過lint, Spyglass等工具,針對電路進行設計規則檢查,包括代碼編寫風格,DFT,命名規則和電路綜合相關規則等檢查。

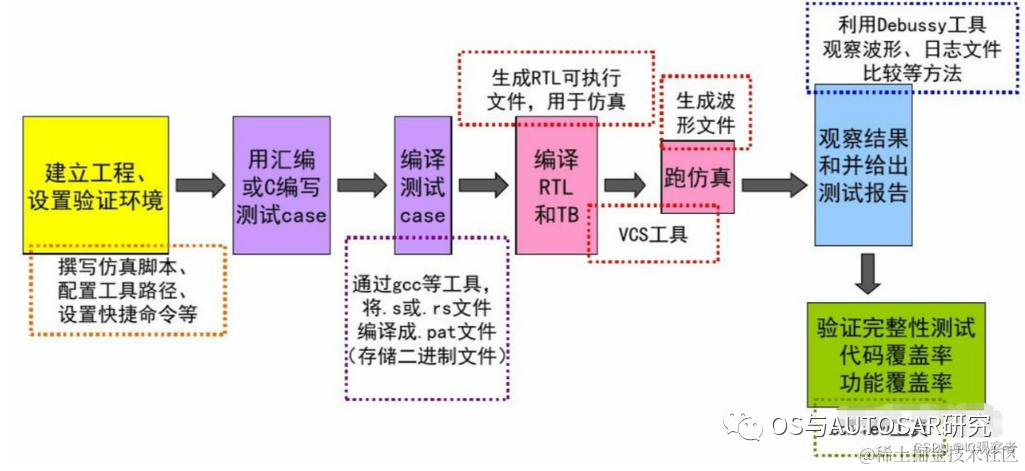

3.2 驗證

驗證是保證芯片功能正確性和完整性最重要的一環。驗證的工作量也是占整個芯片開發周期的50%-70%,相應的,驗證工程師與設計工程師的數量大概在2-3:1。從驗證的層次可以分位:模塊級驗證,子系統級驗證和系統級驗證。從驗證的途徑可以分為:模擬(simulation),仿真和形式驗證(formality check)。

這里又出現了芯片驗證,這里軟件開發人員又來活了,之前在qemu、VDK上模擬的程序現在可以在RTL上模擬了,這里是越來越貼近硬件了。在多平臺驗證雖然很繁瑣,就像驗證完一個玩具系統,然后繼續下一個,好似沒有用,但是每一次都是在進步。 這里需要注意的一點就是在各個驗證平臺下的代碼復用問題,大的模塊差異可以通過編譯時區分,小的差異可以通過運行時讀取標志寄存器來在代碼里面走不同分支或加載不同的配置文件區分,這里需要把握一個度。 一點經驗:多用配置文件例如xml、dts、config文件,不用宏,直接debug版本適應所有驗證平臺,編譯時借助編譯工具腳本自動區分。

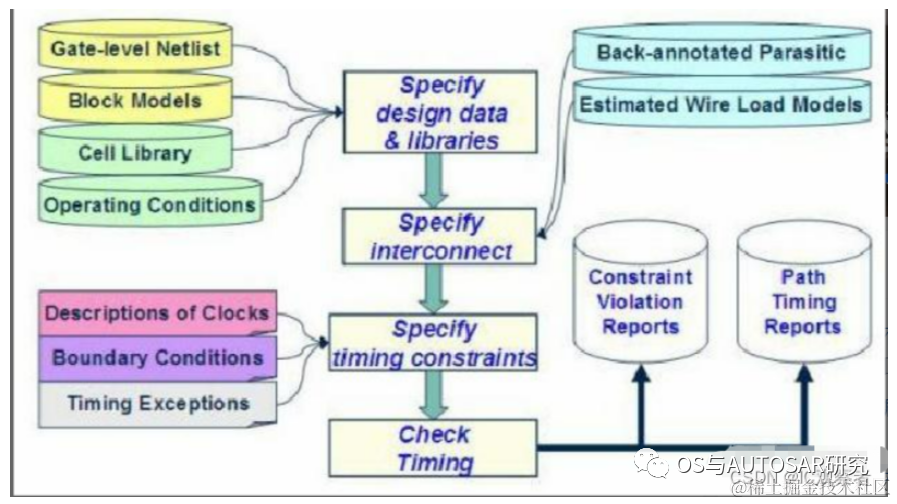

3.3 靜態時序分析(STA)

靜態時序分析是套用特定的時序模型(timing model),針對特定電路,分析其是否違反designer給定的時序限制(timing constraint)。

目前主流的STA工具是synopsys的Prime Time。

? 靜態時序分析的作用:

確定芯片最高工作頻率

通過時序分析可以控制工程的綜合、映射、布局布線等環節,減少延遲,從而盡可能提高工作頻率。

檢查時序約束是否滿足

可以通過時序分析來查看目標模塊是否滿足約束,如不滿足,可以定位到不滿足約束的部分,并給出具體原因,進一步修改程序直至滿足要求。

分析時鐘質量

時鐘存在抖動、偏移、占空比失真等不可避免的缺陷。通過時序分析可以驗證其對目標模塊的影響。

3.4 覆蓋率

覆蓋率作為一種判斷驗證充分性的手段,已成為驗證工作的主導。從目標上,可以把覆蓋率分為兩類:代碼覆蓋率 作用:檢查代碼是否冗余,設計要點是否遍歷完全。檢查對象:RTL代碼 功能覆蓋率 作用:檢查功能是否遍歷 檢查對象:自定義的container 在設計完成時,要進行代碼覆蓋率充分性的sign-off, 對于覆蓋率未達到100%的情況,要給出合理的解釋,保證不影響芯片的工能。

3.5 ASIC綜合

邏輯綜合的結果就是把設計實現的RTL代碼翻譯成門級網表(netlist)的過程。

在做綜合時要設定約束條件,如電路面積、時序要求等目標參數。

工具:synopsys的Design compiler, 綜合后把網表交給后端。

至此我們前端的工作就結束啦!

4. 后端設計

1. 邏輯綜合 2. 形式驗證 3. 物理實現 4. 時鐘樹綜合-CTS 5. 寄生參數提取 6. 版圖物理驗證

4.1 邏輯綜合

同3.5中前端的邏輯綜合

4.2 形式驗證

1)驗證芯片功能的一致性 2)不驗證電路本身的正確性 3)每次電路改變后都需驗證 形式驗證的意義在于保障芯片設計的一致性,一般在邏輯綜合,布局布線完成后必須做。工具:synopsys Formality

4.3 物理實現

物理實現可以分為三個部分:

布局規劃 floor plan

布局 place

布線 route

物理實現可以分為三個部分:

布局規劃 floor plan

布局 place

布線 route

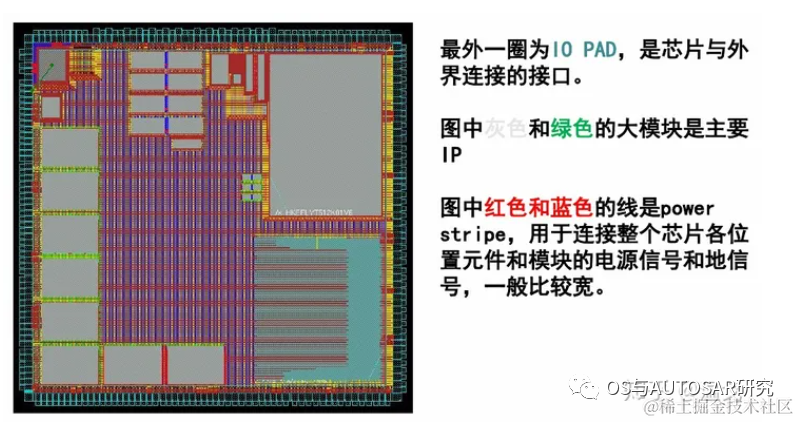

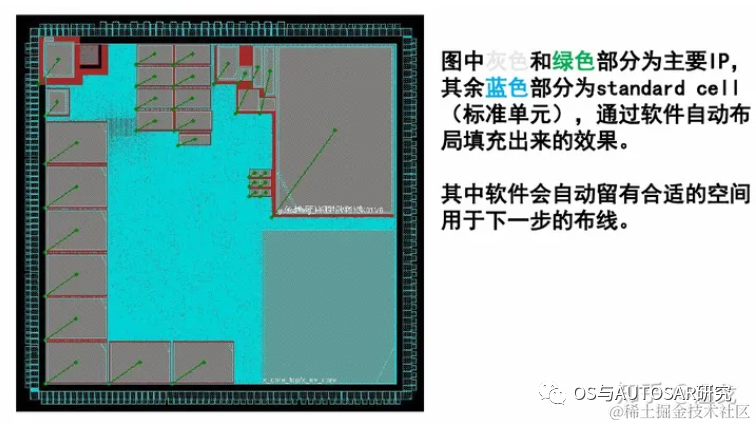

布圖規劃floor plan 布圖規劃是整個后端流程中作重要的一步,但也是彈性最大的一步。因為沒有標準的最佳方案,但又有很多細節需要考量。 布局布線的目標:優化芯片的面積,時序收斂,穩定,方便走線。 工具:IC compiler,Encounter 布圖規劃完成效果圖:

布局 布局即擺放標準單元,I/O pad,宏單元來實現個電路邏輯。 布局目標:利用率越高越好,總線長越短越好,時序越快越好。 但利用率越高,布線就越困難;總線長越長,時序就越慢。因此要做到以上三個參數的最佳平衡。 布局完成效果圖:

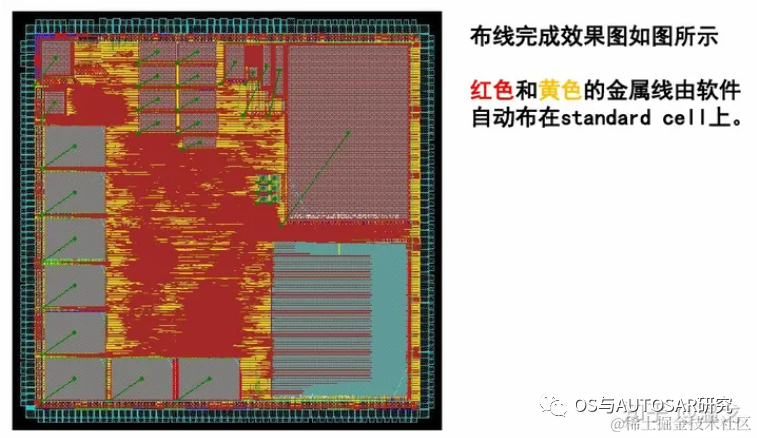

布線 布線是指在滿足工藝規則和布線層數限制、線寬、線間距限制和各線網可靠絕緣的電性能約束條件下,根據電路的連接關系,將各單元和I/O pad用互連線連接起來。

4.4 時鐘樹綜合——CTS

Clock Tree Synthesis,時鐘樹綜合,簡單點說就是時鐘的布線。 由于時鐘信號在數字芯片的全局指揮作用,它的分布應該是對稱式的連到各個寄存器單元,從而使時鐘從同一個時鐘源到達各個寄存器時,時鐘延遲差異最小。這也是為什么時鐘信號需要單獨布線的原因。

4.5 寄生參數提取

由于導線本身存在的電阻,相鄰導線之間的互感,耦合電容在芯片內部會產生信號噪聲,串擾和反射。這些效應會產生信號完整性問題,導致信號電壓波動和變化,如果嚴重就會導致信號失真錯誤。提取寄生參數進行再次的分析驗證,分析信號完整性問題是非常重要的。 工具Synopsys的Star-RCXT

4.6版圖物理驗證

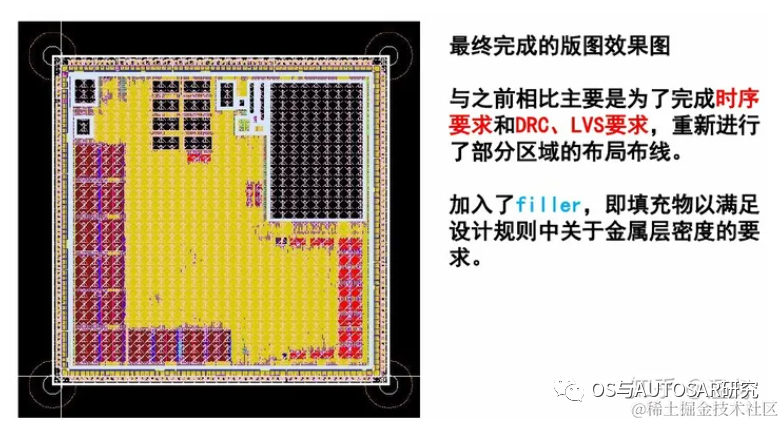

這一環節是對完成布線的物理版圖進行功能和時序上的驗證,大概包含以下方面: LVS(Layout Vs Schematic)驗證:簡單說,就是版圖與邏輯綜合后的門級電路圖的對比驗證; DRC(Design Rule Checking):設計規則檢查,檢查連線間距,連線寬度等是否滿足工藝要求; ERC(Electrical Rule Checking):電氣規則檢查,檢查短路和開路等電氣規則違例; 實際的后端流程還包括電路功耗分析,以及隨著制造工藝不斷進步產生的DFM(可制造性設計)問題等。 物理版圖以GDSII的文件格式交給芯片代工廠(稱為Foundry)在晶圓硅片上做出實際的電路。

最后進行封裝和測試,就得到了我們實際看見的芯片。 ?

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論