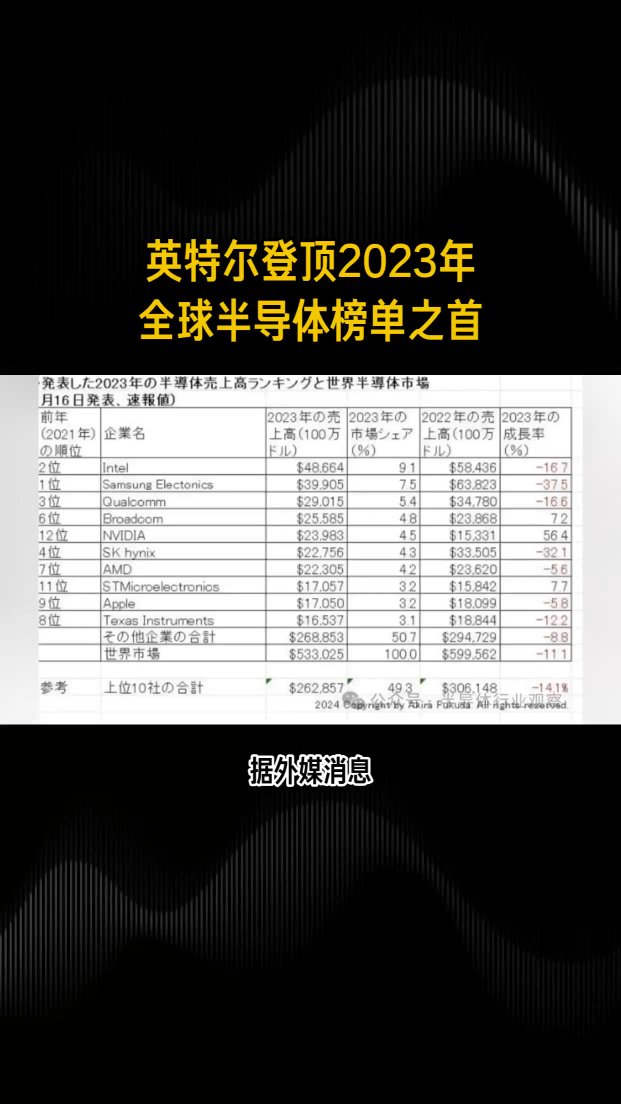

半導(dǎo)體制程工藝上,英特爾要是說(shuō)第二,那沒(méi)人敢說(shuō)第一。晶圓制造這個(gè)圈子,英特爾毫無(wú)疑問(wèn)處于第一流,其他廠(chǎng)商包括IBM,英飛凌,NEC,意法半導(dǎo)體以及東芝等公司,以及目前半導(dǎo)體代工行業(yè)的老大老二老三——臺(tái)積電、 GlobalFoundries、三星,統(tǒng)統(tǒng)都是二流。

說(shuō)這么絕對(duì)可能有人不服,小編舉最近的一個(gè)例子,英特爾僅僅破一次例為美國(guó)芯片制造商Altera代工首個(gè)四核64位ARM Cortex-A53處理器,就引發(fā)了業(yè)界一片驚嘆。

為了讓大家一窺 Intel在半導(dǎo)體制造工藝上的牛逼,筆者選取數(shù)月前參加Intel新品交流會(huì)后,印象深刻的45nm以下HKMG的成型工藝來(lái)做探討。

隨著晶體管尺寸的不斷縮小,HKMG(high-k絕緣層+金屬柵極)技術(shù)幾乎已經(jīng)成為45nm以下級(jí)別制程的必備技術(shù)。不過(guò)在制作HKMG結(jié)構(gòu)晶體管的 工藝方面,業(yè)內(nèi)卻存在兩大各自固執(zhí)己見(jiàn)的不同陣營(yíng),以IBM為代表的前柵極Gate-first工藝流派和以Intel為代表的后柵極Gate-last 工藝流派。更準(zhǔn)確點(diǎn)說(shuō),在步入HKMG時(shí)代之初,只有Intel 和其他所有半導(dǎo)體企業(yè)之別。

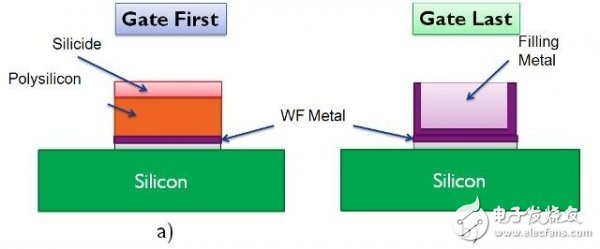

前柵極和后柵極工藝實(shí)現(xiàn)HKMG結(jié)構(gòu),在技術(shù)上有什么差別,請(qǐng)看這段引用:

Gate- last是用于制作金屬柵極結(jié)構(gòu)的一種工藝技術(shù),這種技術(shù)的特點(diǎn)是在對(duì)硅片進(jìn)行漏/源區(qū)離子注入操作以及隨后的高溫退火工步完成之后再形成金屬柵極;與此相對(duì)的是Gate-first工藝,這種工藝的特點(diǎn)是在對(duì)硅片進(jìn)行漏/源區(qū)離子注入操作以及隨后的退火工步完成之前便生成金屬柵極。Gate-last工藝的難點(diǎn)則在于工藝較復(fù)雜,芯片的管芯密度同等條件下要比Gate-first工藝低,需要設(shè)計(jì)方積極配合修改電路設(shè)計(jì)才可以達(dá)到與Gate-first 工藝相同的管芯密度級(jí)別。采用Gate-first工藝制作HKMG的劣勢(shì),是用來(lái)制作high-k絕緣層和制作金屬柵極的材料必須經(jīng)受漏源極退火工步的高溫,會(huì)導(dǎo)致PMOS管Vt門(mén)限電壓的上升,這樣會(huì)影響了管子的性能。

如果對(duì)這段不太理解的童鞋,只需要記住一點(diǎn):后柵極成型HKMG技術(shù)制造的芯片,功耗更低、漏電更少,高頻(即高性能)運(yùn)行狀態(tài)也更穩(wěn)定;但是生產(chǎn)制造技術(shù)復(fù)雜、良品率低、初期很難大規(guī)模量產(chǎn);(在沒(méi)有采用3D晶體管結(jié)構(gòu)前)管芯密度低,對(duì)晶圓的利用不夠經(jīng)濟(jì);真正實(shí)用時(shí),還需要用戶(hù)層面的配合,即客戶(hù)廠(chǎng)商根據(jù)需求配合修改電路設(shè)計(jì)。

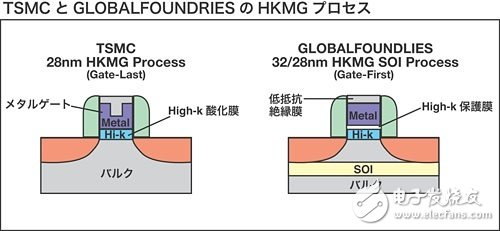

45nm以下必要的HKMG技術(shù)中Gate-first/Gate-last成型工藝各有優(yōu)劣,Intel追求未來(lái)的性能增長(zhǎng)選擇Gate-last,其他廠(chǎng)商則選擇整體難度較小、眼下更容易實(shí)用的Gate-first,經(jīng)過(guò)幾年發(fā)展后,情況如何呢?

先看Gate-first,下面這段話(huà)引用自英特爾中國(guó)技術(shù)發(fā)言人洪力的評(píng)價(jià):

28 納米去年TSMC(臺(tái)積電)剛剛用到所謂后柵極工藝,英特爾從45納米開(kāi)始用后柵工藝,那是4年以前的事。這個(gè)時(shí)候功耗就來(lái)的小,那個(gè)時(shí)候我們出來(lái)包括 IBM那些所有的人出來(lái)說(shuō)英特爾宣布做后柵工藝的時(shí)候,不可能達(dá)到經(jīng)濟(jì)利益上的量產(chǎn),因?yàn)樘y做了,英特爾做出來(lái)了。為什么后柵很重要,當(dāng)處理器運(yùn)算的頻率高的時(shí)候,你的功耗就會(huì)很大,這部分做起來(lái)很不容易。所以你會(huì)看到去年很長(zhǎng)時(shí)間都講到產(chǎn)能不足的問(wèn)題,現(xiàn)在TSMC有了,三星的 28納米還是前柵工藝的。到22納米的時(shí)候我們其實(shí)已經(jīng)開(kāi)始做三維晶體管,這是晶體管的一個(gè)創(chuàng)新,柵極起來(lái)了。那樣的分布方式使得它的性能和功耗、密度都會(huì)有一個(gè)更大的提高,你去看一看TSMC的3D的晶體管是2015年開(kāi)始量產(chǎn),可以看到中間差多遠(yuǎn),三年半的時(shí)間。此28納米和彼22納米不是一回事。還有一些廠(chǎng)商說(shuō)還有14納米更小的,這跟做邏輯的不是一回事,所以英特爾領(lǐng)先是按代來(lái)衡量的,是一代還是兩代。

再看看Gate-last,這是臺(tái)積電研發(fā)部門(mén)高級(jí)副總裁蔣尚義從Gate-first陣營(yíng)轉(zhuǎn)向Gate-last陣營(yíng)時(shí)說(shuō)的話(huà):

和 20年前一樣,我們現(xiàn)在又遇到了如何控制Vt(管子門(mén)限電壓)的難題。如今的Gate-first+HKMG工藝同樣存在很難控制管子Vt電壓的問(wèn)題。盡管廠(chǎng)商可以在管子的上覆層(capping layer)上想辦法對(duì)這種缺陷進(jìn)行補(bǔ)償,不過(guò)這種方案“極其復(fù)雜和困難程度相當(dāng)高”Gate-last工藝當(dāng)然也存在一些局限性。比如這種工藝制出的管子結(jié)構(gòu)很難實(shí)現(xiàn)平整化。不過(guò)如果設(shè)計(jì)方的Layout團(tuán)隊(duì)能夠在電路設(shè)計(jì)方面做出一些改動(dòng),那么就可以克服這個(gè)問(wèn)題,使Gate-last工藝制作出來(lái)的芯片的管芯密度與Gate-first工藝相近。在我們采用后柵極工藝的時(shí)候,有的客戶(hù)一開(kāi)始抱怨連連,曾一度表示如果采用這種新工藝,那么產(chǎn)品的管芯密度很難與Gate-first保持一致,不過(guò)經(jīng)過(guò)我們多次面對(duì)面的商談?dòng)懻摚蛻?hù)們已經(jīng)完全接受了這種新的工藝。我相信目前仍堅(jiān)守Gate-first陣營(yíng)的廠(chǎng)商在22nm制程節(jié)點(diǎn)將被迫轉(zhuǎn)向采用Gate-last工藝。我不是在批評(píng)他們,只是認(rèn)為他們最終會(huì)改變觀(guān)念的。除非他們能找到一種成本低,極具創(chuàng)意的方案來(lái)控制管子的門(mén)限電壓,否則他們必然要轉(zhuǎn)向Gate-last工藝。

這里不得不提的是,據(jù)蔣尚義介紹,20年前,半導(dǎo)體產(chǎn)業(yè)也同樣面臨類(lèi)似的難題,當(dāng)時(shí)的半導(dǎo)體廠(chǎng)商計(jì)劃在NMOS/PMOS管中統(tǒng)一采用N+摻雜的多晶硅材料來(lái)制作柵極,廠(chǎng)商們發(fā)現(xiàn)當(dāng)在PMOS管中采用這種柵極材料之后,管子的性能表現(xiàn)并不好,管子的Vt電壓很難降低到理想的水平。為此,有部分廠(chǎng)商試圖往PMOS管的溝道中摻雜補(bǔ)償性的雜質(zhì)材料,以達(dá)到控制Vt的目的。不過(guò)此舉又帶來(lái)了很多副作用,比如加劇了短溝道效應(yīng)對(duì)管子性能的影響能力。

為何45nm剛開(kāi)始的時(shí)候,只有一家Intel知道使用后柵極,因?yàn)椋簜ゴ蟮钠髽I(yè),特質(zhì)都是相同的——目光長(zhǎng)遠(yuǎn),極富預(yù)見(jiàn)性。Intel 如今的領(lǐng)先優(yōu)勢(shì)有多大,洪力的描述非常清楚地表達(dá)出了目前半導(dǎo)體代工業(yè)老大TSMC和Intel 的差距,這里就不再重復(fù)了。

臺(tái)積電“以史為鑒”,轉(zhuǎn)向后柵極工藝。而目前正在冉冉升起的三星(目前半導(dǎo)體代工市場(chǎng)份額已經(jīng)僅次于臺(tái)積電和GlobalFoundries),更是精明,早在步入HKMG時(shí)代之初,三星雖然加入了前柵極工藝的陣營(yíng),但是據(jù)傳一直在偷偷研發(fā)和嘗試后柵極工藝。(待續(xù),下篇將說(shuō)明目前后柵極成型HKMG工藝芯片的分布情況,并做相關(guān)的分析和對(duì)比)

很多人知道28nm制程比40納米先進(jìn),耗電更低、發(fā)熱更少、集成的晶體管更多。更進(jìn)一步,不少人還知道HKMG(high-k絕緣層+金屬柵極)是實(shí)現(xiàn)更先進(jìn)制程的必備技術(shù)。但了解HKMG的兩種工藝——前柵極/后柵極的人就很少了吧。HKMG的這兩種工藝對(duì)芯片性能/功耗的影響,同樣十分巨大。

很多人知道28nm制程比40納米先進(jìn),耗電更低、發(fā)熱更少、集成的晶體管更多。更進(jìn)一步,不少人還知道HKMG(high-k絕緣層+金屬柵極)是實(shí)現(xiàn)更先進(jìn)制程的必備技術(shù)。但了解HKMG的兩種工藝——前柵極/后柵極的人就很少了吧。HKMG的這兩種工藝對(duì)芯片性能/功耗的影響,同樣十分巨大。

為了讓大家對(duì)芯片制造工藝好壞有一個(gè)全面認(rèn)識(shí),先普及下幾個(gè)重要的概念。

線(xiàn)寬

28nm和40nm指的是芯片上晶體管和晶體管之間導(dǎo)線(xiàn)連線(xiàn)的寬度。半導(dǎo)體業(yè)界習(xí)慣用線(xiàn)寬這個(gè)工藝尺寸來(lái)代表硅芯片生產(chǎn)工藝的水平。線(xiàn)寬越小,晶體管也越小,讓晶體管工作需要的電壓和電流就越低,晶體管開(kāi)關(guān)的速度也就越快,這樣新工藝的晶體管就可以工作在更高的頻率下,隨之而來(lái)的就是芯片性能的提升。簡(jiǎn)而言之就是,線(xiàn)寬越小,芯片更省電的同時(shí),性能還會(huì)提高。

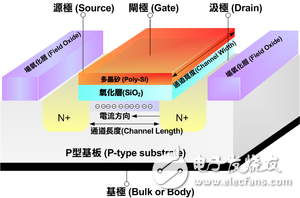

晶體管柵極

我們通過(guò)所說(shuō)的芯片上的晶體管,是指金屬氧化物半導(dǎo)體場(chǎng)效應(yīng)管(簡(jiǎn)稱(chēng):金氧半場(chǎng)效晶體管,MOSFET),有柵極(gate)、漏極(drain)、源極(source)三個(gè)端。

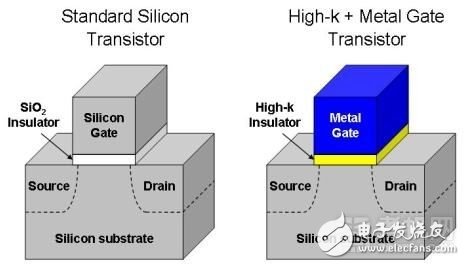

其中縮小柵極面積讓晶體管尺寸變小,是工藝進(jìn)化的關(guān)鍵。HKMG指的就是金屬柵極/高介電常數(shù)絕緣層(High-k)柵結(jié)構(gòu),相對(duì)于傳統(tǒng)的poly/SiON多晶硅氮氧化硅,下面的圖表可以直觀(guān)地展示它們的不同。

阻礙傳統(tǒng)的poly/SiON柵極面積做小的原因,是下方的氧化物絕緣層(主要材料是二氧化硅,不過(guò)有些新的高級(jí)制程已經(jīng)可以使用如氮氧化硅silicon oxynitride, SiON做為氧化層之用)的厚度是不能無(wú)限縮小的。柵極氧化層隨著晶體管尺寸變小而越來(lái)越薄,目前主流的半導(dǎo)體制程中,甚至已經(jīng)做出厚度僅有1.2納米的柵極氧化層,大約等于5個(gè)原子疊在一起的厚度而已。在這種尺度下,所有的物理現(xiàn)象都在量子力學(xué)所規(guī)范的世界內(nèi),例如電子的穿隧效應(yīng)。因?yàn)榇┧硇?yīng),有些電子有機(jī)會(huì)越過(guò)氧化層所形成的位能障壁(potential barrier)而產(chǎn)生漏電流,這也是今日集成電路芯片功耗的來(lái)源之一。為了解決這個(gè)問(wèn)題,有一些介電常數(shù)比二氧化硅更高的物質(zhì)被用在柵極氧化層中。

high- k工藝就是使用高介電常數(shù)的物質(zhì)替代SiO2作為柵介電層。intel采用的HfO2介電常數(shù)為25,相比SiO2的4高了6倍左右,所以同樣電壓同樣電場(chǎng)強(qiáng)度,介電層厚度可以大6倍,這樣就大大減小了柵泄漏。后來(lái),intel在 45nm 啟用了 high-k ,其他企業(yè)則已在或?qū)⒃?32nm/28nm 階段啟用 high-k 技術(shù)。high-k技術(shù)不僅能夠大幅減小柵極的漏電量,還能有效降低柵極電容。這樣晶體管的關(guān)鍵尺寸便能得到進(jìn)一步的縮小,而管子的驅(qū)動(dòng)能力也能得到有效的改善。

簡(jiǎn)而言之,與poly/SiOn相比,使用HKMG柵極,晶體管能做的更小,漏電也更少。目前同制程下,HKMG比poly/SiON耗能低30-35%,所以理論上,32nm的HKMG耗能差不多等同于22.5-24nm的poly/SiON。

前柵極/后柵極

前面我們論證了HKMG相對(duì)于poly/SiON的優(yōu)勢(shì),但很少人知道,即使同樣是HKMG柵極,如果采用不同的制造工藝——前柵極(gate-first)/后柵極(gate-last),芯片表現(xiàn)是不一樣的。

煮機(jī)上一篇文章已經(jīng)說(shuō)過(guò),前柵極工藝制作HKMG,用來(lái)制作high-k絕緣層和制作金屬柵極的材料必須經(jīng)受漏源極退火工步的高溫,會(huì)導(dǎo)致晶體管Vt門(mén)限電壓上升,這樣會(huì)影響管子的性能。具體表現(xiàn),就是當(dāng)處理器運(yùn)算的頻率高的時(shí)候,功耗就會(huì)很大。

所以,在高性能/低功耗方面,使用后柵極工藝HKMG柵極的芯片較好。

好了,我們花了很長(zhǎng)的篇幅給大家講解了HKMG柵極相對(duì)于poly/SiON柵極的優(yōu)勢(shì),以及后柵極工藝HKMG為什么比前柵極工藝HKMG更好,下面將是重頭戲了。

英特爾為什么牛——移動(dòng)芯片制程工藝一覽

前兩篇說(shuō)了一大堆,無(wú)非論證了,除了大家熟悉的xx納米(線(xiàn)寬)越小制程越先進(jìn),評(píng)價(jià)目前半導(dǎo)體制程水平還有兩點(diǎn):Poly/SiON柵極和 HKMG柵極的檔次差距,以及如果同樣是HKMG柵極的情況下,采用前柵極工藝(gate-first)和后柵極工藝(gate-last)對(duì)芯片在實(shí)際應(yīng)用時(shí)的影響。

前兩篇說(shuō)了一大堆,無(wú)非論證了,除了大家熟悉的xx納米(線(xiàn)寬)越小制程越先進(jìn),評(píng)價(jià)目前半導(dǎo)體制程水平還有兩點(diǎn):Poly/SiON柵極和HKMG柵極的檔次差距,以及如果同樣是HKMG柵極的情況下,采用前柵極工藝(gate-first)和后柵極工藝(gate-last)對(duì)芯片在實(shí)際應(yīng)用時(shí)的影響。

這里再總結(jié)一下:

(1)與poly/SiON相比,使用HKMG柵極,晶體管能做的更小,漏電也更少

(2)在高性能/低功耗方面,使用后柵極工藝HKMG柵極的芯片較好

可能大家會(huì)提到FinEFT即3D晶體管,這個(gè)是整個(gè)晶體管層面上的創(chuàng)新(三柵極晶體管),而之前我們討論的、無(wú)論是關(guān)于HKMG柵極和poly/SiON 柵極,還是gate-first/gate-last工藝,創(chuàng)新僅僅局限在傳統(tǒng)晶體管的柵極上。考慮到目前只有Intel 一家實(shí)現(xiàn)了3D晶體管的大規(guī)模量產(chǎn)和實(shí)用,其他廠(chǎng)商完全與其不在一個(gè)檔次上,而此文的主要目的是比較臺(tái)積電、Globalfoundries、三星目前半導(dǎo)體制程工藝的優(yōu)劣,所以就不再深究FinEFT的影響了。

臺(tái)積電28nm制程工藝分布情況

臺(tái)積電目前四種適應(yīng)不同市場(chǎng)定位設(shè)備的28nm工藝,其中HP、HPL、HPM皆采用了HKMG柵極和后柵極工藝,而LP采用了poly/SiON柵極和前柵極工藝。所以,綜合來(lái)看,HPM最好,LP最差。

參照上圖,性能方面HPM>HP>HPL>LP,漏電HPL<HPM<LP<HP。

實(shí)用層面,高通MSM8960 Snapdragon S4使用的就是28nm LP工藝,而紅米吹噓的聯(lián)發(fā)科四核芯片MT6589T也是臺(tái)積電最差的28nm LP工藝。

HPM的實(shí)用典范則是高通的驍龍800。最近MTK(聯(lián)發(fā)科)發(fā)展勢(shì)頭驚人,已經(jīng)曝光的下一代四核芯片MT6588和八核芯片MT6592將采用臺(tái)積電28nm級(jí)別綜合最好的HPM工藝。

英偉達(dá)A15核心的Tegra 4使用的是漏電最少的HPL,看來(lái)為了控制A15的功耗,英偉達(dá)也只有在制程工藝上彌補(bǔ)了。

GlobalFoundries的28/32nm 制程工藝情況

Globalfoundries四種28nm制程工藝和單獨(dú)列出的32nm制程,皆是gate-first即前柵極工藝,可見(jiàn)其目前的制造水準(zhǔn)。

這里不得不八卦一下,Globalfoundries最初成立是依靠從AMD分離出來(lái)的晶圓制造廠(chǎng),后來(lái)獲得中東超富產(chǎn)油小國(guó)的Advanced Technology Investment Company(ATIC)公司投資入股,到最后ATIC全資入股,所以Globalfoundries燒錢(qián)起來(lái)是毫不吝嗇的。中東富豪投資這一行,花錢(qián)起來(lái)讓人側(cè)目,但似乎并不怎么上進(jìn)。

如上表,32nm級(jí)別的SHP和28nm級(jí)別的HPP、HP、SLP都是HKMG柵極,而G(unoffical)則是傳統(tǒng)的Poly/SiON。客戶(hù)一欄里我們也可以發(fā)現(xiàn),Globalfoundries主要客戶(hù)還是AMD。

另外,據(jù)說(shuō)Globalfoundires依靠?jī)r(jià)格優(yōu)勢(shì)以及臺(tái)積電產(chǎn)能不足,今年第三季度從臺(tái)積電那里分流了點(diǎn)MTK(聯(lián)發(fā)科)和高通的28nm級(jí)芯片的訂單,具體用在哪些產(chǎn)品上,筆者并不清楚,但可以肯定的是,這些芯片的品質(zhì)非常一般。

三星也傳出把Globalfoundries當(dāng)做是“后備工廠(chǎng)”,因?yàn)槟壳叭堑木A工廠(chǎng)已無(wú)法同時(shí)滿(mǎn)足自家芯片和蘋(píng)果A系列移動(dòng)芯片的需求,就把一部分訂單轉(zhuǎn)包給了Globalfoundries。蘋(píng)果整天吵著要“脫離”三星,事實(shí)上,三星根本無(wú)所謂,你脫離了反倒釋放了產(chǎn)能,可以給自己的產(chǎn)品集中供貨。

三星 28/32nm制程工藝情況

三星目前的28nm級(jí)別制程使用的是HKMG柵極,但是是前柵極工藝。自家的Exyons 5系列芯片和蘋(píng)果的A7,都是采用的此種工藝。

但是千萬(wàn)別以此小看了三星。早在業(yè)界進(jìn)入HKMG時(shí)代之初,三星聲明支持前柵極工藝卻秘密研發(fā)后柵極工藝,下一代無(wú)20nm/14nm全面使用后柵極工藝應(yīng)該是板上釘釘了。

還有更驚人的,三星的14nm級(jí)FinEFT即3D晶體管早在2012年年底就已經(jīng)流片成功,相傳明年旗艦Galaxy s5上的Exyons 6系列芯片就使用這種工藝制造,而量產(chǎn)時(shí)間點(diǎn),就在明年2014年年初!相比之下,目前晶圓代工市場(chǎng)份額最大的臺(tái)積電,其產(chǎn)品路線(xiàn)圖顯示2015年才會(huì)量產(chǎn)3D晶體管芯片。而Globalfoundries,在三星已經(jīng)流片14nm FinEFT晶圓成功的前幾個(gè)月,才剛剛宣布14nm 3D晶體管的研發(fā)計(jì)劃。

如果傳言屬實(shí),三星進(jìn)步神速不但會(huì)在技術(shù)上最接近Intel,最先進(jìn)制程的大規(guī)模量產(chǎn)實(shí)用層面,則一舉超過(guò)包括 Intel、臺(tái)積電和Globalfoundries。未來(lái)一年將是晶圓代工市場(chǎng)格局發(fā)生關(guān)鍵性轉(zhuǎn)折的一年,三星無(wú)論在技術(shù)上、還是率先大規(guī)模實(shí)用最先進(jìn)制程工藝上,很可能一鳴驚人,就此逆轉(zhuǎn)老3的地位。

至于蘋(píng)果要脫離三星,圈內(nèi)稍微有點(diǎn)常識(shí)的都知道,這對(duì)蘋(píng)果來(lái)說(shuō)是得不償失,只能在媒體上吹風(fēng)而已。把訂單交給臺(tái)積電,臺(tái)積電不愿承擔(dān)風(fēng)險(xiǎn),為臺(tái)積電增加投資和補(bǔ)貼意味著抬高成本;而把訂單交給GlobalFoundries,GF如此懶散不求上進(jìn)的“土豪”,無(wú)論是大規(guī)模量產(chǎn)供貨上,還是產(chǎn)品技術(shù)品質(zhì),都競(jìng)爭(zhēng)不過(guò)勤奮的亞洲人。Intel ?蘋(píng)果得看別人的心情。

總結(jié)

Intel在后PC時(shí)代還是保持著Tick-Tock的節(jié)奏,這幾年在制程級(jí)別的代級(jí)領(lǐng)先和更先進(jìn)的工藝技術(shù),還是前幾年積累的。競(jìng)爭(zhēng)對(duì)手與其差距正在慢慢縮小。其中,三星尤其值得警惕。

晶圓制造領(lǐng)域Intel 之外的其他廠(chǎng)商,臺(tái)積電的表現(xiàn)算是穩(wěn)扎穩(wěn)打,但基于贏(yíng)利/商業(yè)利益的考量,技術(shù)演進(jìn)的速度還是過(guò)于保守了。靠錢(qián)堆起來(lái)的Globalfoundries 開(kāi)始有了起色,正在慢慢走向成熟,但土豪的氣質(zhì)依然未變,靠腳底下石油不愁吃不愁穿的阿拉伯人,最欠缺的其實(shí)是亞洲人的上進(jìn)心/危機(jī)感。

三星的話(huà),不多說(shuō)了,看不久的將來(lái)會(huì)發(fā)生什么吧。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論