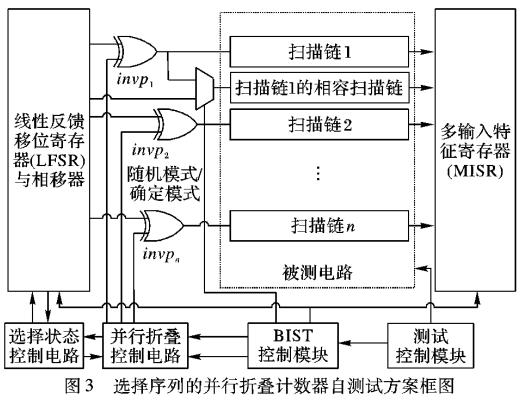

一種選擇序列的并行折疊計數器

大小:0.81 MB 人氣: 2018-02-04 需要積分:2

隨著納米工藝的發展和芯片尺寸的增大,芯片的集成度和設計復雜度越來越高,芯片測試的目標故障、測試數據量測試應用時間也顯著增長。另一方面,昂貴的自動測試設備( Automatic Test Equipment,ATE)的通道數和帶寬極其有限。因此,研究如何在保障芯片測試故障覆蓋率的前提下,壓縮測試數據,減少測試應用時間,降低測試成本,具有十分重要的意義。

為了減少測試應用時間并保證高測試數據壓縮率,提出一種選擇序列的并行折疊計數器。在分析并行折疊計算理論的基礎上,通過記錄表示折疊索引的組序號和組內序號生成選擇狀態的測試序列,避免了無用和冗余的測試序列的生成。ISCAS標準電路的實驗結果表明,該方案的平均測試數據壓縮率為94. 48%,平均測試應用時間為類似方案的15. 31%。

非常好我支持^.^

(0) 0%

不好我反對

(0) 0%

下載地址

一種選擇序列的并行折疊計數器下載

相關電子資料下載

- 10 MHz OCXO,帶40 MHz頻率計數器 97

- STM32G4系列芯片定時器的延時輸出問題 532

- 風速繼電器的應用領域 1034

- 簡儀計數器/定時器模塊滿足嚴格的工業標準和安全要求 325

- TS-RadiMation測試軟件如何在序列測試中發揮作用? 40

- PLC計數器的工作原理與功能 567

- 三菱PLC高速計數器的基本特點 339

- 三菱PLC計數器和數據寄存器介紹 625

- 了解反饋振蕩器,看這篇文章就夠了 122

- 提升效率的利器——10進制計數器的使用指南 174