與4G技術相比,新一代5G無線通信技術有望將吞吐量提高兩個數量級的同時將延時降低兩個數量級。5G標準的到來,為高級手機和融合固定及移動網絡應用定義了全新的算法和協議。

盡管我們研究5G已有一段時間,但新無線電(NR)的5G標準到2018年完成融合,到2020年才開始5G網絡部署,因此芯片的研發周期非常短。在過去兩年中,芯片制造商一直在競相研發5G芯片,以期在5G技術首次亮相時便能夠及時投放市場。所以,芯片制造商沒有坐等標準成熟,而是選擇在模塊中加入更多軟件可編程解決方案。這些解決方案傳統上會作為固定功能硬件,在物理層和數字前端等環節得以實現。

同時,5G令人生畏的吞吐量和延時要求促使各級通信協議全面加速。例如,第2層處理傳統上是在標準處理器中完成,但其實并無法達到實際所需的性能標準。

如何解決?

ASIP方案

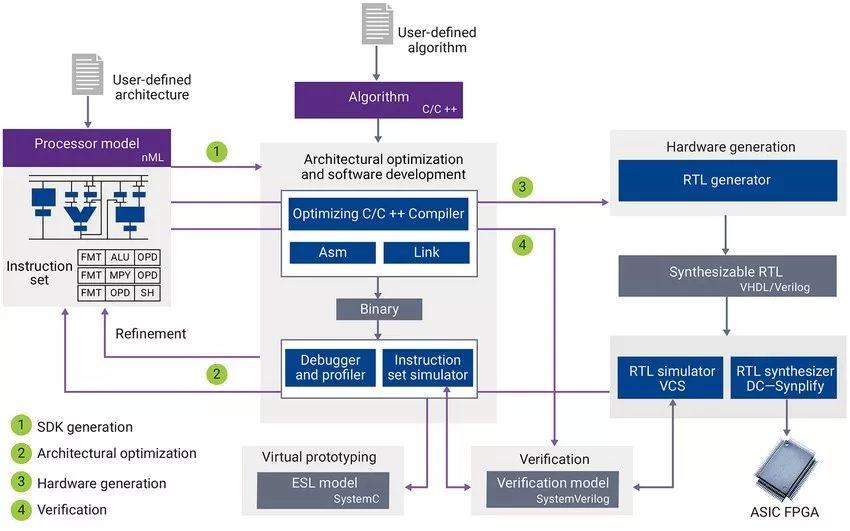

專用指令集處理器(ASIP)成功彌合了高度優化的固定功能硬件實現與標準處理器 IP 之間的差距(圖一)。對于絕大部分5G芯片而言,在實現架構中的模塊時,如果需要特定硬件性能并且還要求處理器 IP 具備可編程性和靈活性,那么ASIP將是最優的選擇 。

▲ASIP 彌合了固定功能 RTL 設計與通用處理器 IP 之間的差距(圖一)

研發團隊可以根據不同要求來開發ASIP去執行一個特定的系統模塊,例如前向糾錯;或者用于整個系統,例如用于第1層基帶處理的矢量DSP。在第一種情況下,它的可編程性使得模塊能夠容納算法變量(例如,將其編程用于LDPC、維特比或極化碼)。每種情況下,設計人員都可以進行權衡,以平衡性能、靈活性、能耗、可重用性(或通用性)和設計時間。

ASIP Designer

ASIP Designer采用了涉及多個領域工作的ASIP方案,包括定義合適的ASIP架構、實現處理器硬件和相應的軟件開發工具包(SDK)、可幫助自動創建ASIP及其相關的SDK(圖二)。

▲ASIP Designer 工具流程(圖二)

處理器建模

ASIP使用nML描述,nML是一種條理清晰的體系結構描述語言,能夠高效而簡潔地描述與編程手冊相同抽象級別的處理器體系結構。

該語言用于定義設計的結構特征(存儲器、寄存器、功能單元、連接等)和指令集體系結構。nML還使用戶能夠描述數據路徑、 I/O 接口的周期精確和位精確行為。

SDK生成

ASIP Designer使軟件開發人員能夠直接在候選架構上開發和分析C/C ++ 軟件,因為ASIP Designer提供了一個功能齊全的SDK(圖二中的第 1 步),可以自動適應nML中描述的已定義處理器架構。SDK包含優化的C/C ++ 編譯器、匯編器/反匯編器、鏈接器、周期精確和指令精確的指令集仿真器,以及圖形調試器。

編譯器獨具專利型編譯器可重定向性,可適應所有候選架構的細節。GNU或 LLVM等經典編譯器框架,需要去開發架構專用的編譯器后端,并且還必須對每個候選架構重復此過程。編譯器的即時可用性支持快速迭代,也支持用于架構探索的“循環內編譯器”方法(圖二中的第2步)。

循環內編譯器方法意味著軟件工程師可以向ASIP設計工程師提前反饋,處理器的動態性能可以即時分析和優化。

硬件的生成和驗證

設計人員一旦確定建模的ASIP滿足所選算法的預期性能,就可以使用ASIPDesigner生成可綜合的 RTL,從而使用標準流程執行實現級細化和詳細驗證(圖二中的第3步),然后使用新思科技Design Compiler生成門級描述,并預測電路的功耗要求和面積,或使用布局布線工具來辨別布線擁塞的風險。

采用這種“循環內綜合”方法能夠作出有根據的決策,避免在設計后期出現意外情況。如果設計人員在實現過程中遇到問題,則可以回到nML描述進行調整。nML中采用單源條目,所以SDK和RTL會保持同步。

5G芯片專用ASIP示例

在大多數即將推出的5G芯片中都部署了ASIP,并且在基站和移動終端中均有部署,主要應用領域包括需要大規模信號處理的領域,例如第1層中的數字前端和基帶處理,以及第2層控制功能的加速。

如圖 1 所示,ASIP可以滿足各種架構的需求,并且ASIP Designer用戶可以進行任何級別的架構設計。5G專用ASIP包括具有專用數據類型、存儲器和寄存器配置以及指令集的寬矢量DSP,其性能優于標準DSP。以下是兩個可供 ASIP Designer授權方使用的示例設計。

FFT/DFT 加速

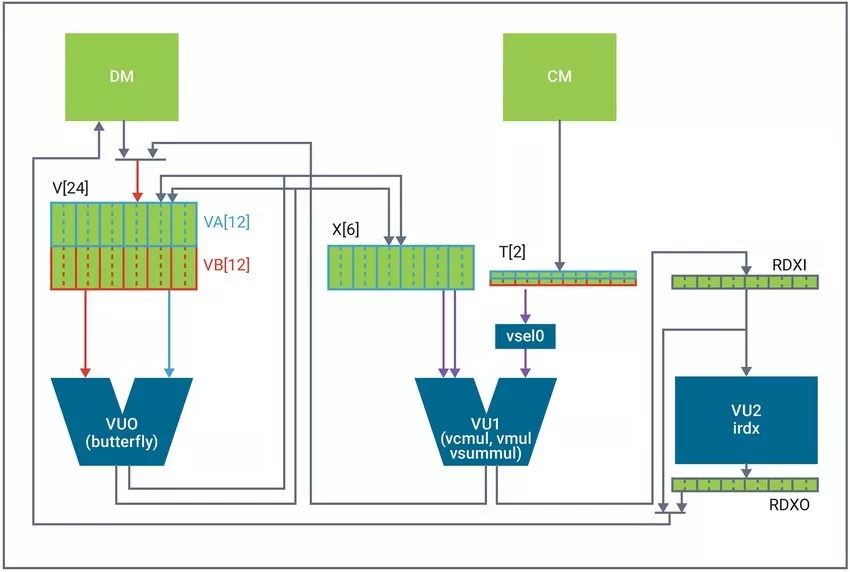

PrimeCore是一款針對FFT/DFT操作進行了調整的處理器。它支持從8到2048的所有2次冪大小的FFT,以及從6到1536的所有質因數分解大小的 DFT。

▲PrimeCore 架構(圖三)

PrimeCore是一個256位8通道SIMD架構,具有三個矢量數據路徑單元,處理復雜的定點操作數。VU0執行專用蝶形運算,從定制的寄存器文件中讀取數據;VU1執行向量乘法和加法;VU2專門執行基數6蝶形計算。它具有兩個矢量存儲器,其中一個存儲器分配給VU1使用。加載及加載-存儲操作與向量操作并行發生,從而產生多達5路的指令級并行。架構雖然經過高度專業化,但通過ASIP Designer生成的編譯器充分利用并行,完全可以進行C編程。一些數據點說明了性能:256-FFT需要172個周期,2048-FFT需要1189個周期,1296-DFT需要798個周期。700MHz時鐘的綜合(16nm FF)結果是35萬門。

MMSE 加速

第二示例處理器可實現最小均方誤差(MMSE)均衡器算法,用于基站中的5GNR信道均衡。該算法在矩陣元素是復雜浮點數的矩陣運算中占有主導地位。最終形成一個非常寬(4096位)的SIMD架構,具有4路指令級并行。該架構特別關注高效存儲器概念。由于成本原因,使用了單端口存儲器,進行一次復雜的乘法累加運算需要訪問存儲器兩次,并且是流水線運算。為處理特定于該算法的三角矩陣,實現了許多專門的索引尋址模式。同樣,這種架構完全可以進行C編程,能夠利用ASIP Designer的編譯器處理流水線運算。基于MMSE算法的嵌套循環結構,編譯器就具備為內循環和外循環執行軟件流水運算的獨特能力,從而顯著減少周期數。

結語

向5G的轉變促使系統架構師在設計中尋找針對各個模塊的實現方法,突破在商用處理器IP上運行軟件或人工、定制的固定RTL之間二選一的局面。

ASIP是一種成熟的實現方案,具備高度優化的RTL和軟件可編程性等優勢。許多公司借助ASIP Designer來設計ASIP,降低風險的同時加快了設計進度,而其獨特的循環內編譯器和循環內綜合方法能夠高效地指導架構的選擇。此外,ASIP Designer自動提供質量優異、功能齊全的專業SDK,無需聘請編譯器、仿真器或調試GUI專家,即可以快速支持軟件開發團隊。

因此,依賴ASIP Designer的設計團隊現在可以考慮:

●用ASIP取代固定功能硬件實現,將設計和驗證過程中復雜、費神且容易出錯的過程轉移到軟件中,這樣就可以在軟件中解決出現的問題,從而加快產品上市時間。

●設計自己的專用DSP和算法特定加速器,例如5G物理層和數字前端處理,以及第2層加速所需的加速器。

幾十年來,不同細分市場的領先公司都采用了ASIP方法,而現在大多數開發5G芯片的頂級公司都把ASIP Designer作為自動化設計流程的首選工具。

-

4G技術

+關注

關注

0文章

21瀏覽量

8572 -

5G

+關注

關注

1356文章

48506瀏覽量

566027

原文標題:你需要這款專用處理器來應對5G時代

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

與4G技術相比,新一代5G技術到來為高級手機融合固定及移動網絡應用

與4G技術相比,新一代5G技術到來為高級手機融合固定及移動網絡應用

評論