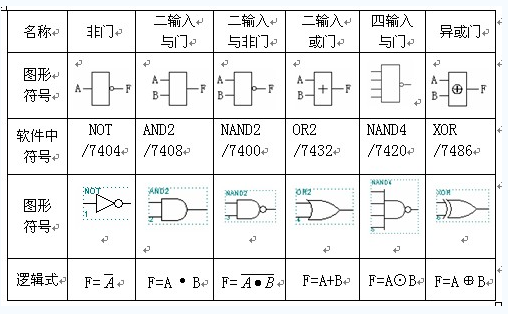

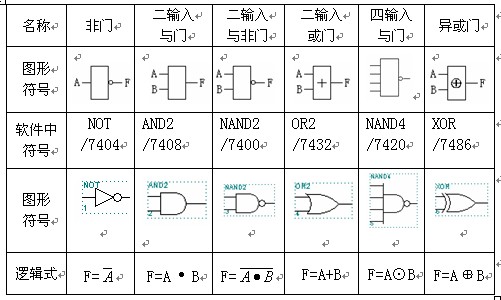

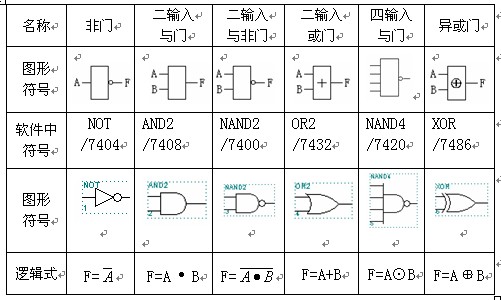

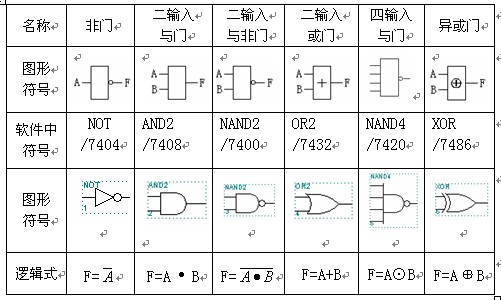

上表包括與門,或門,非門,同或門,異或門,還有這些門電路的邏輯表達式,

1.與邏輯

(1)與邏輯:當(dāng)決定某一事件的所有條件都具備時,該事件才會發(fā)生。

(2)真值表:符號0和1分別表示低電平和高電平,將輸入變量可能的取值組合狀態(tài)及其對應(yīng)的輸出狀態(tài)列成的表格。

表11.2與門真值表

| A | B | Y |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

邏輯門

+關(guān)注

關(guān)注

1文章

142瀏覽量

24127 -

門電路

+關(guān)注

關(guān)注

7文章

199瀏覽量

40260 -

電路符號

+關(guān)注

關(guān)注

3文章

42瀏覽量

12737

發(fā)布評論請先 登錄

相關(guān)推薦

基本邏輯門電路原理

VL≈+5V。 用真值表將所有情況羅列如下:ABCL00001111001100110101010101111111二、非門電路——BJT反相器 上圖表示一基本反相器電路及其邏輯

發(fā)表于 04-06 23:59

與門電路圖

這個因該是與門電路圖吧 E12 = 12V E5 =5V E3 = 3V但為什么不能實現(xiàn)與門邏輯,不管輸入的電壓是 E12, 還是 E3最多只能用 E3 實現(xiàn)或門邏輯,鉗制電壓到3V

發(fā)表于 07-12 18:25

關(guān)于多位輸入真值表的問題

在復(fù)雜的數(shù)字電路中,用真值表的方法化簡邏輯表達式很復(fù)雜,很麻煩,請問諸位高手有沒有簡單的方法化簡邏輯表達式啊?小弟在這里不勝感激

發(fā)表于 07-11 15:20

勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載24:表面現(xiàn)象揭秘——邏輯關(guān)系

符號和真值表圖3.9 或非門符號和真值表圖3.10 異或門符

發(fā)表于 11-20 21:26

門電路的計算方式 門電路工作原理真值計算

?¤B = A ∩ B 其真值表為表 1-1。2.“或”門當(dāng)兩個輸入端 A、 B 中, 只要至少有一個輸入端為“1”時, 輸出 端 C 就為“1” , 具有這種邏輯關(guān)系的電路叫做“或

發(fā)表于 12-25 17:04

與門真值表和與非門真值表的區(qū)別

與門真值表和與非門真值表的區(qū)別,與門真值表:有0出0,全1出1。與非門真值表:有0出1,全1出0

發(fā)表于 01-30 15:37

?12.2w次閱讀

邏輯門電路符號圖及與門真值表的資料概述

邏輯門電路符號圖及與門真值表的資料概述

評論