參加這個研討會可以通過物理設(shè)計(PDR)減少PCB設(shè)計的重用。我們將研究pdr的各種用途,并展示使用經(jīng)驗證的電路以減少設(shè)計時間的積極作用,并強調(diào)pads優(yōu)于競爭對手的關(guān)鍵原因。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

pcb

+關(guān)注

關(guān)注

4326文章

23161瀏覽量

399976 -

設(shè)計

+關(guān)注

關(guān)注

4文章

818瀏覽量

69952 -

PADS

+關(guān)注

關(guān)注

80文章

808瀏覽量

107952

發(fā)布評論請先 登錄

相關(guān)推薦

電子工程師的PCB設(shè)計經(jīng)驗

本文分享了電子工程師在PCB設(shè)計方面的經(jīng)驗,包括PCB布局、布線、電磁兼容性優(yōu)化等內(nèi)容,旨在幫助初學(xué)者掌握PCB設(shè)計的關(guān)鍵技術(shù)。

高速PCB設(shè)計EMI防控手冊:九大關(guān)鍵步驟詳解

的關(guān)注。據(jù)統(tǒng)計,幾乎60%的EMI問題都可以通過優(yōu)化高速PCB設(shè)計來解決。本文將詳細介紹高速PCB設(shè)計解決EMI問題的九大規(guī)則,幫助工程師們在設(shè)計中有效減少EMI的產(chǎn)生。 高速

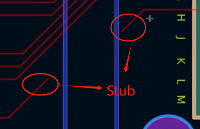

PCB設(shè)計中的Stub對信號傳輸?shù)挠绊?/a>

PCB設(shè)計中應(yīng)盡量減少Stub的存在,或者在無法完全避免Stub的情況下,通過優(yōu)化Stub的長度和幾何形狀來降低它們對信號的影響。

HDMI模塊的PCB設(shè)計

在前面各類設(shè)計的理論講解、設(shè)計實操講解、以及軟件操作的講解的過后,粉絲后臺反饋想結(jié)合前面三種類型進行整體學(xué)習(xí)—模塊設(shè)計,本期推出第一章HDMI模塊的PCB設(shè)計,后續(xù)會繼續(xù)更新各類模塊的PCB設(shè)計教學(xué),以及PCB設(shè)計理論、設(shè)計技巧

高速PCB設(shè)計指南

如今,可以認為大多數(shù)PCB存在某種類型的信號完整性問題的風(fēng)險,這種問題通常與高速數(shù)字設(shè)計相關(guān)。高速PCB設(shè)計和布局專注于創(chuàng)建不易受信號完整性、電源完整性和EMI/EMC問題影響的電路板設(shè)計。雖然沒有

專業(yè)PCB設(shè)計,高速PCB設(shè)計,PCB設(shè)計外包, PCB Layout,PCB Design,PCB畫板公司,PCB設(shè)計公司,迅安通科技公司介紹

專業(yè)PCB設(shè)計,高速PCB設(shè)計,PCB設(shè)計外包, PCB Layout,PCB Design,PCB

發(fā)表于 10-13 15:48

pcb設(shè)計中如何設(shè)置坐標(biāo)原點

在PCB設(shè)計中,坐標(biāo)原點是一個非常重要的概念,它決定了PCB布局的起始位置和方向。 一、坐標(biāo)原點的定義 坐標(biāo)原點的概念 在PCB設(shè)計中,坐標(biāo)原點是一個參考點,用于確定PCB布局的起始位

PCB設(shè)計與PCB制板的緊密關(guān)系

一站式PCBA智造廠家今天為大家講講PCB設(shè)計與PCB制板有什么關(guān)系?PCB設(shè)計與PCB制板的關(guān)系。PCB設(shè)計和制板是

電路仿真和PCB設(shè)計軟件

關(guān)鍵要點電路仿真軟件和PCB設(shè)計軟件在PCB設(shè)計過程中發(fā)揮著互補作用,為工程師提供設(shè)計、仿真、驗證和優(yōu)化電子電路的工具。有效的仿真分析有助于減少開發(fā)所需的設(shè)計、制造和測試迭代次數(shù),確保電路設(shè)計在板

PCB設(shè)計基本原則總結(jié),工程師必看

一站式PCBA智造廠家今天為大家講講pcb設(shè)計安全規(guī)則有哪些要求?PCB工藝規(guī)范及PCB設(shè)計安規(guī)原則。在PCB設(shè)計中,遵循安規(guī)(安全規(guī)范)原則是確保電子產(chǎn)品安全性和合規(guī)性的關(guān)鍵。接下來

PCB設(shè)計中的常見問題有哪些?

一站式PCBA智造廠家今天為大家講講PCB設(shè)計中的常見問題有哪些?PCB設(shè)計布局時容易出現(xiàn)的五大常見問題。在電子產(chǎn)品的開發(fā)過程中,PCB(Printed Circuit Board,印刷電路

pcb設(shè)計

cadence原理圖、Allegro PCB設(shè)計。Aundefined

1.根據(jù)客戶要求代畫原理圖和PCB。

2.原理圖和PCB的修改。

3.單板、雙層板、多層板均可。

支持軟件: cadence

發(fā)表于 05-09 01:38

這幾招教你解決PCB設(shè)計中的電磁干擾(EMI)問題

作為電子設(shè)計中重要組成部分,在PCB設(shè)計中出現(xiàn)電磁問題時如何解決呢?本文將從多方面細節(jié)探討問題要點,可以采取以下解決辦法來降低或消除電磁干擾(EMI): 1.合理的PCB設(shè)計: 盡量采用層板設(shè)計,以

發(fā)表于 05-08 14:39

?3216次閱讀

多層pcb設(shè)計如何過孔的原理

一站式PCBA智造廠家今天為大家講講如何實現(xiàn)多層PCB的過孔?多層pcb設(shè)計過孔的方法。在現(xiàn)代電子行業(yè)中,多層PCB設(shè)計已經(jīng)成為常見且重要的技術(shù)。多層PCB不僅可以提供更高的電路密度,

DC電源模塊的 PCB設(shè)計和布局指南

合適的PCB尺寸和層數(shù):根據(jù)電源模塊的尺寸和功能需求,選擇合適的PCB尺寸和層數(shù)。注意保持足夠的空間來布置元件和散熱器。 DC電源模塊的 PCB設(shè)計和布局指南 2. 地平面:在PCB的

如何通過物理設(shè)計減少PCB設(shè)計的重用

如何通過物理設(shè)計減少PCB設(shè)計的重用

評論