摩爾定律是否失效了?近年來,這一討論不絕于耳。

隨著芯片工藝技術(shù)不斷演進(jìn),芯片設(shè)計和制造成本都在呈指數(shù)級增加,去年開始有兩家大型芯片制造商先后放棄先進(jìn)工藝研發(fā),同時,先進(jìn)工藝每一代至少較上一代增加30%~50%的設(shè)計成本。

“技術(shù)會繼續(xù)發(fā)展,芯片集成度會繼續(xù)增加,但是像過去那樣提高性能、降低功耗而不增加成本已經(jīng)不存在了。”近日,在接受第一財經(jīng)記者專訪時,賽靈思中央工程部芯片技術(shù)副總裁吳欣告訴記者,除了繼續(xù)通過晶體管微縮來提高密度之外,異構(gòu)集成(Heterogeneous Integration,HI)也被認(rèn)為是增強功能及降低成本的可行方法,是延續(xù)摩爾定律的新路徑。

研發(fā)成本越來越高

芯片行業(yè)是典型的人才密集和資金密集型高風(fēng)險產(chǎn)業(yè),如果沒有大量用戶攤薄費用,芯片成本將直線上升。華為曾向媒體透露7nm的麒麟980研發(fā)費用遠(yuǎn)超業(yè)界預(yù)估的5億美元,紫光展銳的一名工作人員則對記者表示,(5G Modem)研發(fā)費用在上億美元,光流片就特別費錢,還有團(tuán)隊的持續(xù)投入,累計參與項目的工程師有上千人。

一方面,制造成本不斷攀升。吳欣指出,由于使用多次曝光(multi-patterning),從20nm開始,芯片制造成本便上升很快。“本來一次曝光,現(xiàn)在兩次:本來一個機(jī)臺一天做4000片wafer(晶圓),現(xiàn)在兩次曝光只能做2000片了。一片晶圓從頭到尾大概需要幾十步的光刻過程,假如光刻占設(shè)備成本的一半,有一半都需要兩次曝光,成本就增加了25%。”

作為芯片制造業(yè)中最核心的設(shè)備,光刻機(jī)也越來越昂貴。“整個業(yè)界花了二三十年的時間把EUV(極紫外光)做出來,今后幾代光刻都會使用EUV。一臺EUV光刻機(jī)就可能需要2億美金。臺積電、英特爾的新工藝生產(chǎn)線都需要十幾臺這樣的設(shè)備。”吳欣告訴記者。

越來越高的費用也讓晶圓代工廠望而卻步。格芯(GlobalFoundries)去年8月正式對外宣布放棄7nm和更先進(jìn)制程的研發(fā),并調(diào)整相應(yīng)研發(fā)團(tuán)隊來支持強化的產(chǎn)品組合方案。此前,臺聯(lián)電也宣布放棄12nm先進(jìn)制程的投資。

據(jù)預(yù)測,未來5年有能力投入先進(jìn)制程的晶圓代工廠只有臺積電、三星和英特爾,在激烈競爭之下,一定會讓定價壓力會一路延燒。

另一方面,設(shè)計成本也不斷上漲,每一代至少增加30~50%的設(shè)計成本,主要是“人頭費”。吳欣表示,對于芯片設(shè)計而言,此前迭代無需考慮新的工藝問題,“只需了解65nm比90nm小多少,可以直接把90nm上的設(shè)計拿到65nm工藝上,重新設(shè)計一下馬上就能做,整個過程半年、一年就完成了。但現(xiàn)在7nm和16nm有很多不一樣的地方,不能把16nm的設(shè)計直接放到7nm上,從架構(gòu)到設(shè)計到后端都要做很多改變。”

由于芯片設(shè)計越來越復(fù)雜,設(shè)計的周期和人數(shù)都要增加。“過去設(shè)計一年現(xiàn)在需要兩年;過去1000人一年,現(xiàn)在2000人兩年,變成四倍了。”對于絕大多數(shù)芯片制作廠商而言,這無疑是一個非常大的負(fù)擔(dān)。

因此,對于一些超大數(shù)據(jù)企業(yè)紛紛自己造芯的現(xiàn)象,吳欣指出,“這些芯片本身不一定賺錢,但谷歌、百度、阿里巴巴這些數(shù)據(jù)公司會想做自己的芯片是因為這會讓企業(yè)自己的搜索引擎等業(yè)務(wù)更有效率,在系統(tǒng)層面上能夠享受到好處。”

但是對于創(chuàng)業(yè)企業(yè)而言,資本、人才和客戶都存在問題,“即使大如谷歌,做TPU的團(tuán)隊也并不大,遠(yuǎn)不夠設(shè)計芯片并維持芯片迭代,需要外包給芯片公司,其他的創(chuàng)業(yè)公司又有多少錢和人?”

異構(gòu)集成成為新潮流

在芯片設(shè)計和制造成本越來越高的情況下,異構(gòu)集成作為先進(jìn)封裝技術(shù)越來越受關(guān)注,被認(rèn)為是增加芯片功能,及降低成本的可行方法,也被視為延續(xù)摩爾定律的新路徑。

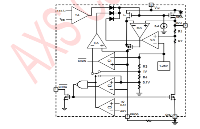

異構(gòu)集成主要指將多個單獨制造的部件封裝到一個芯片上,以增強功能性和提高工作性能,可以對采用不同工藝、不同功能、不同制造商制造的組件進(jìn)行封裝。通過這一技術(shù),工程師可以像搭積木一樣,在芯片庫里將不同工藝的小芯片組裝在一起。

吳欣舉例稱,“我們做第一顆異構(gòu)集成芯片是V2000T。如果當(dāng)時不用異構(gòu)集成的話,芯片要大很多。這么大的芯片良率太低,一片12寸的晶圓在當(dāng)時只能出兩個通過良品測試的芯片。“

他解釋稱,良率和面積并不是線性關(guān)系,而是呈指數(shù)關(guān)系,“如果把這顆原本很大的芯片切分成四塊,每片晶圓能有100個通過良品測試的裸晶片,再把每四個組成一顆完整的芯片,就可以有25顆芯片。考慮到額外的一些損失,即使損失一半也還剩12顆;對客戶來說,也不需要花6倍的價錢去買。”

以賽靈思的FPGA產(chǎn)品為例,吳欣告訴記者,通過采用異構(gòu)集成技術(shù),最近幾代FPGA容納的最大邏輯單元數(shù)量比起僅靠摩爾定律增加了70%甚至一倍以上。

不過,異構(gòu)集成在延續(xù)摩爾定律的同時也面臨可靠性、散熱、測試難度等多方面的挑戰(zhàn)。

更復(fù)雜的封裝技術(shù)意味著測試也更難。常規(guī)的芯片測試中,一個芯片測試后進(jìn)行封裝再進(jìn)行整體測試。而系統(tǒng)化封裝中,對每個小芯片的性能測試以及整體系統(tǒng)的測試無疑讓芯片測試變得更加復(fù)雜。

吳欣指出,異構(gòu)集成并不簡單,要讓集成的芯片和單片芯片具有一樣的可靠性需要很多工作。

同時,他強調(diào),異構(gòu)集成時代更看重終端應(yīng)用場景,而不是功能越強越好,“以前摩爾定律的黃金時代,芯片工藝從90nm到65nm到40nm,不用想,40nm肯定比65nm要好。 但是異構(gòu)集成不是這樣,能力越強成本也越高,并不存在哪種技術(shù)一定更好,而是說你的產(chǎn)品最適合哪個就去選哪個。”

-

芯片

+關(guān)注

關(guān)注

456文章

51192瀏覽量

427316 -

摩爾定律

+關(guān)注

關(guān)注

4文章

636瀏覽量

79235 -

異構(gòu)集成

+關(guān)注

關(guān)注

0文章

34瀏覽量

1918

發(fā)布評論請先 登錄

相關(guān)推薦

如何判定線性穩(wěn)壓器是否存在過熱問題?工作溫度范圍的重要性影響多方面因素

租用站群服務(wù)器時如何降低成本?

中國AI企業(yè)創(chuàng)新降低成本打造競爭力模型

在飽和狀態(tài)下運行UCC2888x離線降壓以降低成本

AI即服務(wù)平臺的優(yōu)勢

【?嵌入式機(jī)電一體化系統(tǒng)設(shè)計與實現(xiàn)?閱讀體驗】+磁力輸送機(jī)系統(tǒng)設(shè)計的創(chuàng)新與挑戰(zhàn)

CC2340系統(tǒng)降低成本的方案剖析

SOLIDWORKS 2024多方面優(yōu)勢

risc-v多核芯片在AI方面的應(yīng)用

工業(yè)觸摸顯示屏在提升生產(chǎn)效率、降低成本等方面具有顯著優(yōu)勢

是德科技5G O-RAN端到端解決方案助力技術(shù)創(chuàng)新并降低成本

ZR機(jī)械手:提高生產(chǎn)效率,降低成本的有效途徑-速程精密

異構(gòu)集成被認(rèn)為是增強功能及降低成本的可行方法 但也面臨多方面的挑戰(zhàn)

異構(gòu)集成被認(rèn)為是增強功能及降低成本的可行方法 但也面臨多方面的挑戰(zhàn)

評論