最新消息稱微軟正開始在Win10上開發(fā)基于USB4.0的驅(qū)動程序,大量廠商已經(jīng)開發(fā)基于USB4.0的設(shè)備,或許不用多久,我們就可以使用上基于USB4.0接口的設(shè)備,從而大大的提高傳輸速度。那么USB4.0是什么?USB4.0的前世今生到底是怎么回事,他和USB3.0、2.0都是什么關(guān)系?且聽我慢慢道來。

USB4.0統(tǒng)一接口

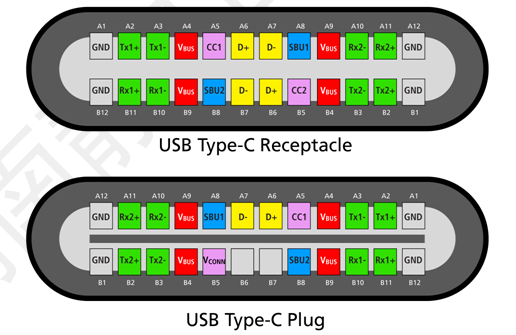

目前市場是我們能聽到的或者見到的USB接口有多少種呢?USB2.0、USB3.0、USB3.1、USB3.1 Gen1、USB3.2 Gen2,包括即將發(fā)布的USB4.0,除了這些協(xié)議規(guī)范之外,還有Type-A、Type-C、USB公頭母頭等等各種不同的概念,但是也許以后這樣的日子會一去不復(fù)返因為在USB 4.0以后也許就只有一種接口了。

USB歷史回顧

回望USB從二十年前的1.0起,截至今天廣泛為人所接受的3.0,USB標準總共經(jīng)歷了四個版本的迭代:

1995年,第一代USB接口USB1.0發(fā)布,最大特點是支持熱插拔(帶電插拔)和即插即用(Plug and Play)。USB1.0 低速(Low Speed) 傳輸速率為 1.5Mbps。

2000年,USB2.0在1.0基礎(chǔ)上,速度升級到480mbps,速度是USB1.0的40倍,被稱為USB 2.0的高速(High-speed)版本。

2014年,USB3.0面世,速度5.0Gbps(500MB/s),這個速度將較之現(xiàn)在的5Gbps快一倍之多。

由于USB 3.0增加了更多并行模式的物理總線,并利用了雙向數(shù)據(jù)傳輸模式,而USB 2.0時代是半雙工模式。簡單來說,數(shù)據(jù)只需要朝一個方向流動就可以了,簡化了等待引起的時間消耗。

隨著要傳輸?shù)臄?shù)據(jù)越來越大,USB規(guī)格仍在進化。在更新一代的電腦里,USB3.1的速度被提升到了10Gbps,而達到這種傳輸速度的USB接口,被稱之為USB3.1 Gen2。

USB4.0以USB3.2/2.0架構(gòu)為基礎(chǔ)打造,重新定義多終端設(shè)備共享和單路高速鏈路連接方案,具備自動擴展數(shù)據(jù)分配能力,多種數(shù)據(jù)傳輸時互不影響,并可最大限度高效利用帶寬,雙通道環(huán)境下最高可達40Gbps。USB 4.0速度是USB 3.0的8倍。

光從字來理解也不夠生動,那我們來看圖說話標識一下。

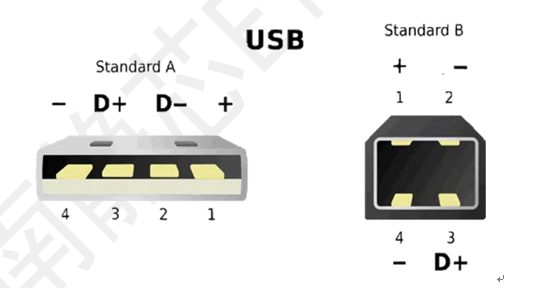

前面說的那些都是USB的協(xié)議版本,它代表的是版本的迭代,新的協(xié)議版本越高代表著傳輸速度會越快,至于上圖中的接口外觀出現(xiàn)了兩種的類型一個Type-A、B和C三種類型。在AB兩個版本里面各有三個級別一個標準版本,一個是mini版本和微接口版本。這就是為什么我們見到的USB接口為啥這么多的原因,協(xié)議不同接口不同就會多生出一個接口類型,但其實這都是屬于USB接口范疇。

USB 3.0和USB 3.1 Gen1

其實上面的USB接口命名已經(jīng)很多了,但是這個時候一個大佬可能是覺得這種命名不符合它的身份,為了彰顯其魅力,并且為了體現(xiàn)它的先進性他把接口名稱描述為USB3.1 Gen1,這個公司就是蘋果,其在Macbook Pro電腦上使用了全新的USB Type-C接口,然后描述的是新一代的 USB 3.1 Gen1,大家都知道蘋果公司的號召力的確不一般,因為它的這個改名舉動,大量的廠商也開始玩起來這種換湯不換藥的文字游戲,也紛紛改名。這迫使USB協(xié)會最終把USB3.0規(guī)范改名為USB3.1 Gen1,也就是說你用的USB3.0和USB 3.1 Gen1其實從傳輸速度和使用的協(xié)議來說是一模一樣的東西。

總結(jié):

1.USB 3.0接口通常為藍色,一定會有5個以上的觸點,而USB 2.0接口的觸點不會超過5個;

2.USB 3.1 Gen1就是USB 3.0換了個馬甲;

3.不要見到USB Type-C就以為它會更快,速度請認準USB 3.1 Gen2.

各個接口的實際傳輸速率

更高的傳輸標準

隨著USB的傳輸數(shù)據(jù)的要求越來越高,比如外接顯卡或者是通過USB接口外接高清顯示器,這些要求對于USB傳輸?shù)乃俾室蟾撸词故荱SB3.1都被提升到了10Gbps/秒也不能擋住對高速率和高功率版本輸出的要求,這個時候又推出了USB3.1 Gen2,也有稱為SuperSpeed+ USB,在USB3.1 Gen1的速度上翻了一倍,達到20Gbps/秒。

但是對于科技進步的探索,人類是永無止盡的,由于intel大力的推廣雷電3接口技術(shù),該技術(shù)該技術(shù)允許串接多臺設(shè)備,并最終達到總40Gbps/秒的帶寬,同時這一接口還能同時傳輸顯示信號,并且能傳送不超過100w的電力。也就是說雷電3接口可以保證在同一根線下面能夠?qū)崿F(xiàn)傳輸視頻數(shù)據(jù)和電力輸送功能,那么USB4.0直接也照辦了這個協(xié)議,也就是說USB4.0不僅實現(xiàn)了速率的提升,還實現(xiàn)了雷電3協(xié)議所能提供的能力,真是集強大能力為一身啊。并且接口同一采用Type-C接口來實現(xiàn)接口的外觀統(tǒng)一。

當然以上技術(shù)的實現(xiàn),主要還是得感謝intel將私有化的Thunderbolt協(xié)議公開給大家來使用,才真正的促使了USB4.0的誕生。

因為USB4.0直連CPU的PCIE總線,最高傳輸速率能達到40Gbps,同時還能傳輸Displayport視頻信號和USB PD快充電流的新一代USB外設(shè)傳輸協(xié)議,它本質(zhì)上是Intel的Thunderbolt3技術(shù),但同時也支持USB協(xié)議,因此它能完美向下兼容Thunderbolt3、USB3.2、USB3.1及USB2.0協(xié)議,這也就是為USB4.0即將開始大規(guī)模普及奠定了普及推廣的基石。可以預(yù)見的是在未來我們所有的使用設(shè)備外接接口將會被USB 4.0所統(tǒng)一。

-

接口

+關(guān)注

關(guān)注

33文章

8694瀏覽量

151929 -

usb

+關(guān)注

關(guān)注

60文章

7981瀏覽量

266118 -

USB4

+關(guān)注

關(guān)注

1文章

141瀏覽量

6420

發(fā)布評論請先 登錄

相關(guān)推薦

安泰功率放大器應(yīng)用:納米材料的前世今生

深入了解Java泛型——從前世今生到PECS原則

400Hz中頻電源前世今生未來

帶你揭秘:功率放大器的前世今生~

USB-C 與 USB-A 的區(qū)別

訊飛星火大模型V4.0正式發(fā)布

USB 4.0靜電保護方案

USB 2.0靜電保護方案

求助,關(guān)于STM32F1 USB庫Custom HID時鐘問題求解

嵌入式系統(tǒng)的前世今生

淺析USB4.0的前世今生

淺析USB4.0的前世今生

評論