FPGA(Field Programmable Gates Array 現場可編程門陣列,內部結構為門陣列構成靜態存儲器(SRAM)。該SRAM可構成函數發生器,即查找表,通過查找表可實現邏輯函數功能)

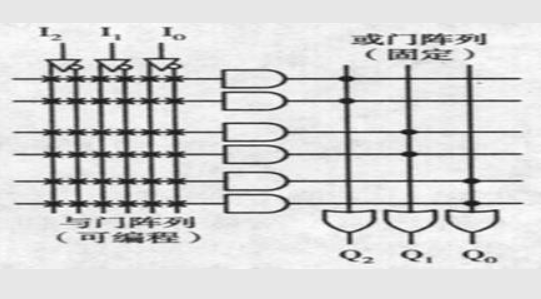

CPLD(Complex Programmable Logic Device 復雜可編程邏輯器件,內部結構為“與或陣列”。該結構來自于典型的PAL、GAL器件的結構。任意一個組合邏輯都可以用“與—或”表達式來描述,所以該“與或陣列”結構能實現大量的組合邏輯功能)

簡單的“與或”陣列:(PAL、GAL、CPLD)

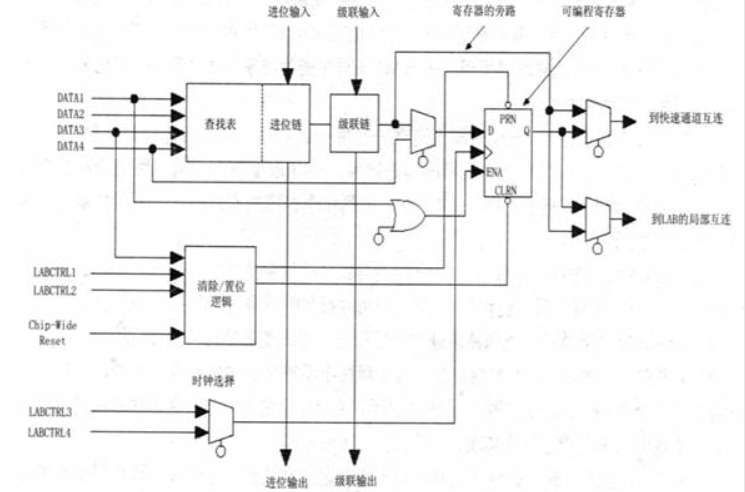

含查找表的邏輯單元:(FPGA)

CPLD和FPGA的主要區別:

1、布線能力

CPLD內連率高,不需要人工布局布線來優化速度和面積,較FPGA更適合于EDA芯片設計的可編程驗證。

2、延遲小預測能力

CPLD連續式布線結構決定時序延時是均勻的和可預測的,FPGA分段式布線結構決定了不可預測時間延遲。

3、集成度的不同

CPLD:500 ~ 50000門; FPGA:1K ~ 10M 門

4、應用范圍的不同

CPLD邏輯能力強而寄存器少,適用于控制密集型系統;

FPGA邏輯能力較弱但寄存器多,適于數據密集型系統。

CPLD和FPGA的優點:

1.規模越來越大,實現功能越來越強,同時可以實現系統集成。

2.研制開發費用低,不承擔投片風險,使用方便。

3.通過開發工具在計算機上完成設計,電路設計周期短。

4.不需要設計人員了解很深的IC知識,EDA軟件易學易用。

5.通過FPGA和CPLD開發的系統成熟后,可以進行ASIC設計,形成批量生產。

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605996 -

cpld

+關注

關注

32文章

1257瀏覽量

169633 -

sram

+關注

關注

6文章

768瀏覽量

114884

發布評論請先 登錄

相關推薦

FPGA與CPLD到底有什么區別

FPGA與CPLD到底有什么區別

評論