TTL和CMOS門(mén)電路的區(qū)別:

1. TTL和帶緩沖的TTL信號(hào) 輸出高電平》2.4V,輸出低電平《0.4V。在室溫下,一般輸出高電平是3.5V,輸出低電平是0.2V。最小輸入高電平和低電平:輸入高電平》=2.0V,輸入低電平《=0.8V,噪聲容限是0.4V。

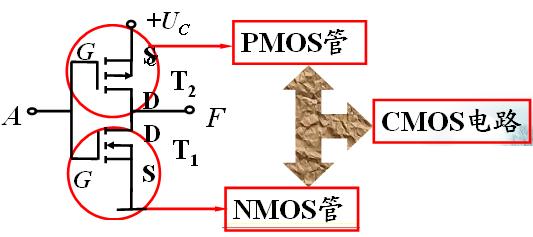

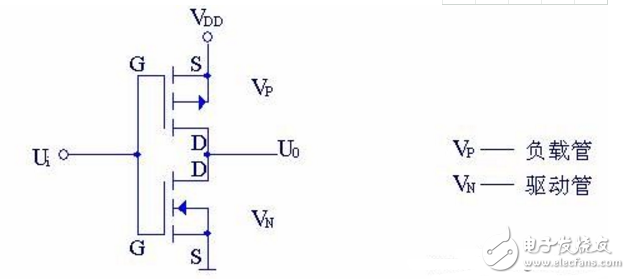

2. CMOS電平:

1邏輯電平電壓接近于電源電壓,0邏輯電平接近于0V。而且具有很寬的噪聲容限。

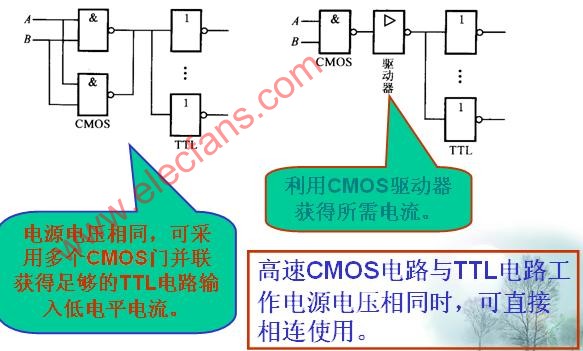

3. 電平轉(zhuǎn)換電路:

因?yàn)門(mén)TL和COMS的高低電平的值不一樣(ttl 5v《==》cmos 3.3v),所以互相連接時(shí)需要電平的轉(zhuǎn)換:就是用兩個(gè)電阻對(duì)電平分壓,沒(méi)有什么高深的東西。

4. OC門(mén),即集電極開(kāi)路門(mén)電路,OD門(mén),即漏極開(kāi)路門(mén)電路,必須外界上拉電阻和電源才能將開(kāi)關(guān)電平作為高低電平用。否則它一般只作為開(kāi)關(guān)大電壓和大電流負(fù)載,所以又叫做驅(qū)動(dòng)門(mén)電路。

5. TTL和COMS電路比較:

1)TTL電路是電流控制器件,而coms電路是電壓控制器件。

2)TTL電路的速度快,傳輸延遲時(shí)間短(5-10ns),但是功耗大。COMS電路的速度慢,傳輸延遲時(shí)間長(zhǎng)(25-50ns),但功耗低。COMS電路本身的功耗與輸入信號(hào)的脈沖頻率有關(guān),頻率越高,芯片集越熱,這是正常現(xiàn)象。

3)COMS電路的鎖定效應(yīng):

COMS電路由于輸入太大的電流,內(nèi)部的電流急劇增大,除非切斷電源,電流一直在增大。這種效應(yīng)就是鎖定效應(yīng)。當(dāng)產(chǎn)生鎖定效應(yīng)時(shí),COMS的內(nèi)部電流能達(dá)到40mA以上,很容易燒毀芯片。

防御措施: 1)在輸入端和輸出端加鉗位電路,使輸入和輸出不超過(guò)不超過(guò)規(guī)定電壓。

2)芯片的電源輸入端加去耦電路,防止VDD端出現(xiàn)瞬間的高壓。

3)在VDD和外電源之間加線流電阻,即使有大的電流也不讓它進(jìn)去。

4)當(dāng)系統(tǒng)由幾個(gè)電源分別供電時(shí),開(kāi)關(guān)要按下列順序:開(kāi)啟時(shí),先開(kāi)啟COMS電路得電源,再開(kāi)啟輸入信號(hào)和負(fù)載的電源;關(guān)閉時(shí),先

關(guān)閉輸入信號(hào)和負(fù)載的電源,再關(guān)閉COMS電路的電源。

6. COMS電路的使用注意事項(xiàng)

1)COMS電路時(shí)電壓控制器件,它的輸入總抗很大,對(duì)干擾信號(hào)的捕捉能力很強(qiáng)。所以,不用的管腳不要懸空,要接上拉電阻或者下拉電阻,

給它一個(gè)恒定的電平。

2)輸入端接低內(nèi)組的信號(hào)源時(shí),要在輸入端和信號(hào)源之間要串聯(lián)限流電阻,使輸入的電流限制在1mA之內(nèi)。

3)當(dāng)接長(zhǎng)信號(hào)傳輸線時(shí),在COMS電路端接匹配電阻。

4)當(dāng)輸入端接大電容時(shí),應(yīng)該在輸入端和電容間接保護(hù)電阻。電阻值為R=V0/1mA.V0是外界電容上的電壓。

5)COMS的輸入電流超過(guò)1mA,就有可能燒壞COMS。

7. TTL門(mén)電路中輸入端負(fù)載特性(輸入端帶電阻特殊情況的處理):

1)懸空時(shí)相當(dāng)于輸入端接高電平。因?yàn)檫@時(shí)可以看作是輸入端接一個(gè)無(wú)窮大的電阻。

2)在門(mén)電路輸入端串聯(lián)10K電阻后再輸入低電平,輸入端出呈現(xiàn)的是高電平而不是低電平。因?yàn)橛蒚TL門(mén)電路的輸入端負(fù)載特性可知,只有在輸

入端接的串聯(lián)電阻小于910歐時(shí),它輸入來(lái)的低電平信號(hào)才能被門(mén)電路識(shí)別出來(lái),串聯(lián)電阻再大的話輸入端就一直呈現(xiàn)高電平。這個(gè)一定要注意。COMS門(mén)電路就不用考慮這些了。

8. TTL電路有集電極開(kāi)路OC門(mén),MOS管也有和集電極對(duì)應(yīng)的漏極開(kāi)路的OD門(mén),它的輸出就叫做開(kāi)漏輸出。OC門(mén)在截止時(shí)有漏電流輸出,那就是漏電流,為什么有漏電流呢?那是因?yàn)楫?dāng)三機(jī)管截止的時(shí)候,它的基極電流約等于0,但是并不是真正的為0,經(jīng)過(guò)三極管的集電極的電流也就不是真正的 0,而是約0。而這個(gè)就是漏電流。開(kāi)漏輸出:OC門(mén)的輸出就是開(kāi)漏輸出;OD門(mén)的輸出也是開(kāi)漏輸出。它可以吸收很大的電流,但是不能向外輸出的電流。所以,為了能輸入和輸出電流,它使用的時(shí)候要跟電源和上拉電阻一齊用。OD門(mén)一般作為輸出緩沖/驅(qū)動(dòng)器、電平轉(zhuǎn)換器以及滿足吸收大負(fù)載電流的需要。

9. 什么叫做圖騰柱,它與開(kāi)漏電路有什么區(qū)別?

TTL集成電路中,輸出有接上拉三極管的輸出叫做圖騰柱輸出,沒(méi)有的叫做OC門(mén)。因?yàn)門(mén)TL就是一個(gè)三級(jí)關(guān),圖騰柱也就是兩個(gè)三級(jí)管推挽相連。所以推挽就是圖騰。一般圖騰式輸出,高電平400UA,低電平8MA

TTL電平信號(hào)被利用的最多是因?yàn)橥ǔ?shù)據(jù)表示采用二進(jìn)制規(guī)定,+5V等價(jià)于邏輯“1”,0V等價(jià)于邏輯“0”,這被稱做TTL(晶體管-晶體管邏輯電平)信號(hào)系統(tǒng),這是計(jì)算機(jī)處理器控制的設(shè)備內(nèi)部各部分之間通信的標(biāo)準(zhǔn)技術(shù)。

TTL電平信號(hào)對(duì)于計(jì)算機(jī)處理器控制的設(shè)備內(nèi)部的數(shù)據(jù)傳輸是很理想的,首先計(jì)算機(jī)處理器控制的設(shè)備內(nèi)部的數(shù)據(jù)傳輸對(duì)于電源的要求不高以及熱損耗也較低,另外TTL電平信號(hào)直接與集成電路連接而不需要價(jià)格昂貴的線路驅(qū)動(dòng)器以及接收器電路;再者,計(jì)算機(jī)處理器控制的設(shè)備內(nèi)部的數(shù)據(jù)傳輸是在高速下進(jìn)行的,而TTL接口的操作恰能滿足這個(gè)要求。TTL型通信大多數(shù)情況下,是采用并行數(shù)據(jù)傳輸方式,而并行數(shù)據(jù)傳輸對(duì)于超過(guò)10英尺的距離就不適合了。這是由于可靠性和成本兩面的原因。因?yàn)樵诓⑿薪涌谥写嬖谥嗪筒粚?duì)稱的問(wèn)題,這些問(wèn)題對(duì)可靠性均有影響;另外對(duì)于并行數(shù)據(jù)傳輸,電纜以及連接器的費(fèi)用比起串行通信方式來(lái)也要高一些。 10. 閑置引腳處理:

1)CMOS數(shù)字電路的空閑引腳,應(yīng)該根據(jù)CMOS數(shù)字電路的種類、引腳的功能和電路的邏輯要求,分 不同的情況進(jìn)行處理。

1. 對(duì)于多余的輸出端一般應(yīng)該懸空;

2. 對(duì)于一個(gè)集成塊中多余不用的門(mén)電路或觸發(fā)器,應(yīng)該將其所有的輸入端接地(或接正電源Vcc);

3. 對(duì)于與門(mén)、與非門(mén)多余的輸入端,可將其接正電源Vcc;也可將其與使用中的輸入端并接在一起使用;

4. 對(duì)于或門(mén)、或非門(mén)多余的輸入端,可將其接地;也可將其與使用中的輸入端并接使用;

5. 對(duì)于觸發(fā)器、計(jì)數(shù)器、譯碼器、寄存器等數(shù)字電路不用的輸入端,應(yīng)該根據(jù)電路邏輯功能的要求,將其接正電源Vcc或接地。例如:對(duì)于不用

的清零端R(“1”電平清零)應(yīng)將其接地;而對(duì)于不用的清零端R(“0”低電平清零)則應(yīng)將其接正電源Vcc.

2)TTL集成門(mén)電路使用時(shí),對(duì)于閑置輸入端(不用的輸入端)一般不懸空,主要是防止干擾信號(hào)從懸空輸入端引入電路。對(duì)于閑置輸入端的處理以不改變電路邏輯狀態(tài)及工作穩(wěn)定為原則。常用的方法有以下幾種:

(1)與非門(mén)的閑置輸入端可直接接電源電壓VCC,或通過(guò)1~10kΩ的電阻接電源VCC。

(2)如前級(jí)驅(qū)動(dòng)能力允許時(shí),可將閑置輸入端與有用輸入端并聯(lián)使用。

(3)在外界干擾很小時(shí),與非門(mén)的閑置輸入端可以剪斷或懸空,但不允許接開(kāi)路長(zhǎng)線,以免引入干擾而產(chǎn)生邏輯錯(cuò)誤。

(4)或非門(mén)不使用的閑置輸入端應(yīng)接地,對(duì)與或非門(mén)中不使用的與門(mén)至少有一個(gè)輸入端接地

上拉電阻下拉電阻的總結(jié)-轉(zhuǎn)載

上拉電阻:

1、當(dāng)TTL電路驅(qū)動(dòng)COMS電路時(shí),如果TTL電路輸出的高電平低于COMS電路的最低高電平(一般為3.5V),這時(shí)就需要在TTL的輸出端接上拉電阻,以提高輸出高電平的值。

2、OC門(mén)電路必須加上拉電阻,才能使用。

3、為加大輸出引腳的驅(qū)動(dòng)能力,有的單片機(jī)管腳上也常使用上拉電阻。

4、在COMS芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉電阻產(chǎn)生降低輸入阻抗,提供泄荷通路。

5、芯片的管腳加上拉電阻來(lái)提高輸出電平,從而提高芯片輸入信號(hào)的噪聲容限增強(qiáng)抗干擾能力。

6、提高總線的抗電磁干擾能力。管腳懸空就比較容易接受外界的電磁干擾。

7、長(zhǎng)線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾。

上拉電阻阻值的選擇原則包括:

1、從節(jié)約功耗及芯片的灌電流能力考慮應(yīng)當(dāng)足夠大;電阻大,電流小。

2、從確保足夠的驅(qū)動(dòng)電流考慮應(yīng)當(dāng)足夠小;電阻小,電流大。

3、對(duì)于高速電路,過(guò)大的上拉電阻可能邊沿變平緩。綜合考慮

以上三點(diǎn),通常在1k到10k之間選取。對(duì)下拉電阻也有類似道理

對(duì)上拉電阻和下拉電阻的選擇應(yīng)結(jié)合開(kāi)關(guān)管特性和下級(jí)電路的輸入特性進(jìn)行設(shè)定,主要需要考慮以下幾個(gè)因素:

1. 驅(qū)動(dòng)能力與功耗的平衡。以上拉電阻為例,一般地說(shuō),上拉電阻越小,驅(qū)動(dòng)能力越強(qiáng),但功耗越大,設(shè)計(jì)是應(yīng)注意兩者之間的均衡。

2. 下級(jí)電路的驅(qū)動(dòng)需求。同樣以上拉電阻為例,當(dāng)輸出高電平時(shí),開(kāi)關(guān)管斷開(kāi),上拉電阻應(yīng)適當(dāng)選擇以能夠向下級(jí)電路提供足夠的電流。

3. 高低電平的設(shè)定。不同電路的高低電平的門(mén)檻電平會(huì)有不同,電阻應(yīng)適當(dāng)設(shè)定以確保能輸出正確的電平。以上拉電阻為例,當(dāng)輸出低電平時(shí),開(kāi)關(guān)管導(dǎo)通,上拉電阻和開(kāi)關(guān)管導(dǎo)通電阻分壓值應(yīng)確保在零電平門(mén)檻之下。

4. 頻率特性。以上拉電阻為例,上拉電阻和開(kāi)關(guān)管漏源級(jí)之間的電容和下級(jí)電路之間的輸入電容會(huì)形成RC延遲,電阻越大,延遲越大。上拉電阻的設(shè)定應(yīng)考慮電路在這方面的需求。

下拉電阻的設(shè)定的原則和上拉電阻是一樣的。

OC門(mén)輸出高電平時(shí)是一個(gè)高阻態(tài),其上拉電流要由上拉電阻來(lái)提供,設(shè)輸入端每端口不大于100uA,設(shè)輸出口驅(qū)動(dòng)電流約500uA,標(biāo)準(zhǔn)工作電壓是5V,輸入口的高低電平門(mén)限為0.8V(低于此值為低電平);2V(高電平門(mén)限值)。

選上拉電阻時(shí):

500uA x 8.4K= 4.2即選大于8.4K時(shí)輸出端能下拉至0.8V以下,此為最小阻值,再小就拉不下來(lái)了。如果輸出口驅(qū)動(dòng)電流較大,則阻值可減小,保證下拉時(shí)能低于0.8V即可。

當(dāng)輸出高電平時(shí),忽略管子的漏電流,兩輸入口需200uA

200uA x15K=3V即上拉電阻壓降為3V,輸出口可達(dá)到2V,此阻值為最大阻值,再大就拉不到2V了。選10K可用。COMS門(mén)的可參考74HC系列

設(shè)計(jì)時(shí)管子的漏電流不可忽略,IO口實(shí)際電流在不同電平下也是不同的,上述僅僅是原理,一句話概括為:輸出高電平時(shí)要喂飽后面的輸入口,輸出低電平不要把輸出口喂撐了(否則多余的電流喂給了級(jí)聯(lián)的輸入口,高于低電平門(mén)限值就不可靠了)

在數(shù)字電路中不用的輸入腳都要接固定電平,通過(guò)1k電阻接高電平或接地。

1. 電阻作用:

1)接電組就是為了防止輸入端懸空

2)減弱外部電流對(duì)芯片產(chǎn)生的干擾

3) 保護(hù)cmos內(nèi)的保護(hù)二極管,一般電流不大于10mA

4 )上拉和下拉、限流

5)改變電平的電位,常用在TTL-CMOS匹配

6) 在引腳懸空時(shí)有確定的狀態(tài)

7)增加高電平輸出時(shí)的驅(qū)動(dòng)能力。

8)為OC門(mén)提供電流

- 那要看輸出口驅(qū)動(dòng)的是什么器件,如果該器件需要高電壓的話,而輸出口的輸出電壓又不夠,就需要加上拉電阻。

- 如果有上拉電阻那它的端口在默認(rèn)值為高電平你要控制它必須用低電平才能控制如三態(tài)門(mén)電路三極管的集電極,或二極管正極去控制把上拉電阻的電流拉下來(lái)成為低電平。反之,

- 尤其用在接口電路中,為了得到確定的電平,一般采用這種方法,以保證正確的電路狀態(tài),以免發(fā)生意外,比如,在電機(jī)控制中,逆變橋上下橋臂不能直通,如果它們都用同一個(gè)單片機(jī)來(lái)驅(qū)動(dòng),必須設(shè)置初始狀態(tài)。防止直通!

2、定義:

- 上拉就是將不確定的信號(hào)通過(guò)一個(gè)電阻嵌位在高電平!電阻同時(shí)起限流作用!下拉同理!

- 上拉是對(duì)器件注入電流,下拉是輸出電流

- 弱強(qiáng)只是上拉電阻的阻值不同,沒(méi)有什么嚴(yán)格區(qū)分

- 對(duì)于非集電極(或漏極)開(kāi)路輸出型電路(如普通門(mén)電路)提升電流和電壓的能力是有限的,上拉電阻的功能主要是為集電極開(kāi)路輸出型電路輸出電流通道。

3、為什么要使用拉電阻:

- 一般作單鍵觸發(fā)使用時(shí),如果IC本身沒(méi)有內(nèi)接電阻,為了使單鍵維持在不被觸發(fā)的狀態(tài)或是觸發(fā)后回到原狀態(tài),必須在IC外部另接一電阻。

- 數(shù)字電路有三種狀態(tài):高電平、低電平、和高阻狀態(tài),有些應(yīng)用場(chǎng)合不希望出現(xiàn)高阻狀態(tài),可以通過(guò)上拉電阻或下拉電阻的方式使處于穩(wěn)定狀態(tài),具體視設(shè)計(jì)要求而定!

- 一般說(shuō)的是I/O端口,有的可以設(shè)置,有的不可以設(shè)置,有的是內(nèi)置,有的是需要外接,I/O端口的輸出類似與一個(gè)三極管的C,當(dāng)C接通過(guò)一個(gè)電阻和電源連接在一起的時(shí)候,該電阻成為上C拉電阻,也就是說(shuō),如果該端口正常時(shí)為高電平,C通過(guò)一個(gè)電阻和地連接在一起的時(shí)候,該電阻稱為下拉電阻,使該端口平時(shí)為低電平,作用嗎:

比如:當(dāng)一個(gè)接有上拉電阻的端口設(shè)為輸如狀態(tài)時(shí),他的常態(tài)就為高電平,用于檢測(cè)低電平的輸入。

- 上拉電阻是用來(lái)解決總線驅(qū)動(dòng)能力不足時(shí)提供電流的。一般說(shuō)法是拉電流,下拉電阻是用來(lái)吸收電流的,也就是你同學(xué)說(shuō)的灌電流

-

上拉電阻

+關(guān)注

關(guān)注

5文章

363瀏覽量

30732 -

TTL

+關(guān)注

關(guān)注

7文章

504瀏覽量

70426 -

電平轉(zhuǎn)換

+關(guān)注

關(guān)注

3文章

136瀏覽量

33902 -

COMS

+關(guān)注

關(guān)注

1文章

91瀏覽量

33220 -

CMOS門(mén)電路

+關(guān)注

關(guān)注

0文章

6瀏覽量

4927

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

TTL集成門(mén)電路的使用注意事項(xiàng)

轉(zhuǎn)載-------TTL和CMOS門(mén)電路的區(qū)別

CMOS和TTL集成門(mén)電路多余輸入端如何處理?

CMOS和TTL集成門(mén)電路多余輸入端如何處理?

CMOS邏輯門(mén)電路

CMOS集成邏輯門(mén)電路的使用注意事項(xiàng)

CMOS電路驅(qū)動(dòng)TTL電路

TTL和CMOS門(mén)電路的區(qū)別 COMS電路的使用注意事項(xiàng)

TTL和CMOS門(mén)電路的區(qū)別 COMS電路的使用注意事項(xiàng)

評(píng)論