雖然不少人對高速可能有了一點概念性的認識,但往往難以想象在所謂的“高速”情況下,會真正給實際的電路系統(tǒng)帶來什么樣的后果,這里我舉幾個實際的案例來剖析一下高速給PCB設計帶來的一系列問題。

A.某公司早期開發(fā)的一個產(chǎn)品,一直工作良好,可是最近生產(chǎn)出來的一批卻總是毛病不斷,受到許多客戶的抱怨。可是根本沒有對設計進行任何變動,連使用的芯片也是同一型號的,原因是什么呢?

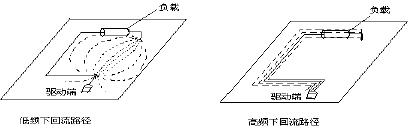

B.某個PCB工程師Layout經(jīng)驗非常豐富,設計的產(chǎn)品很少出過問題,但最近設計了一塊PCB板,卻發(fā)現(xiàn)了EMC檢測不合格的問題,改變布線也毫無效果,但以前類似的板子卻沒有這樣的問題。C.一個專業(yè)的內(nèi)存模塊設計工程師,從EDO內(nèi)存到SDRAM的PC66,PC100,設計過很多項目,很少出現(xiàn)問題,可是自從內(nèi)存時鐘頻率上到133MHz以上時,幾乎很少有設計能一次性通過的。簡單分析一下上面的幾個案例,A的情況是由于芯片的工藝改進造成的,雖然所使用的芯片基本電路功能一樣,但隨著的IC制造工藝水平的提高,信號的上升沿變快了,于是出現(xiàn)了反射、串擾等信號不完整的問題,從而導致突然失效;B例子中,通過細致地檢測,最終發(fā)現(xiàn)是PCB板上有兩個并排平行放置的電感元件,所以產(chǎn)生了較為嚴重的EMI;

C中的內(nèi)存設計師則是因為忽視了嚴格的拓補結構要求,在頻率提高、時序要求更嚴格的情況下,非單調(diào)性和時鐘偏移等問題造成了設計的內(nèi)存模塊無法啟動。除了以上提到的三個實例,還有很多其他的問題,比如因為電容設計不當導致電源電壓不穩(wěn)而無法工作,數(shù)模接地不正確產(chǎn)生的干擾太嚴重使得系統(tǒng)不穩(wěn)定等等。

隨著電子技術的不斷發(fā)展,類似于以上的各種問題層出不窮,而且可以預見,今后還會出現(xiàn)更多的這樣或那樣的問題。所以,了解信號完整性理論,進而指導和驗證高速PCB的設計是一件刻不容緩的事情。

傳統(tǒng)的PCB設計一般經(jīng)過原理圖設計、布局、布線、優(yōu)化等四個主要步驟,由于缺乏高速分析和仿真指導,信號的質(zhì)量無法得到保證,而且大部分問題必須等到制板測試后才能發(fā)現(xiàn),這大大降低了設計的效率,提高了成本,顯然在激烈的市場競爭下,這種設計方法是很不利的。于是,針對高速PCB設計,業(yè)界提出了一種新的設計思路,稱為“自上而下”的設計方法,這是一種建立在實時仿真基礎上優(yōu)化的高效設計流程,見圖1-1-1:從上面的流程圖可以看到,高速的PCB設計在完成之前,經(jīng)過多方面的仿真、分析和優(yōu)化,避免了絕大部分可能產(chǎn)生的問題,如果依托強大的EDA仿真工具,基本上能實現(xiàn)“設計即正確”目的。

在整個高速設計過程中,信號完整性工程師必須貫穿于設計的始終,Cadence公司的首席顧問DonaldTelian曾給信號完整性工程師歸納了七點作用:

研究和定義(pioneeringanddefining)

分類和總結(Partitioning和Approximating)

建模和測量(ModelingandMeasuring)

設計和優(yōu)化(Designingandoptimizing)

量化和驗證(Quantifyingandverifying)

減少和簡化(Reducingandsimplifying)

聯(lián)系和調(diào)試(CorrelatingandDebugging)

對于以上這七大作用的詳細闡述,可以參見1997high-performancesystemDesignConference上DonaldTelian的原稿。

-

內(nèi)存

+關注

關注

8文章

3055瀏覽量

74336 -

PCB設計

+關注

關注

394文章

4701瀏覽量

86358 -

信號完整性

+關注

關注

68文章

1417瀏覽量

95636 -

emc

+關注

關注

170文章

3948瀏覽量

183723 -

華秋DFM

+關注

關注

20文章

3494瀏覽量

4741

發(fā)布評論請先 登錄

相關推薦

高速PCB設計之Allegro實戰(zhàn)解答,教你如何玩轉(zhuǎn)PCB設計!

高速PCB設計經(jīng)驗與體會

Cadence高速PCB設計

高速PCB設計誤區(qū)與對策

高速給PCB設計會帶來什么影響

高速給PCB設計會帶來什么影響

評論