摘要

放下摩爾定律這個定勢思維,或許不是壞事。后摩爾時代的創新不僅“豐富多彩”,而且還隱含著某些哲理,“硅-馮”范式、類硅模式、類腦模式、新興范式等,人類有可能在半導體晶體管和存儲程序計算發明百年后,迎來新興的器件技術與計算架構的工程化。

早前,我們從代表硅技術進步的各代DRAM產品生命周期中,分析計算了硅技術的S曲線,幾種模擬方法得出S曲線的拐點發生在2014~2017(平均為2016) 年間[1]。屆時,硅微電子產業及其R&D總投入均由增速轉為減速,進入成熟發展期,摩爾定律(Moore's Law)開始失靈。早前的這個預測已為當今發展所印證。2016年3月,權威雜志《自然》發文指出,摩爾定律即將終結。與此同時,信守摩爾定律的英特爾公司在10nm節點上一再延后,并將其產品升級的“嘀嗒”(Tick-Tock)節奏模式,更改為“嘀(工藝)-嗒(架構)-嗒(優化)”。

現在不僅學術界,廣大產業界和政界也都認為整個產業已經進入了“后摩爾定律時代”,紛紛部署“后摩爾”技術創新。例如:

2015年, 美國前總統奧巴馬簽署“國家戰略計算推進計劃” (NSCI)總統令,部署“后摩爾定律時代” 技術創新的支持。

2016年, “全球半導體技術路線圖”(ITRS)史無前例地放棄了以摩爾定律為主導的思路,在IEEE重啟計算創議下,更改為“自下而上”、應用推動技術發展的“全球器件與系統路線圖”(IRDS)。

2016年,在中國半導體市場年會暨第五屆集成電路產業創新大會上,工信部領導指出,“后摩爾時代”來臨,多措并舉加快集成電路轉型。

2017年, 美國國防高級研究計劃局(DARPA)啟動了“后摩爾時代”的電子復興計劃。

2018年,歐盟提出有法、德、意、英等國29家公司參與的“后摩爾定律時代半導體增值策略”。

午后陽光依然燦爛,在追逐摩爾定律“狂歡”過后,人們將跳出定勢思維,迎接新時代的新范式。

百花齊放,拓展創新視野

過去,在很長時間里,人們自覺地圍繞摩爾定律的步伐,按部就班升級制程工藝、按部就班搭便車進行工程應用創新。但是,近年來,隨著制程節點列車漸近“終點”,信奉摩爾定律的人們開始碰到進退維谷的困惑:跟隨摩爾定律似乎能夠支撐計算應用的進步,但它又時時阻礙著這種進步。

現在,這種“困惑”正在讓業界人士看到,“放下摩爾定律這個定勢思維,或許不是壞事”!為此,我們根據技術、架構對應用的關系,從技術與架構的分類法中看到(如表1),后摩爾時代的創新不僅“豐富多彩”,而且還隱含著某些哲理,這些,我們可以從以下各個子節介紹中看到。

表1

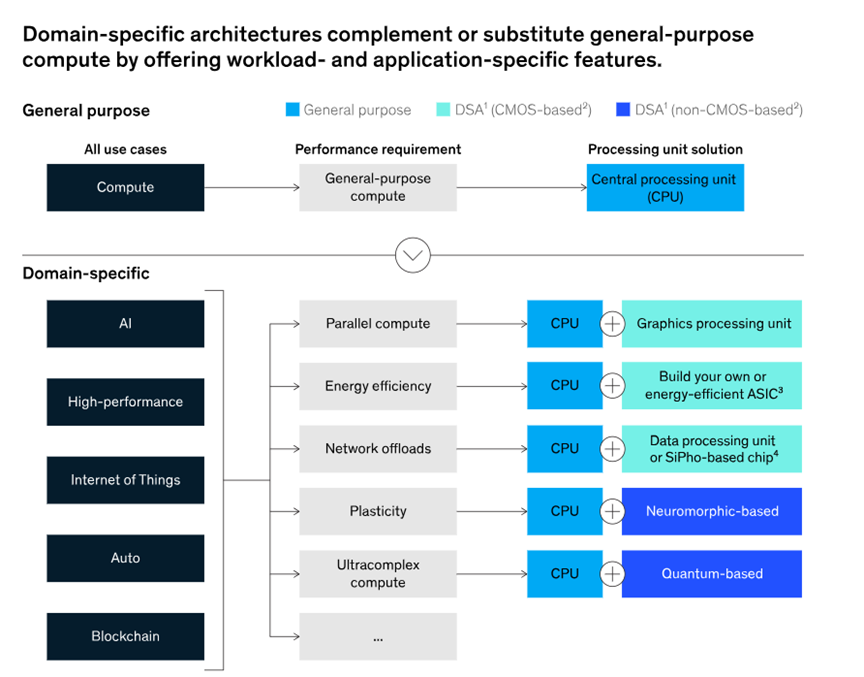

其中,硅CMOS技術與馮諾依曼架構所形成的“硅-馮”范式,涉及技術和架構兩方面的創新。前者包括MOSFET構建的CMOS(平面)和泛CMOS(立體柵FinFET、納米線環柵NWFET 、碳納米管CNTFET、Graphene FET等)技術,后者則是“在串行體制”內進行并行的體系結構創新。該范式盡管暴露了很多問題,但仍“欲罷不能”,還將在相當長的時期內主導著行業的發展。

類硅模式是在馮氏架構下的新興技術創新,涉及NC FET(負電容)、TFET(隧穿)、相變FET、SET(單電子)等仍屬電荷變換的非CMOS技術,由于能延續摩爾定律,受到了半導體業界的重視;

類腦模式是利用包括存儲器在內的各種集成電路和3D封裝模擬神經元特性,摸索存算一體等計算,因其并行性、低功耗的特點,已經在人工智能領域引起了廣泛注意,并已獲得某些工業應用;

新興范式則涉及新的狀態變換(信息強相關電子態/自旋取向)、新興器件技術(自旋器件/量子)和新興架構(量子計算/神經形態計算)。盡管商業化難度很大,但在基礎探索的同時,也開始進入了產業視野。

架構創新,迎來黃金年代

丹納德縮小(Dennard Scaling)、摩爾定律和計算架構是推動“硅-馮”范式技術進步的兩股力量。在過去很長時間里,盡管架構也在不斷創新,但硅CMOS技術每一年半到兩年升級一大檔,引誘了業界越來越傾向于“搭摩爾便車”以適時滿足應用市場的要求,并因此造就了電子信息產業的“一代繁榮”。

但是,到2003年后,丹納德(幾何)縮小開始失效,隨后的等效縮小主要依靠器件結構和新材料的創新,在維持硅芯片集成度和性能的增長趨勢下,付出的代價是功耗不再滿足丹納德恒定電場的設想。

芯片功耗的上升制約了“硅-馮”范式特征產品-硅處理器的性能升級,從單核單線程硅處理器40年發展歷程(見表2)可以看到,硅處理器的集成度和性能翻番規律,只在2003年前符合摩爾定律,之后由于丹納德縮放失效、功耗密度不再不變,年均性能增長大幅下降,翻番年數由1.5年增加到3.5年,隨后更一路下滑到幾乎不再增長,進入了“平臺期”。

表2

單程序硅處理器進入平臺期的時間是2015年,而正是這一年ITRS升級到ITRS2.0,并于2016年更改為IRDS。這些情況表明,丹納德縮放和摩爾定律的終結,使得“硅-馮”范式的創新主體由技術轉向架構,從而迎來架構創新的黃金年代[2]。

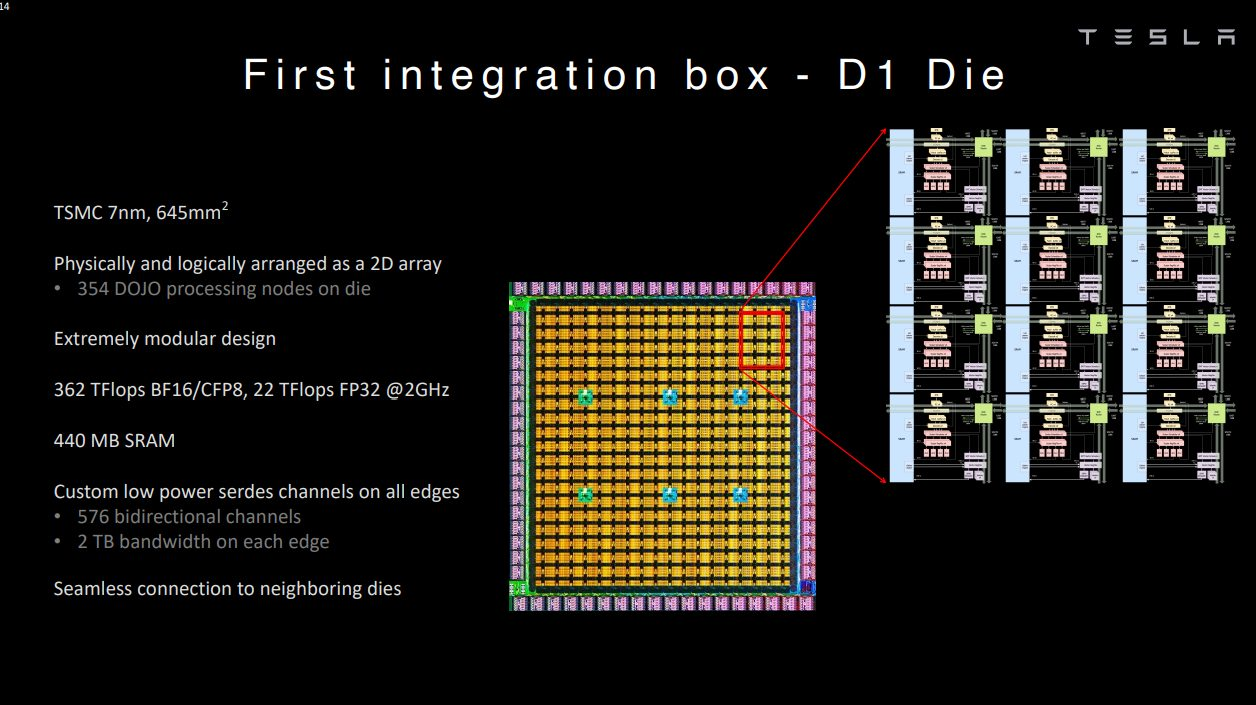

近幾年來,為應對大數據、人工智能等高算力的應用要求,主流芯片架構發生了重大變化,以期增加每瓦、每個時鐘周期內可處理的數據量,為數十年來芯片架構轉變奠定了基礎,使得異構計算(HC)、領域專用計算、可重構計算等得到了很大發展。架構創新所涉及的要點有以下幾個方面:

最大限度地減少數據移動,同時又使數據流最大化;移近計算與存儲、有效利用、提高內存帶寬;提高軟件對硬件的適配性、提高軟件重用性和抽象水平;消除不必要的精確性;容忍適當的近似計算;優化成本、性能、能耗。

異構集成,重塑產業生態

1965年,摩爾以“在集成電路中塞進(Cramming)更多元件”為題發表被譽為“定律”的預測;之后,行業依此思想由小規模集成到大規模集成,一直發展到今天“塞進”了數以百億元件的片上系統(SoCs),把半導體工業推到一個“無以復加”的高度。

但“全則必缺,極則必反”(呂氏春秋·博志)。在工藝制程精細到十幾個、幾個納米的今天,在同一個工藝節點上,把諸多元件“填鴨式(Cramming)”地做成系統,不僅不能同時優化SoCs上不同元部件的特性,還會因此造成“浪費”。另外還因為構成復雜,需要不同團隊的無縫協同,拉長了設計時間,極大地提高了產品成本。例如14nm制程工藝,僅僅驗證花費就高達5千萬美元)。

隨著節點縮小,工藝變得越來越復雜且昂貴,在經典平面縮放耗盡了現有技術資源、應用又要求集成更加靈活和多樣化的今天,若在芯片中還想“塞進更多元件”,就必須擴展到立體三維,從異構集成(HI)中找出路。

2015年(又是這一年)Marvell公司在舊金山的ISSCC(IC奧林匹克賽會)和上海的IC China上提出了模塊化芯片(Modular Chip,MOChiTM )概念:采用DRAM存儲器,CPU、GPU計算元件,LTE Modem、WiFi、南橋等“模塊化”裸芯片,通過異構封裝堆疊成智能手機和筆記本電腦處理器,而這些模塊以前就是一顆SoCs芯片。其中特別要指出的是,異構集成所堆疊的、可置于計算近處的高帶寬存儲器(HBM),在SoCs中是難以實現的。

2017年美國國防高級研究計劃局(DARPA)在其啟動的電子復興計劃中提出名為CHIPS(Common Heterogeneous Integration and IP Reuse Strategies)的項目,參加單位有英特爾、美光、新思科技以及波音、洛克希德等公司。計劃的目標客戶是商業和軍事應用;計劃的思路是建立一個由多方提供的、稱為Chiplet的模塊化裸芯。Chiplet是一種裸管芯(die)形態的IP,譯為“芯粒”比較恰當[3]。它以“搭積木”的方法,采用先進封裝堆疊連接成“多芯粒模組”(MCM)。這是對SoCs的替代,從過去基于IP設計,變為基于芯粒(Chiplet as a IP)設計,它將促進從架構探索到模組實現的EDA工具發展;同時它也是對過去“多芯片模組”(MCM)的螺旋復歸,從過去芯片(Chip)的組裝到現在基于芯粒(Chiplet)的異構集成。這些情況表明,技術對應用的需求,都要回歸到“使用最經濟資源,實現最理想功能 ”的電子系統基本要求上來。

基于異構集成的芯粒具有很多優點,例如:可用不同節點制造,因而不僅優化了各自的性能,而且還因結構緊湊可兼善良率與成本;可以靈活且方便組裝系統,因而能捕捉市場窗口,縮短上市時間;可方便修改設計,更換異構計算中的定制加速部件/協處理器,從而鼓勵、推動芯片架構創新。

在這些優點刺激下,芯粒模式發展迅速。2018年10月,為制定芯粒開放標準、促進芯粒生態系統、催生低成本SoCs替代方案的ODSA (Open Domain-Specific Architecture)組織成立,發起單位僅7家,但半年后就增加到53家,去年底則已擴大到70多家,反應熱烈。值得指出的是,這次芯粒所誘發的產業變革跟上一次Fabless+Foundry完全不同,它是由Intel(IDM)、AMD(Fabless)、TSMC(Foundry)這樣的大企業主導的,因而來勢洶涌,從提出芯粒重用策略到今天才短短幾年就已經形成熱潮。

芯粒是半導體產業方向的重大轉變,它必將重塑行業生態。芯粒雖然對擁有先進封裝能力的IDM、Foundry有利,但產權有可能來自系統商、IP商和Fabless等各個行業部門,而且封測商也占據了與以前稍有不同的重要地位。由芯粒模式所重塑的行業生態將影響著半導體以外的整個電子信息行業。

推陳出新,科學實踐突破

“硅-馮”范式是一個極為龐大而復雜的體系,在70多年趕班車式的發展歷程中,既積累了天文數字的寶貴資源,又暴露了難以解決的問題,從而導致人們既想沿著這條路走下去,以收獲成果,但在途中又碰到阻礙這種成果實現的壁壘。為解決這個矛盾,業界出現了跟半導體更新換代類似的科學實踐。

半導體產業是一個集極端精密(線寬達納米級)和極大規模(僅納米級方孔就數以億計)于一體的工程科學,產品制程工序數以百計,因此在技術與產品更新換代過程中,釆用了“嘀”(工藝升級)-“嗒”(產品換代)策略,即在工藝升級時產品(比如存儲器)架構保持不變,便于找出工藝問題,而在工藝穩定后再換代產品,集中解決新產品本身的問題。

在多元相關復雜的“硅-馮”范式中,早在多年前就已經開始了“嘀”-“嗒”的進步策略,表一中的類硅模式是一個例子,即在馮氏架構不變情況下,沿著電荷狀態變換,尋找可代替CMOS的器件技術,其中除了改善MOS晶體管亞閾值的負電容FET、二維材料FET等外,還進行了諸如納電子機械NEM relay之類的全新機制的技術探索。另一個例子是表一中的類腦模式,它利用現行器件技術模擬非馮架構,其中特別是改變存儲與計算分離的“存內算計算”和區別于“程序流”的“脈沖或尖峰傳遞信息的事件驅動”計算。

縮小變數、聚焦問題的“嘀”-“嗒”研究策略,既能為顛覆性的創新打基礎,又滿足了市場對高算力應用的要求。

超越摩爾,回歸物理基礎

從物理角度看,馮氏計算的性能與頻率正相關,而硅CMOS技術的功耗卻正比于頻率的3次方,“硅-馮”范式碰到了難以逾越的功耗墻瓶頸。一位被譽為可重構計算之父的德國教援R. Hartenstein在2016年提到:“70年前采用馮諾依曼原理是歷史上最大的錯誤之一 ”,某種程度上表明現在已經到了探索新的替代范式的時候了。

道生萬物,萬物復歸于道。技術與計算早期都是始于“模擬”,后來才慢慢“數字化”。經歷了計算與網絡的第一次數字化浪潮、移動計算的第二次數字化浪潮和現在正進入的以數字智能為特征的第三次數字浪潮,計算技術今后不知道還會不會進一步發展。但基于人類認識的螺旋上升特點,在“非0即1”精確可控的高度“數字化”后,又會“復歸”于“模擬”。

自然界有兩個神秘而奇特的現象,一個是詭異的量子疊加與糾纏現象,一個是至今難以說清的腦意識現象,這些現象中的狀態變換,不是“非此即彼”,而是具有概率結構或事件驅動性質的模擬計算。

在摩爾定律逐漸示微的過程中,波粒二象性的量子計算和基于新功能材料的腦靈感神經形態計算必將加速發展,人類有可能在半導體晶體管和存儲程序計算發明百年后,迎來新興的器件技術與計算架構的工程化。屆時,我們又將看到從現在的工程應用創新回歸到物理基礎創新。顛覆性基礎創新將把人類推向更高的文明。

-

半導體

+關注

關注

334文章

27709瀏覽量

222645 -

摩爾定律

+關注

關注

4文章

636瀏覽量

79234 -

晶體管

+關注

關注

77文章

9746瀏覽量

138900

原文標題:后摩爾時代的技術創新

文章出處:【微信號:cjssia,微信公眾號:集成電路園地】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

擊碎摩爾定律!英偉達和AMD將一年一款新品,均提及HBM和先進封裝

AI時代的存儲墻,哪種存算方案才能打破?

石墨烯互連技術:延續摩爾定律的新希望

摩爾定律是什么 影響了我們哪些方面

后摩爾定律時代,提升集成芯片系統化能力的有效途徑有哪些?

奇異摩爾專用DSA加速解決方案重塑人工智能與高性能計算

高算力AI芯片主張“超越摩爾”,Chiplet與先進封裝技術迎百家爭鳴時代

“自我實現的預言”摩爾定律,如何繼續引領創新

封裝技術會成為摩爾定律的未來嗎?

天津大學與佐治亞理工學院共創石墨烯芯片新時代

放下摩爾定律這個定勢思維,或許不是壞事

放下摩爾定律這個定勢思維,或許不是壞事

評論