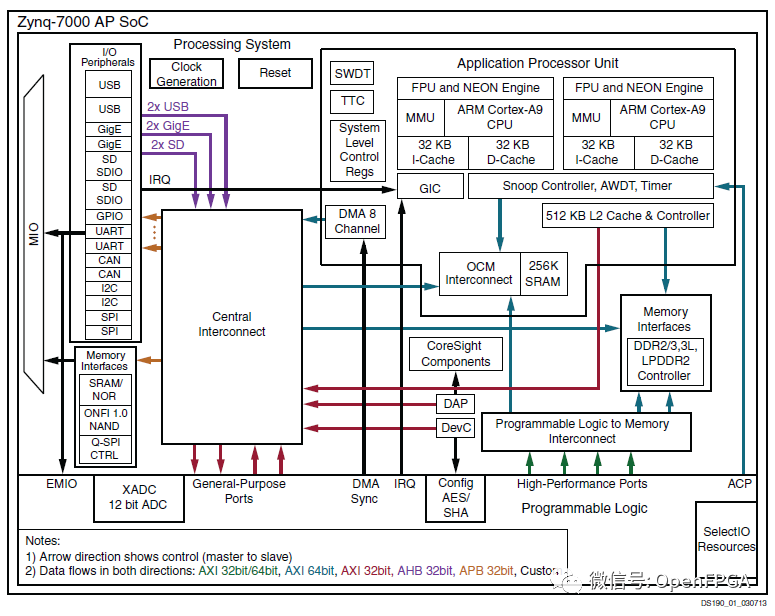

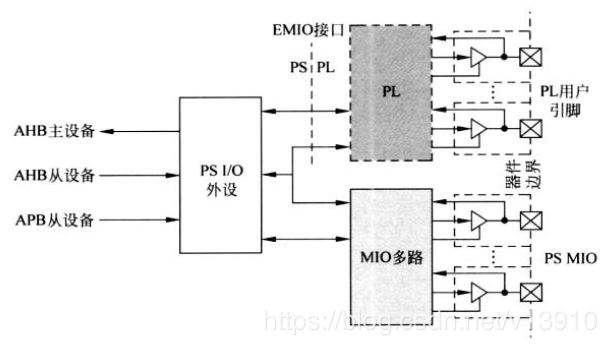

PS部分框圖如上圖所示,PS 和外部接口之間的通信主要是通過復(fù)用的輸入 / 輸出( Multiplexed Input/Output,MIO)實(shí)現(xiàn)的,它提供了可以做靈活配置的 54 個(gè)引腳,這表明外部設(shè)備和引腳之間的映射是可以按需定義的。這樣的連接也可以通過擴(kuò)展 MIO (ExtendedMIO,EMIO)來實(shí)現(xiàn),EMIO 并不是 PS 和外部連接之間的直接通路,而是通過共用了PL 的 I/O 資源來實(shí)現(xiàn)的 。這些都出現(xiàn)在上圖的左側(cè)。當(dāng)需要擴(kuò)展超過 54 個(gè)引腳的時(shí)候可以用 EMIO,而當(dāng) PL 中實(shí)現(xiàn)了一個(gè) IP 包的時(shí)候,這也是 PS 和 PL 中的IP 包接口的一種方法。

可用的 I/O 包括標(biāo)準(zhǔn)通信接口和通用輸入 / 輸出 (General Purpose Input/Output,GPIO),GPIO 可以用做各種用途,包括簡(jiǎn)單的按鈕、開關(guān)和 LED。

在ZYNQ7000系列PS中除了上面提到的MIO和EMIO之外,還包括AXI_GPIO。

這三者關(guān)系如下:

其中MIO和EMIO是直接掛在PS上的GPIO。而AXI_GPIO是通過AXI總線掛在PS上的GPIO上。

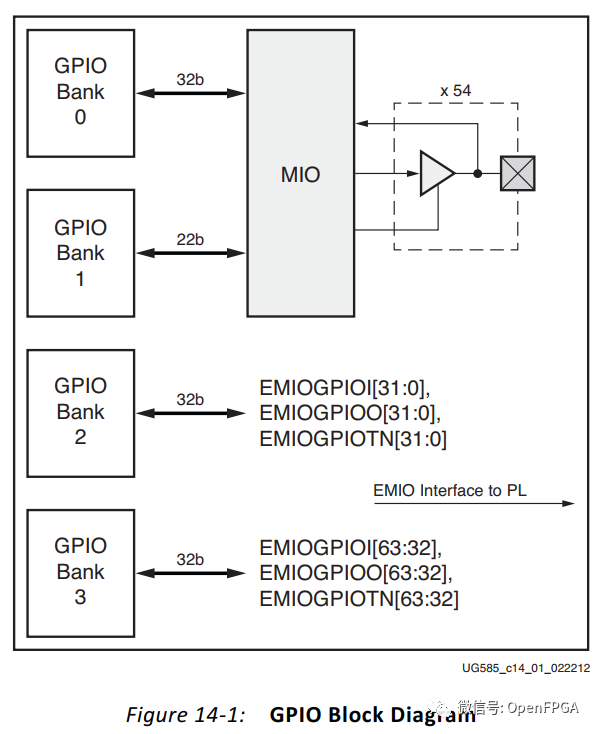

我們先看一下MIO和EMIO:下圖EMIO和MIO的結(jié)構(gòu)。其中MIO分布在BANK0,BANK1,而EMIO則分布在BANK2、BANK3。

注意一下幾項(xiàng):

首先、MIO在zynq上的管腳是固定的,而EMIO,是通過PL部分?jǐn)U展的,所以使用EMIO時(shí)候需要在約束文件中分配管腳,所以設(shè)計(jì)EMIO的程序時(shí),需要生成PL部分的bit文件,燒寫到FPGA中。

其次、由下圖可以看出MIO共占54bit,而EMIO占64bit。其中MIO占用IO號(hào)為0-53。而EMIO占用IO號(hào)為54-117。

再者、無論是EMIO還是MIO都屬于PS上的IO,直接由PS操作。在調(diào)用頭文件,只調(diào)用#include "xgpiops.h"即可,而在調(diào)用AXI_GPIO時(shí),則需要#include "xgpio.h"。

關(guān)于EMIO:

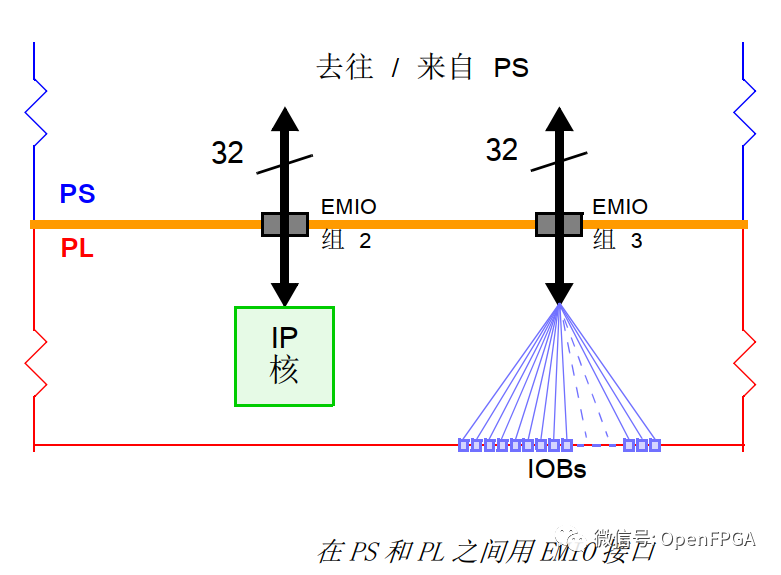

從 PS 出來,有幾種連接可以經(jīng)由 PL 到外部接口上,這被稱作擴(kuò)展的 MIO (Extended MIO) ,即 EMIO。

EMIO 涉及到兩個(gè)域之間的信號(hào)傳輸,是由一組簡(jiǎn)單的導(dǎo)線連接實(shí)現(xiàn)的,因此,EMIO 并不支持所有的 MIO 接口,而支持的那些中,也有些的能力受到了限制 。這些連接被安排成兩個(gè) 32 位的組。

很多情況下,經(jīng)由 EMIO 的接口是直接連接到所需的 PL 的外部引腳上的,這個(gè)連接是由一個(gè)約束(描述)文件中的條目所指定的。在這個(gè)模式下,EMIO 可以實(shí)現(xiàn)額外的 64 個(gè)輸入線和 64 個(gè)帶有輸出始能的輸出線。另一個(gè)選擇是用 EMIO 來連接PS 和 PL 里的外設(shè)模塊。下圖描繪了這兩種使用模式:

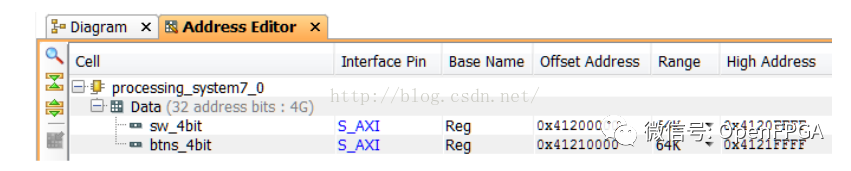

最后看一下,AXI_GPIO相當(dāng)于GPIO的IP核,我們調(diào)用時(shí)是占用相應(yīng)AXI總線地址空間,如下圖,占用地址為0x41200000和0x41210000

-

接口

+關(guān)注

關(guān)注

33文章

8692瀏覽量

151922 -

引腳

+關(guān)注

關(guān)注

16文章

1220瀏覽量

50909 -

GPIO

+關(guān)注

關(guān)注

16文章

1216瀏覽量

52381

原文標(biāo)題:ZYNQ7000系列MIO/EMIO/AXI_GPIO接口

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

MIO與EMIO的關(guān)系解析 GPIO、MIO、EMIO的區(qū)別

Xilinx ZYNQ開發(fā)GPIO的三種方式:MIO、EMIO、AXI_GPIO

分享黑金ZYNQ7000系列視頻教程

玩轉(zhuǎn)Zynq連載31——[ex53] 基于Zynq PS的EMIO控制

ZYNQ的GPIO相關(guān)資料推薦

ZYNQ 的三種GPIO :MIO、EMIO、AXI

Zynq7000系列之芯片引腳功能綜述

被zynq的GPIO唬住,告訴你zynq的3種GPIO

ZYNQ的GPIO簡(jiǎn)介

ZYNQ學(xué)習(xí)筆記_GPIO之輸入輸出

ZYNQ7000系列MIO/EMIO/AXI_GPIO接口

ZYNQ7000系列MIO/EMIO/AXI_GPIO接口

評(píng)論