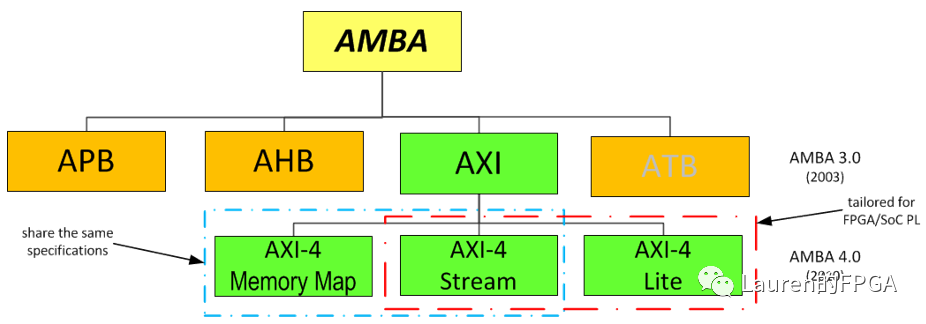

AXI全稱Advanced eXtensibleInterface,是Xilinx從6系列的FPGA開始引入的一種接口協(xié)議,主要描述了主設(shè)備和從設(shè)備之間的數(shù)據(jù)傳輸方式。該協(xié)議是AMBA3.0(Advanced Microcontroller Bus Architecture)中最重要的部分,是一種面向高性能、高帶寬、低延遲的片內(nèi)接口協(xié)議。AMBA4.0將其修改升級(jí)為AXI4.0,如下圖所示。

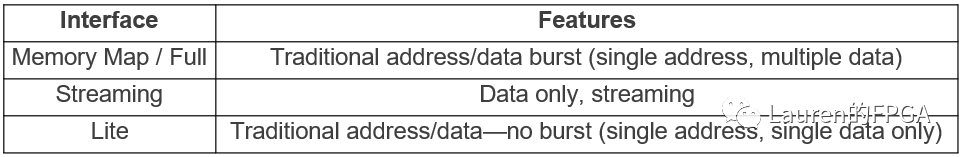

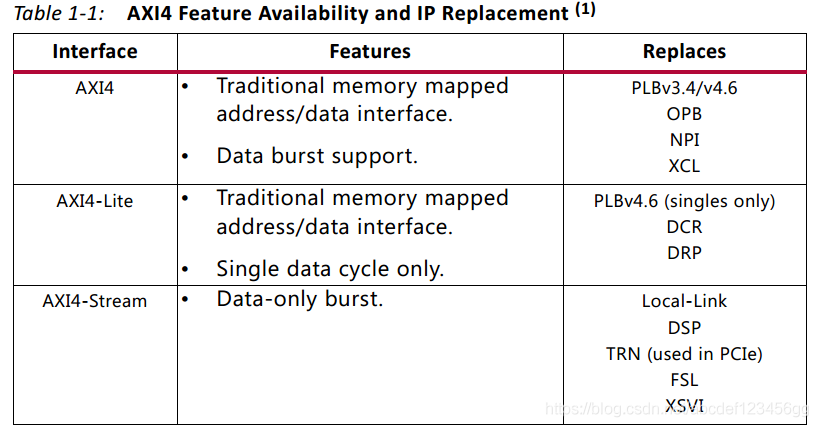

AXI4.0提供三種類型的接口形式,分別是AXI-4 Memory Map(也稱之為AXI-4 Full)、AXI-4 Stream和AXI-4 Lite,三者的特性如下圖所示。

AXI-4 Full協(xié)議相當(dāng)于原來(lái)的AHB協(xié)議,提供高速的系統(tǒng)內(nèi)部互連通道,可以支持burst模式,主要用于處理器訪問(wèn)存儲(chǔ)單元等需要高速數(shù)據(jù)傳輸?shù)膱?chǎng)合;AXI4-Lite相當(dāng)于原來(lái)的APB協(xié)議,主要用于訪問(wèn)一些低速外設(shè);AXI4-Stream接口就像FIFO一樣,數(shù)據(jù)傳輸?shù)臅r(shí)候不需要地址,而是主從設(shè)備直接連續(xù)讀寫數(shù)據(jù),主要用于如視頻、高速AD、PCIe、DMA接口等需要高速數(shù)據(jù)傳輸?shù)膱?chǎng)合,跟Xilinx原來(lái)的Local Link協(xié)議類似。

總體而言,AXI接口協(xié)議具有如下特征:

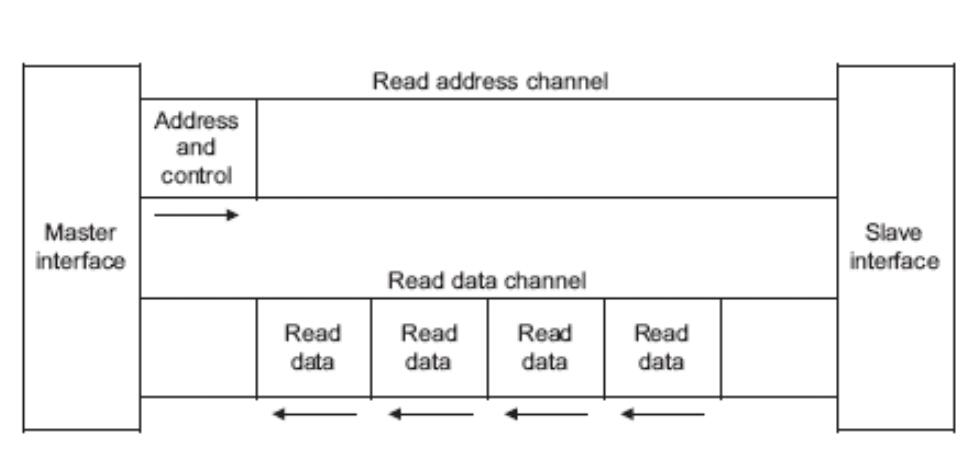

分離的地址/控制、數(shù)據(jù)相位

使用字節(jié)選通,支持非對(duì)齊的數(shù)據(jù)傳輸

基于burst傳輸,只需傳輸首地址

讀、寫數(shù)據(jù)通道分離,能提供低功耗DMA

支持多種尋址方式

支持亂序傳輸

易于添加寄存器級(jí)來(lái)進(jìn)行時(shí)序收斂

AXI并非總線(Bus),總線是如下圖所示的數(shù)據(jù)傳輸和互聯(lián)方式,而AXI是點(diǎn)對(duì)點(diǎn)(Point-to-point)的主從接口協(xié)議。當(dāng)多個(gè)外設(shè)需要互相交互數(shù)據(jù)時(shí),我們需要加入一個(gè)所謂的AXI Interconnect模塊(Xilinx提供了這個(gè)IP),也就是AXI互聯(lián)矩陣,作用是提供將一個(gè)或多個(gè)AXI主設(shè)備連接到一個(gè)或多個(gè)AXI從設(shè)備的一種交換機(jī)制(有點(diǎn)類似于交換機(jī)里面的交換矩陣)。

-

接口協(xié)議

+關(guān)注

關(guān)注

5文章

41瀏覽量

18598 -

AXI

+關(guān)注

關(guān)注

1文章

128瀏覽量

16713

原文標(biāo)題:AXI是Interface還是Bus?

文章出處:【微信號(hào):Lauren_FPGA,微信公眾號(hào):FPGA技術(shù)驛站】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

AXI總線協(xié)議的幾種時(shí)序介紹

XILINX FPGA IP之AXI Traffic Generator

AXI接口協(xié)議詳解

AXI接口協(xié)議詳解

AMBA AXI協(xié)議指南

AXI總線協(xié)議的幾種時(shí)序介紹

自定義sobel濾波IP核,IP接口遵守AXI Stream協(xié)議

FPGA程序設(shè)計(jì):如何封裝AXI_SLAVE接口IP

AXI總線協(xié)議總結(jié)

一文看懂AMBA AXI協(xié)議

AMBA 3.0 AXI總線接口協(xié)議的研究與應(yīng)用

AXI總線協(xié)議簡(jiǎn)介

FPGA AXI4協(xié)議學(xué)習(xí)筆記(二)

AMBA AXI4接口協(xié)議概述

AXI接口協(xié)議的類型和特征

AXI接口協(xié)議的類型和特征

評(píng)論