同步時(shí)鐘是指發(fā)送時(shí)鐘和接收時(shí)鐘是由同一個(gè)MMCM或PLL生成,兩者之間有明確的相位關(guān)系。例如:兩者可以是同頻但有固定相差;或者同相但不同頻。這里我們重點(diǎn)介紹一下同相不同頻的跨時(shí)鐘域路徑,分兩種情形:從慢時(shí)鐘到快時(shí)鐘和從快時(shí)鐘到慢時(shí)鐘。

從慢時(shí)鐘到快時(shí)鐘

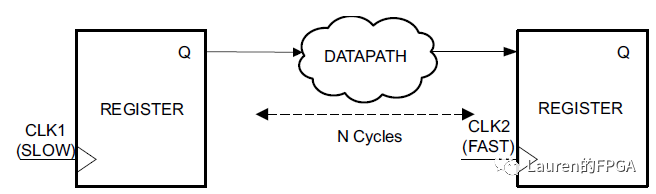

如下圖所示,這里假定CLK2的頻率是CLK1的3倍。這實(shí)際是條多周期路徑。

發(fā)送時(shí)鐘和接收時(shí)鐘之間的關(guān)系如下圖所示。

在只有時(shí)鐘周期約束而沒有多周期路徑約束的情況下,STA(Static Timing Analysis)工具會(huì)認(rèn)為建立時(shí)間檢查和保持時(shí)間檢查如下圖所示。不難看出,保持時(shí)間檢查是合理的,但建立時(shí)間檢查不是期望的。換言之,建立時(shí)間如果按此分析就會(huì)過緊。

-

同步時(shí)鐘

+關(guān)注

關(guān)注

0文章

49瀏覽量

3291

原文標(biāo)題:同步跨時(shí)鐘域路徑如何約束

文章出處:【微信號(hào):Lauren_FPGA,微信公眾號(hào):FPGA技術(shù)驛站】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FPGA設(shè)計(jì)中解決跨時(shí)鐘域的三大方案

關(guān)于跨時(shí)鐘域信號(hào)的處理方法

跨時(shí)鐘域的時(shí)鐘約束介紹

如何處理好FPGA設(shè)計(jì)中跨時(shí)鐘域間的數(shù)據(jù)

關(guān)于FPGA中跨時(shí)鐘域的問題分析

揭秘FPGA跨時(shí)鐘域處理的三大方法

CDC單bit脈沖跨時(shí)鐘域的處理介紹

FPGA跨時(shí)鐘域處理方法(一)

如何處理跨時(shí)鐘域這些基礎(chǔ)問題

同相不同頻的跨時(shí)鐘域路徑介紹

同相不同頻的跨時(shí)鐘域路徑介紹

評(píng)論