S3c2440是三星公司推出的一款基于ARM920T的處理器,采用ARM內核,不同于單片機,無片上rom與ram,必須搭配相應的外圍電路進行使用,現在,讓我們從零開始進行這一塊MCU的學習,為了入門簡單方便,前期我不會搭載任何操作系統,本手冊寫到哪算哪.

1.什么是nor flash啟動和nand flash啟動

在任何視屏教程里面,都會告訴你一個開關左右選擇就能norflash啟動或者nand flash啟動,norflash啟動能直接運行代碼,nand flash啟動不能直接運行代碼,可是為什么呢?

要知道這一點,首先要明白nandflash和norflash的區別,首先,norflash是隨機存儲介質,也就是說,對norflash的操作時可以進行任意單字節的讀寫的,而nanaflash是塊存儲介質,對nandflash的讀寫只能以塊的方式讀寫,也就是說,nand要修改一個字節,必須重寫整個塊

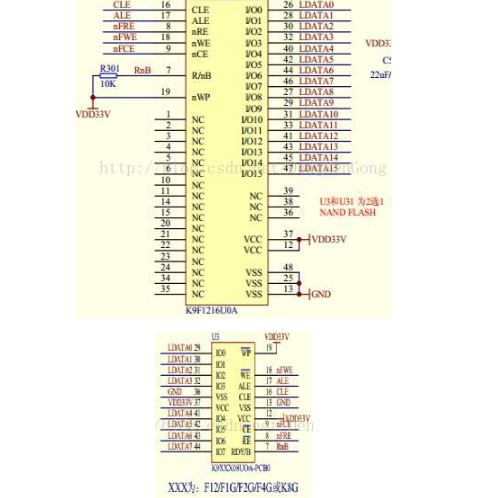

由此我們就可以知道,nand flash不可能作為代碼直接執行的介質了,理論上,就算我們通過電路實現了nand flash執行代碼也不可能,因為代碼執行很重要的一點是可以隨機的對任意一個字節的數據進行任意修改,而nand寫一個字節要重寫整個塊,這速度太慢了,還有一個原因,因為某些工藝因素的影響,nandflash生產過程中就可能出現壞塊,另外,nandflash在多次擦寫中也可能出現壞塊,所以這也決定了nand不可能實現直接運行代碼,只能做存儲器的功能,以下是nandflash電路(TQ2440)

可見,nand flash分為八位和16位,地址線和數據線復用,依靠控制總線來切換地址數據時序,主要的控制線有

CLE:命令鎖存使能線,輸入命令時使用

ALE:地址鎖存使能,輸入地址時使用

NFRE:連接NRE讀使能,讀數據之前,要先讓nre有效

NFWE:寫使能,寫數據的時候這根線有效

RNB :就緒/忙標志,主要用于發送完編程/擦除命令后,檢測操作是否完成

WP :寫保護使能

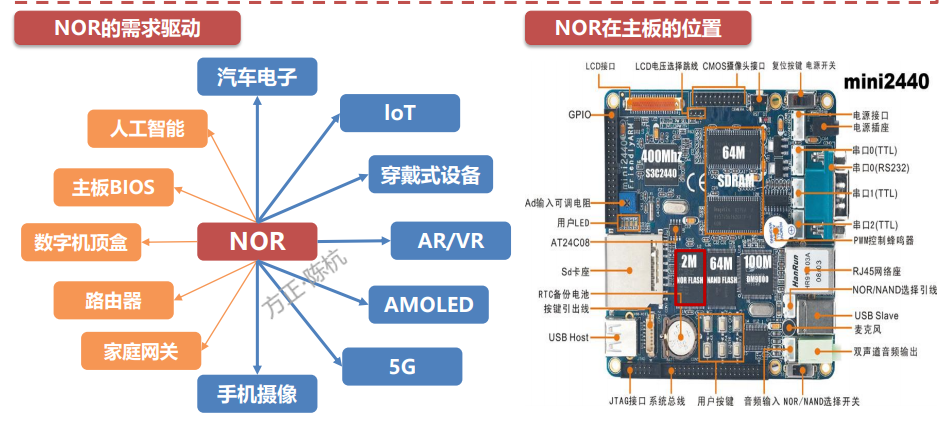

說完nandflash說說norflash,首先norflash的地址線和數據線是分開的,其次,是可以單字節讀取寫入的,另外,可靠性好,不易出現壞塊,使用時間更長,(norflash上帶的是通用sdram接口)

電路圖如下,

因為是16位數據,所以沒有接data0的必要,初始地址是0x00000000,

OE:讀使能

WE寫使能

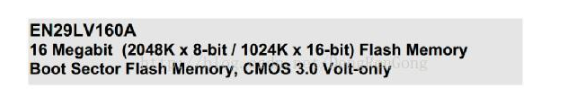

片選接了GCS0,那么norflash尋址范圍是多少呢?首先,選用的芯片是EN29系列,

該系列芯片說明書中說明

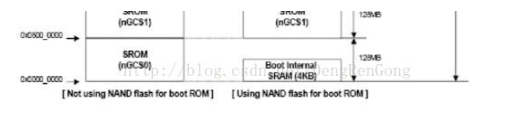

可見,NORFLASH是16M的,但是尋址范圍是不是16M我們還需要確認NGCS0的選通時間,查看memory說明,有這樣一段

也就是說2440的NGCS0分區大小為128M,驅動16M足足夠了,所以,我們可以說,norflash啟動,16M完全可用

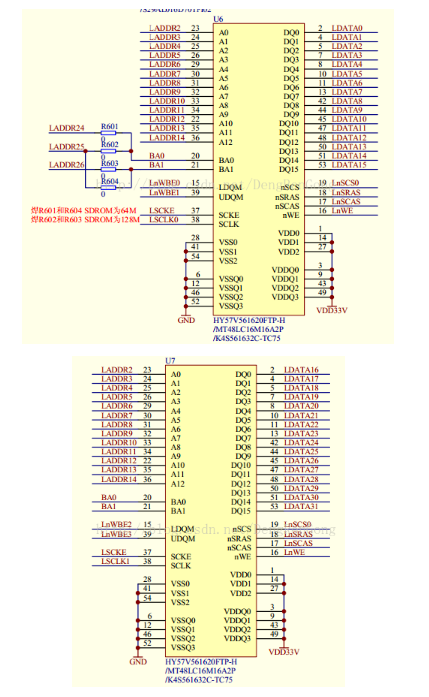

接下來說一下SDRAM,電路圖如下

這是兩塊相同的芯片,兩塊16位芯片合起來將數據總線擴展到32位

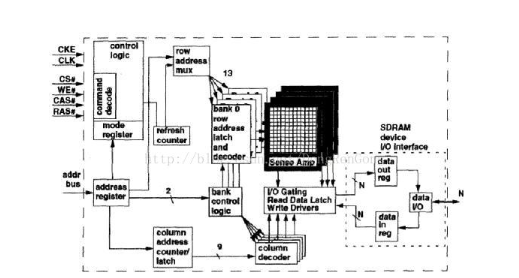

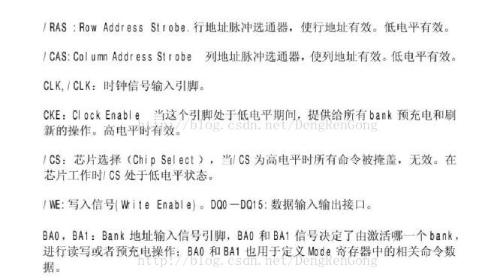

可以看到,地址線和數據線是分離的,控制接口主要由以下幾根線組成

CKE:INPUT控制norflash內部時鐘的使能與禁止,從而進入三種狀態,掉電,掛起,自刷新(為了保持內部數據,設備自身也需要一個時鐘來進行數據自刷新,和外部讀寫時鐘并不是一個概念)

CLK:INPUT外部讀寫時鐘,用于外部讀寫同步

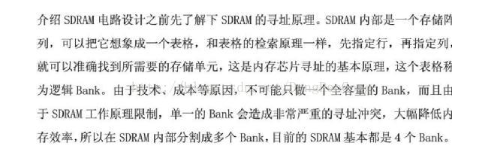

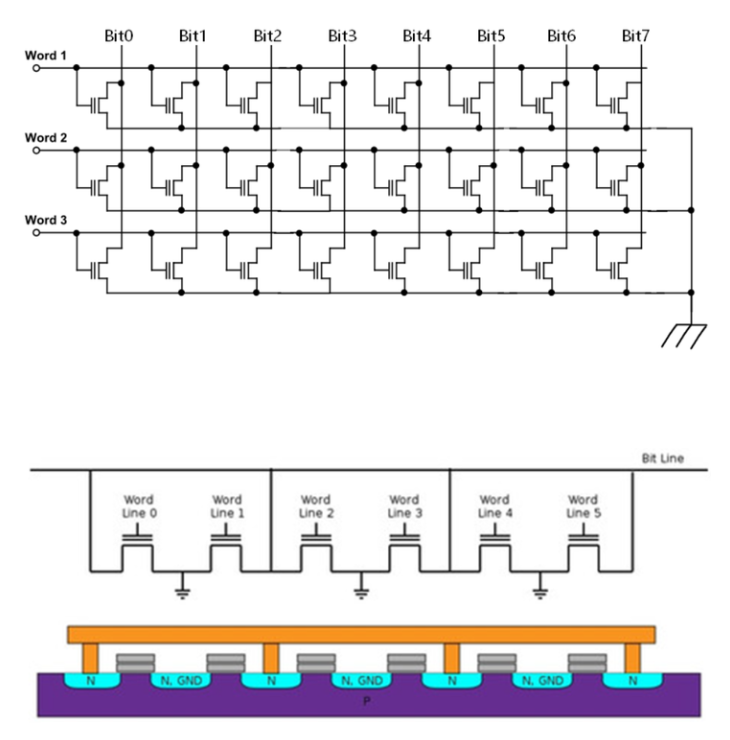

其他的控制總線想要明白必須要先明白SRAM的架構,雖然不用去設計,但是明白SDRAM架構看不懂這個電路圖,來,我們說說

以下是標準4bank的SDRAM內部結構

其寫入原理如下

要存取數據時,先選中一行( wordline加高電位),于是這一行上掛著的所有的行選通NMOS都導通,電容中的數據就沿著bitline進入感應放大器,經其放大后到達列選通NMOS處。接下來,當某根CSL置高后,相應的列選通NMOS就導通,數據沿著bifline繼續向IO接口傳,或者外面的數據立即寫入存儲陣列。當然,具體實現肯定更復雜,但是基本原理就是這樣

那么,這些控制線什么作用呢

LDQM UDQM:數據屏蔽,當LDQM為高,數據線上低8位被屏蔽UDQM高八位被屏蔽,這樣就可以進行bank選擇了(不管內存怎么設計,最終還是八位一個字節,所以需要屏蔽)

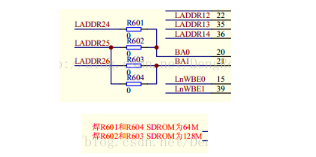

接下來我們看看SDRAM尋址,通過電路可以看到,WBE0 1 2 3分別四根線控制,也就是說,同一個地址,選擇不同的WEB,可以依次讀出0-7 8-15 16-23 24-31四個八位數據,CPU內部自動將這四個數據組合起來,形成一個32位數據,所以,實際上,依次讀寫操作獲得或者寫入數據單純數據上就要四步,另外,地址寫入也分兩步,之前說了,SDRAM尋址分為行和列,所以寫入地址分為寫入行地址,寫入列地址,簡化來看,一共就是6步(沒有說各種控制總線過程,大家有興趣可以研究)

連接的ba0 ba1

首先四字節對其尋址(32位數據線),那么DAT0 DAT1的尋址線肯定是0,所以沒有接上的必要,24 25 26決定最高位,如果為64M r601 r604接上,地址線24-25連接,CPU設置0x30000000為基地址的話,最高地址是0x33FFFFFF,(0x30000000-0x33ffffff) = 0x3ffffff個字節,一共就是64M字節

注意,這中間涉及到一個比較復雜的解碼過程,就是將物理地址解碼成總線地址,(兩個數據),并不是說25 26連接了地址空間就絕對是0X36FFFFFF了,具體過程,請查閱相關資料

-

處理器

+關注

關注

68文章

19409瀏覽量

231206 -

mcu

+關注

關注

146文章

17324瀏覽量

352662 -

SDRAM

+關注

關注

7文章

430瀏覽量

55371 -

存儲器

+關注

關注

38文章

7528瀏覽量

164350 -

nandflash

+關注

關注

0文章

48瀏覽量

20272

發布評論請先 登錄

相關推薦

EE-302:ADSP-BF53x Blackfin處理器與NAND FLASH存儲器的接口

NAND Flash的擦寫次數介紹

NAND Flash和NOR Flash哪個更好

esp32-c3開啟安全啟動和flash加密概率不啟動是什么原因導致的?

貼片式tf卡 Nand flash芯片試用體驗

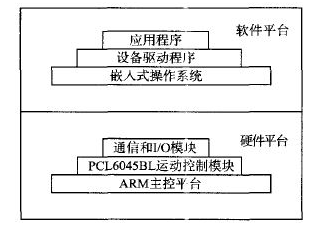

基于S3C2440和專用DSP的嵌入式四軸運動控制器

Flash存儲芯片:NOR Flash、NAND Flash、UFS和eMMC的比較與解析

Flash存儲芯片:NOR Flash、NAND Flash、UFS和eMMC的比較與解析

S3c2440處理器中nor flash啟動和nand flash啟動問題

S3c2440處理器中nor flash啟動和nand flash啟動問題

評論