本系列文章主要針對FPGA初學者編寫,包括FPGA的模塊書寫、基礎語法、狀態機、RAM、UART、SPI、VGA、以及功能驗證等。將每一個知識點作為一個章節進行講解,旨在更快速的提升初學者在FPGA開發方面的能力,每一個章節中都有針對性的代碼書寫以及代碼的講解,可作為讀者參考。

第一章:模塊書寫

Verilog HDL 語言的基本語法與 C語言相似,因此與 VHDL 相比較更容易上手。本章將會在實際小項目的基礎上,以 Verilog HDL 語言為主, 教讀者怎么更方便、更高效的學習 FPGA。

Verilog HDL 中的 HDL 指的是硬件描述語言(Hardware Description Language), 顧名思義,Verilog HDL 可以描述對應的硬件電路,下面以一個小例子說明。

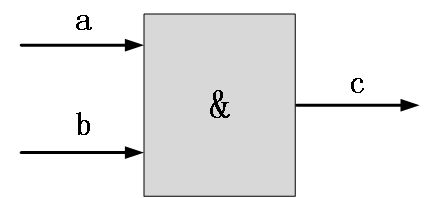

如圖1所示為電路示意圖, 首先分析一下該電路:

①兩個輸入端口即 a 和 b,為了更好地讓讀者理解該變量為一個輸入端口,輸入端口可加上方向pi(port input)表示輸入。面對大量的代碼,一個比較好的命名風格,更方便我們后續的驗證, 希望前期就可以養成比較好的命名風格。

②一個輸出端口即 c,同理 po 即為 port output。

功能:該電路實現 a 和 b 相與,結果為 c。

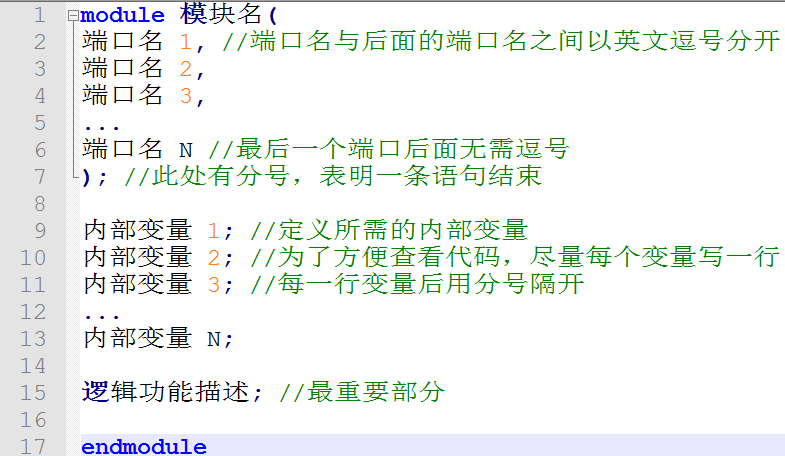

在用 Verilog HDL 描述一個電路時,必須要對該電路命名,此處我們對該電路命名為 a_and_b。在用 Verilog HDL 描述一個電路時, 模塊的開始都是以 module 開始,endmodule 結束, module 后面寫該模塊的模塊名,模塊名的后面有一個小括號,所有該模塊的端口都需要在此小括號內聲明,小括號以分號結束(半角分號,同c 語言一樣, Verilog HDL 中每一條語句也是以分號結束)。

在 module 與 endmodule 之間,可以定義必要的內部變量,以及我們所有描述的邏輯功能。具體如圖2所示:

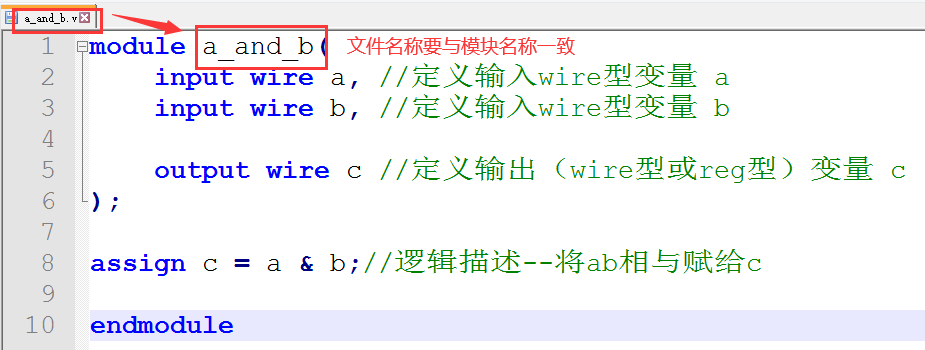

建議安裝專門編輯程序的一些軟件,例如Notepad++軟件界面及功能都比較齊全。用 Notepad++打開我們新建的 V 文件, 按照模板書寫模塊a_and_b的 Verilog HDL 代碼, 如下所示:

代碼解析:

①模塊以 module 作為開頭, endmodule 作為結尾, 需要注意模塊名與 V 文件名要一致;

②小括號內描述端口, Verilog HDL 中輸入端口的關鍵字為 input,輸出端口的關鍵字為 output。wire(線) 為端口的變量類型, input 端口的變量均為 wire型, Verilog HDL 中另一種常用的變量類型為 reg(寄存器),將在后面的章節詳細介紹;

③代碼第 8 行, 描述了具體的邏輯功能, assign 為 Verilog HDL 中的關鍵字,assign 可以描述組合邏輯,每一個 assign 后面只能跟一條語句。Verilog HDL 中另一個常用的關鍵字為 always, 后續會詳細講解。該語句表達的意思為 a&b賦值給 c, 其中=為賦值號, 將右邊的結果賦值為左邊的變量, &為按位與,即變量的對應位相與, 將在基礎語法部分詳細講解。

這樣我們就已經將圖中電路描述清楚了,代碼只需要按照給出的模板填寫對應的內容即可。

第二章節我們將會講解在ISE中如何驗證代碼是否有語法錯誤,以及將對應的代碼轉變成 RTL 電路。

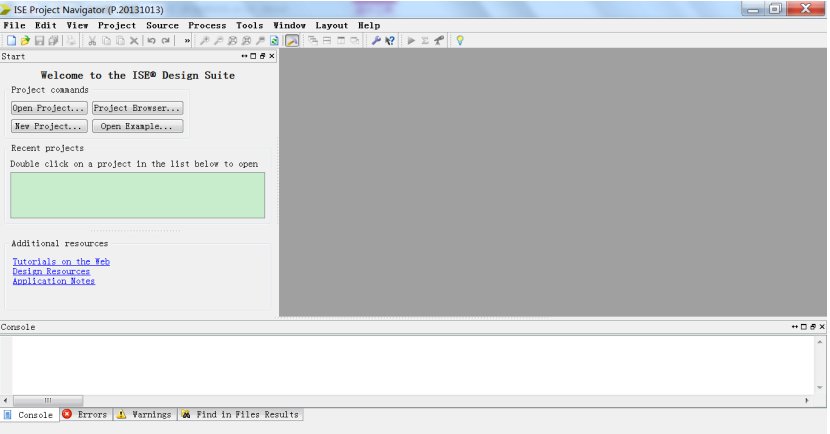

第二章:電路綜合

第一章中已經將 a & b = c 對應的 Verilog HDL 程序寫出, 但是我們無法得知我們所寫的代碼是否有語法錯誤,也不知道代碼是否能夠按照我們的意思生成對應的電路。本章中我們將會使用 xilinx 公司的 ISE 軟件對所寫的程序進行綜合,從中可以得知代碼是否有語法錯誤,以及生成對應的 RTL 電路。為了方便管理,我們在與 design 文件夾同路徑下新建一個文件夾,取名為ise_prj(基于 ISE 的 project)。打開 ISE,會看到如圖 1 所示的界面。點擊右上角的 File,選擇 New Project…新建一個工程。

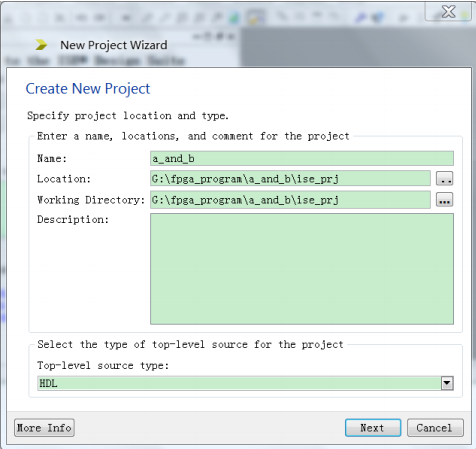

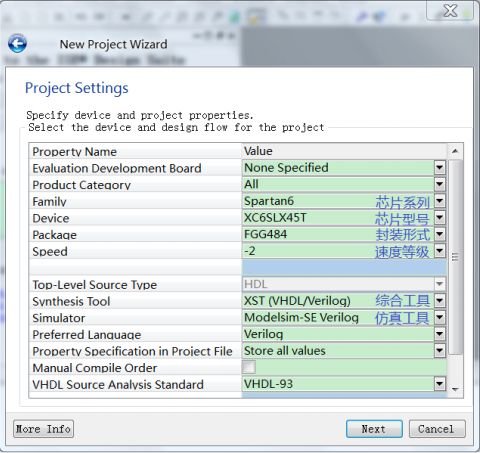

彈出如圖 2 所示的界面,在 Name 處填寫工程名字(盡量保證與頂層文件名一致即a_and_b), Location 處選擇工程存放的路徑, Working Direction 默認路徑與 Location一致, Top-level source type 處按照所需選擇,此處我們選擇 HDL。

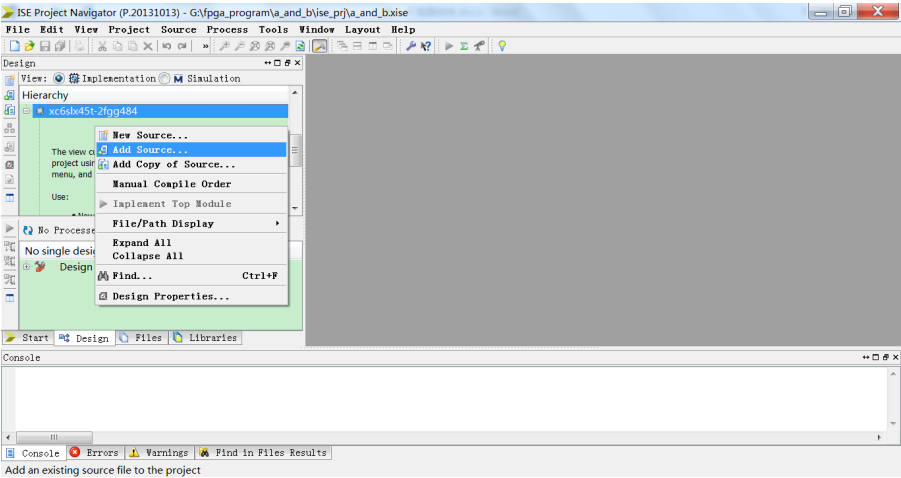

點擊 Next,再點擊 Finish 完成工程的創建。按照圖4所示,右鍵點擊芯片型號,選擇 Add Source…添加已經存在的文件(a_and_b.v)。找到 design 文件夾中a_and_b.v 文件所在的路徑,選中該文件,點擊 OK。

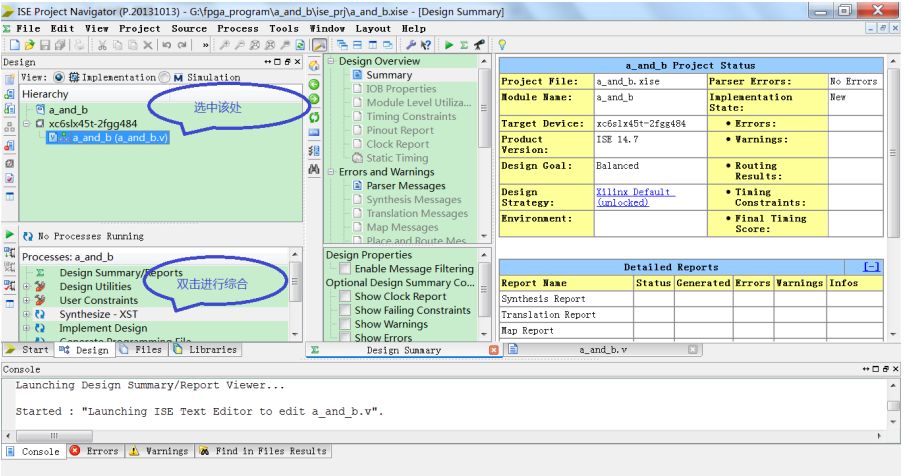

添加文件后的工程界面如圖 5 所示。

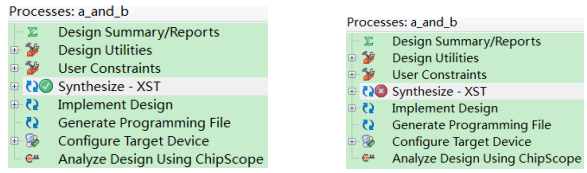

選中 a_and_b,雙擊 Synthesize 選項進行對我們的程序進行綜合。若是沒有語法錯誤則會出現圖6左所示的界面,如果有語法錯誤則會出現圖6右所示的界面,則需要查看錯誤報告將錯誤的地方改正并重新綜合,直至編譯通過為止。

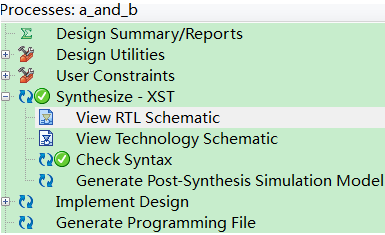

在綜合正確的情況下,點擊 Synthesize 選項前面的加號,如圖 7 所示。

選擇 Start with a schematic of the top-level block,點擊 OK 選項,生成如下圖 9 所示界面。

可以雙擊圖 9 所示的模塊的模型,則可以看到模塊內部的 RTL 電路,如圖 10 所示。

從圖 10 中我們可以看到生成的電路是我們用 Verilog HDL 語言描述的電路結構。代碼的語法及電路驗證都是正確的,但是具體的功能是否滿足我們的要求呢, 這就需要我們通過仿真來驗證了。

在第三章中,我們會針對該代碼書寫對應的測試文件,并且通過 Modelsim 軟件來驗證我們的a_and_b 模塊功能是否正確。

編輯:hfy

-

FPGA

+關注

關注

1630文章

21798瀏覽量

606056 -

Xilinx

+關注

關注

71文章

2171瀏覽量

122150 -

C語言

+關注

關注

180文章

7614瀏覽量

137736 -

硬件電路

+關注

關注

39文章

244瀏覽量

29322 -

VerilogHDL

+關注

關注

2文章

39瀏覽量

19132

發布評論請先 登錄

相關推薦

電子工程師的電路設計經驗分享

基于FPGA的電子琴設計

FPGA初學者系列——模塊書寫&電路綜合

FPGA初學者系列——模塊書寫&電路綜合

評論