作者:Sanjay Churiwala,賽靈思公司工具與方法學(xué)應(yīng)用專家

如果你已經(jīng)有了一個設(shè)計并且想將這個設(shè)計移植到另一款目標(biāo)器件上,這篇文章將幫助你確定這種轉(zhuǎn)換所應(yīng)遵循的步驟。

這篇文章不會涉及與原設(shè)計完全不同的轉(zhuǎn)換方式,從底層組件來看并非完全不同的。

對于這種轉(zhuǎn)換你應(yīng)該遵循特定的轉(zhuǎn)換指南,比如UltraScale系列轉(zhuǎn)換為Versal系列器件,這篇文章的主題就是這種轉(zhuǎn)換的方法,轉(zhuǎn)換的方式通常是相似的。

設(shè)計的RTL部分

底層的RTL結(jié)構(gòu)和Verfilog/VHDL代碼不需要任何更改。

大部分的實例化原語也不需要任何更改,Vivado工具將會用等效的實例化原語來進行替換來滿足目標(biāo)設(shè)計的需要。

可能有一些特定的原語不能進行替換,這可能與最初組件的選擇和目標(biāo)設(shè)計的結(jié)合有一定關(guān)系。對于這種情況,你就需要手動找到最接近的等效功能從而替換之前的原語模塊。

對RTL源碼進行一次綜合操作,不用擔(dān)心時序約束的正確性,甚至不用去考慮是否是最優(yōu)的綜合。

然后仔細查看綜合操作的日志文件,如果你看到某些與無法綜合的原語相關(guān)的信息,那么這些原語就需要你親自來替換了。

還要注意那些關(guān)鍵的警告,如果某些原語被重新設(shè)計了,但是功能就可能得不到保證。

使用綜合操作的日志文件來確定可能需要修改是一種比較快速的方法,而不用遍歷所有的RTL源碼。

設(shè)計的IP部分

如果你的設(shè)計采用了IP模塊,首先你需要檢查來確定相同的IP在新的芯片上是否還能夠使用。

大部分軟核IP在新的目標(biāo)器件上都應(yīng)該能夠使用,然而硬核IP有可能就不適用了,當(dāng)然這與選擇的器件有關(guān)。

你想做的第一件事就是“升級”你的IP組件。

檢查IP說明文檔或者IP升級日志,這些文件包含更改了哪些參數(shù)、管腳輸出等詳細信息,IP升級日志可以在你的工程目錄下找到。

對于采用的所有IP,你要快速檢查可以自定義的參數(shù),通常IP的自定義配置可以保留不變,然而在新的設(shè)計結(jié)構(gòu)中可能還需要一些額外的參數(shù)設(shè)置,當(dāng)然一些參數(shù)可能不再適用了,你希望看到的是采用當(dāng)前的參數(shù)設(shè)置每個IP的功能都能正常工作。

同樣的輸入管腳配置也需要修改,如果有必要的話你需要檢查管腳輸出,更改實例化IP組件的管腳連接。

然后“生成輸入文件”——面向新的器件

即使在修改不同組件之前已經(jīng)執(zhí)行了“生成輸入文件”操作,那些輸入文件可能不再有意義,因此需要重新生成。

設(shè)計的IPI/BD部分

整個設(shè)計的IPI/BD部分與IP部分應(yīng)該非常的相似。

首先要檢查一下在BD中使用的IP模塊在目標(biāo)器件上是否可用。

對于設(shè)計的BD部分,執(zhí)行“報告IP狀態(tài)”操作,升級建議的IP模塊。一般來說它會將以對BD中使用的所有IP進行升級。

查看IP升級日志文件,其中包括需要更改哪些參數(shù)、輸入管腳等詳細信息,IP升級日志可以在工程目錄下找到。

檢查每個IP的參數(shù),可能會增加一些新的參數(shù),一些之前版本的參數(shù)可能棄用了,同樣的管腳輸出也需要修改。

如果管腳輸出被更改了,你應(yīng)該能夠借助自動化連接操作來找回丟失的連接。

一旦BD部分為新的設(shè)計準備好了,那么就可以執(zhí)行“驗證BD”操作了,驗證成功后執(zhí)行“生成輸入文件”操作即可。

檢查BD級的管腳輸出是否仍然保持不變,否則就需要重新實例化BD模塊并且更新BD模塊的管腳連接。

I/O管腳規(guī)劃和布局(Planning)

如果有需要還要根據(jù)新的目標(biāo)器件的管腳輸出重新執(zhí)行I/O布局操作。

實現(xiàn)步驟

一旦IP(包括工程目錄下的和BD目錄下的)都進行了更新,那么整個設(shè)計還需要重新執(zhí)行編譯操作,包括綜合(synthesis)和實現(xiàn)(implementation)等操作。

在驗證過程中還需要對實現(xiàn)策略、執(zhí)行順序、管腳規(guī)劃布局以及LOC約束進行仔細的檢查。

最后感謝來自CortexRF公司的格倫·英格利希(Glen English)對本篇文章的建議,確認了設(shè)計轉(zhuǎn)換器件過程中要注意的事項和操作步驟,從而保證整個設(shè)計的正常工作。

編輯:hfy

-

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

8745瀏覽量

148056 -

vhdl

+關(guān)注

關(guān)注

30文章

817瀏覽量

128343 -

RTL

+關(guān)注

關(guān)注

1文章

385瀏覽量

59952

發(fā)布評論請先 登錄

相關(guān)推薦

詳解Object Detection Demo的移植

智能語音識別照明解決方案,平臺自定義,中英切換

采用物聯(lián)網(wǎng)能源效率解決方案實現(xiàn)凈零排放目標(biāo)

通過外部多路選擇開關(guān)來動態(tài)切換不同采樣目標(biāo)時,ADS125H02的內(nèi)部數(shù)字濾波器是否會導(dǎo)致采樣的結(jié)果會相互影響?

AIGC系統(tǒng)中多個模型的切換調(diào)用方案探索

多平臺FPGA工程快速移植與構(gòu)建

kvm切換器怎么實現(xiàn)鍵盤熱鍵切換

在KeyStone器件實現(xiàn)IEEE1588時鐘方案

基于機智云移植STM32L496G代碼移植

電源切換開關(guān)芯片怎么接

電源切換芯片怎么設(shè)置

羅姆GaN器件被臺達電子采用

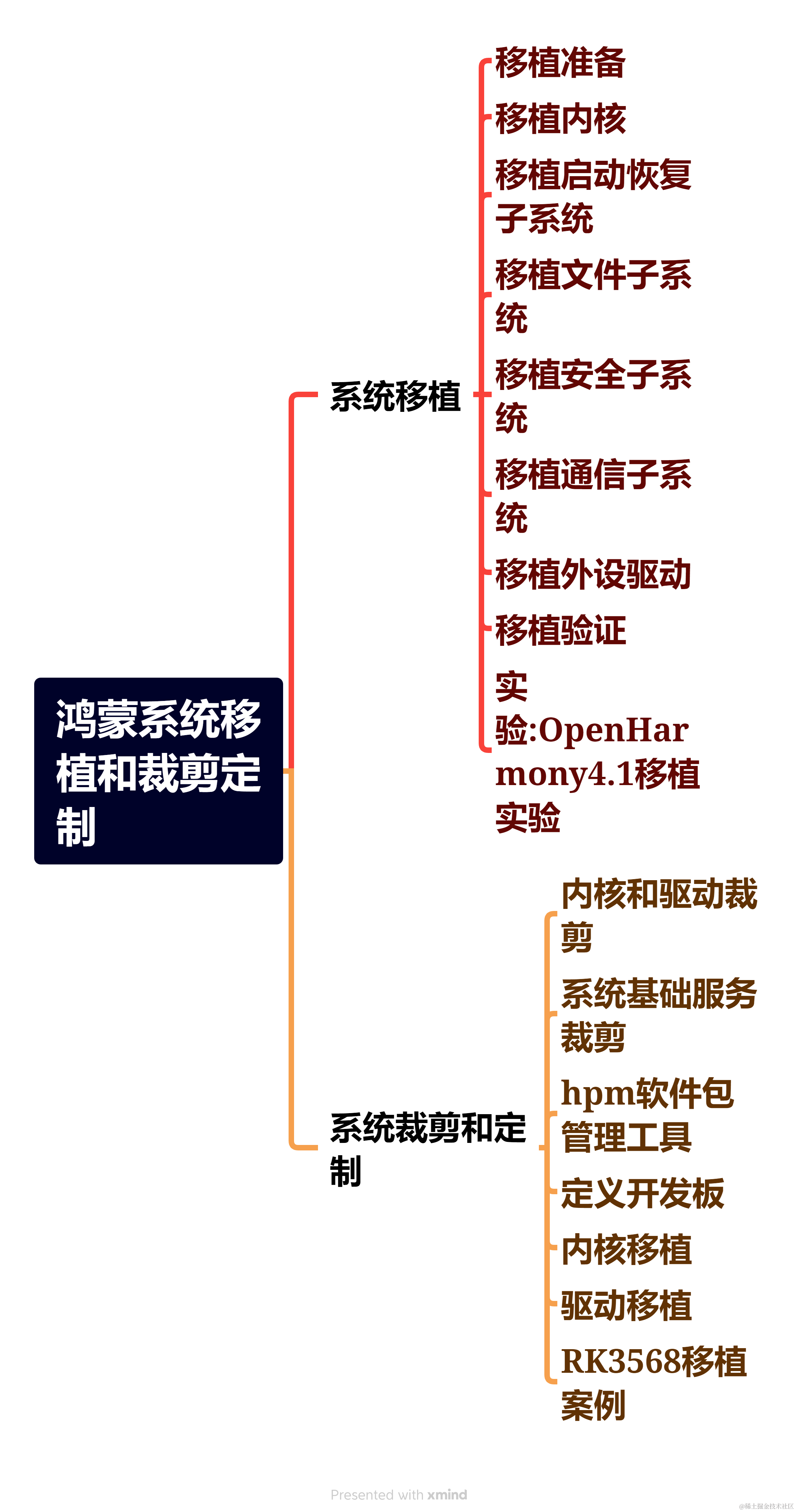

【鴻蒙】標(biāo)準系統(tǒng)移植指南

設(shè)計采用目標(biāo)器件的移植切換方案

設(shè)計采用目標(biāo)器件的移植切換方案

評論