仿真功能概述

仿真FPGA開發中常用的功能,通過給設計注入激勵和觀察輸出結果,驗證設計的功能性。Vivado設計套件支持如下仿真工具:Vivado Simulator、Questa、ModelSim、IES、VCS、Rivera-PRO和Active-HDl。

Vivado的仿真流程如下圖所示:

仿真可以在設計階段的不同時間點進行,主要包括如下三個階段:

RTL級行為仿真:在綜合和實現前便可驗證設計,用來檢查代碼語法和驗證代碼像設計者想要的功能一樣工作,早期的行為級仿真可以盡早發現問題;

綜合后仿真:使用綜合網表仿真,驗證綜合后設計滿足功能需求。該階段仿真不太常用,可以用時序仿真(timing simulation)來估計時間;功能仿真(functional sumulation)由層次化的網表組成,最底層由Xilinx原語構成;

實現后仿真:可以進行功能仿真和時序仿真,且與FPGA硬件上的工作情況最為接近,確保實現后設計滿足功能和時序要求。

時序仿真相比功能仿真要耗費大量的時間,但是可以檢測到功能仿真無法檢測的問題,比如:

由于屬性設置(綜合屬性、UNISIM庫屬性等),或不同仿真器對語法的不同解釋,導致綜合后或實現后功能發生改變;

雙口RAM讀寫沖突;

錯誤的、不合適的時序約束;

異步路徑操作問題;

由于優化技術引起的功能問題

Vivado Simulator支持VHDL(IEEE-STD-1076-1993)、Verilog(IEEE-STD-1364-2001)、SystemVerilog中的可綜合子集(IEEE-STD-1800-2009)三種硬件描述語言,此外還支持IEEE P1735加密標準。

使用TestBench和激勵文件

TestBench也是由HDL語言代碼編寫,其實例化了需要仿真的設計,生成設計所需要的激勵信號,監測設計輸出結果并檢查功能的正確性。一個簡單的TestBench可以僅僅將激勵順序地加載到設計的輸入管腳上;一個復雜的TestBench可能會包含子程序調用、從外部文件讀取激勵信號、條件化激勵和其它更多復雜的結構。

下面是編寫TestBench時極度推薦的一些注意事項:

在Verilog TestBench中總是使用timescale規定時間,如`timescale 1ns/1ps;

在仿真時間的0時刻,將所有的設計輸入初始化位為一個確定的值;

在綜合后和實現后的時序仿真中,會自動觸發全局置位/復位脈沖(GSR),這會讓所有的寄存器在仿真的前100ns內鎖定其值。因此在100ns之后再賦值激勵數據;

在全局置位、復位脈沖釋放之前就確保時鐘源已經開始工作。

指定仿真器位置

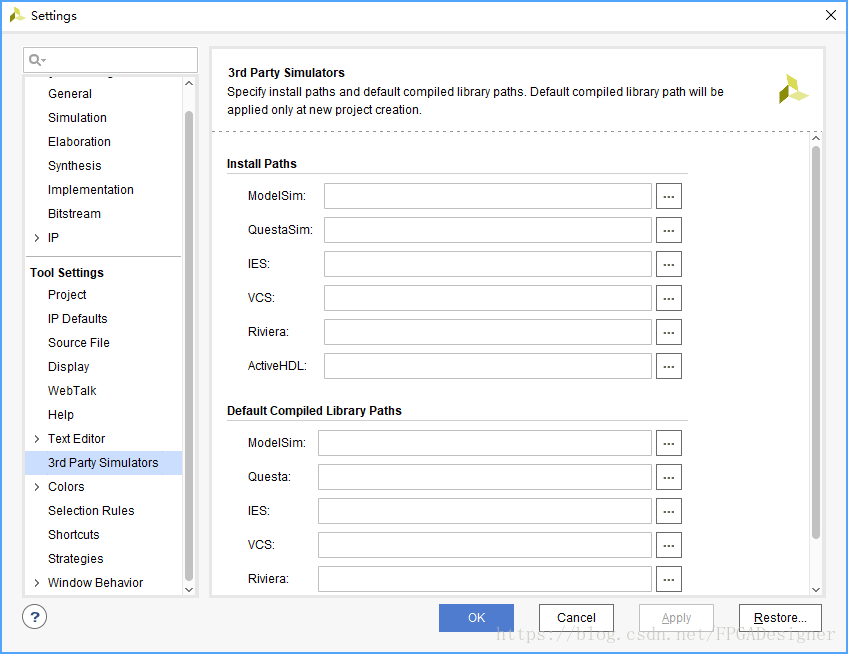

點擊Tools->Settings->Tool Settings->3rd Party Simulators:

Install Paths中定位仿真器的安裝路徑,Default Compiled Library Paths中指定與仿真器相關的編譯庫路徑。只有第三方仿真器需要在此設置,Vivado Simulator不需要設置。

編譯仿真庫

使用Vivado Simulator時,不需要編譯仿真庫。但是使用第三方仿真工具時,必須先編譯仿真庫,才能在第三方仿真工具中正確運行。仿真庫中包含了仿真模型,比如FPGA和IP的行為模型和時序模型。編譯之后的庫可以在多個設計工程中使用。

在編譯過程中,Vivado會創建一個仿真器用來參考編譯庫文件的初始化文件,該文件包含了一些控制變量,包括規定參考庫路徑、優化、編譯和仿真設置。如果沒有正確的初始化文件,就不能運行包含Xilinx原語的仿真。不同仿真器的初始化文件名稱如下:

Questa/ModelSim:modelsim.ini;

IES:cds.lib;

VCS:synopsys_sim.setup

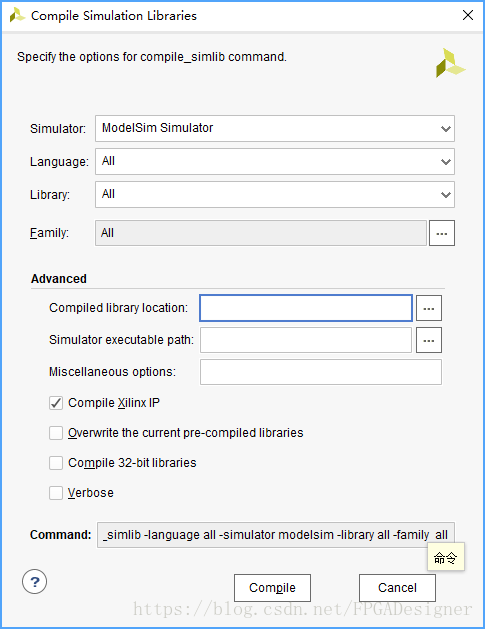

如果使用的仿真器版本不變,只需要編譯一次庫文件即可;如果更換了Vivado或仿真器的版本,就必須重新編譯一次庫文件。編譯庫文件有Vivado IDE和Tcl命令兩種方法,本文介紹第一種。點擊Tools->Compile Simulation Libraries(即使不打開工程也有此命令)打開如下窗口:

Simulator:選擇第三方仿真器;

Language:編譯庫到規定的語言,如果為All,則會根據選擇的仿真器自動選擇語言,如果仿真器支持混合語言仿真,則Verilog庫和VHDL庫都會編譯;

Library:選擇需要編譯的仿真庫(Unisim或Simprim),默認會編譯所有 的庫;

Family:編譯庫到規定的FPGA系列,默認會生成所有的器件系列;

Compiled library location:設置保存編譯庫結果的目錄路徑。默認情況下會保存在當前工程目錄的.cache/compile_simlib目錄下;

Simulator executable path:設置仿真器可執行文件所在的路徑;

Miscellaneous Options:使用Tcl命令設置一些其它選項;

Compile Xilinx IP:選擇是否編譯Xilinx IP的仿真庫;

Overwrite current pre-compiled libraries:選擇是否重寫當前預編譯庫;

Compile 32-bit libraries:默認為64bit模式,選中此項,仿真器編譯會在32bit模式下進行;

Verbose:Messages窗口默認有消息顯示數量限制,選中此選項后,相關命令會忽視此限制,所有消息都會顯示在Messages窗口中;

Command:展示了上述設置所等效的Tcl命令。

Xilinx仿真庫

設計者可以將Xilinx仿真庫用于任何支持VHDL-93和Verilog-2001語言標準的仿真器。庫中包含延遲與模型信息,可以正確地仿真Xilinx硬件器件。

仿真時,如果數據和時鐘同時發生變化,仿真器在判斷當前時鐘邊緣時會采樣上一個狀態的輸入,同時變換時刻的輸入會安排在下一個始終邊緣才有效。最好的做法當然是不要使數據信號和時鐘信號同時變換,以避免出現意料之外的仿真結果。

當設計者在設計中實例化了一個組件后,仿真器必須在庫中找到描述該組件功能的內容,以確保正確的仿真。下面列出Xilinx提供的仿真庫:

UNISIM:Xilinx原語的功能仿真,Verilog庫名為UNISIMS_VER。包含了器件原語和最低等級構建模塊的描述。

UNIMACRO:Xilinx宏的功能仿真,Verilog庫名為UNIMACRO_VER。當使用器件宏時,必須設置此庫。

UNIFAST:快速仿真庫,Verilog庫名為UNIFAST_VER。推薦在RTL行為級仿真中使用此庫,可以節省仿真運行時間。

SIMPRIMS_VER:Xilinx原語的時序仿真,僅支持Verilog,因此時序仿真僅支持Verilog語言。

SECUREIP:Xilinx復雜器件組件(如PCIE、高速收發器)的功能仿真和時序仿真庫,在Vivado安裝目錄的data/secureip目錄下可以查看完整IP列表。

XPM:Xilinx原語的功能仿真。

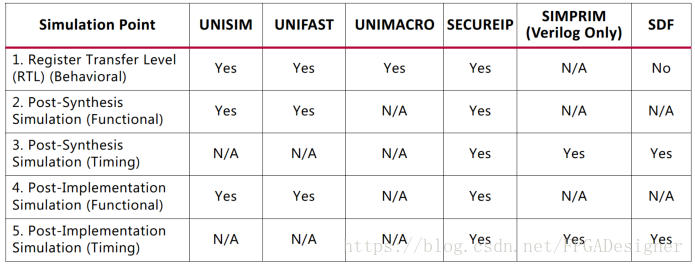

除了SECUREIP外,其它庫都位于Vivado安裝目錄data/Verilog或VHDL/src目錄內。設計者必須根據運行的仿真來設定不同的仿真庫。下表中給出了與不同仿真階段相關的仿真庫文件:

仿真設置

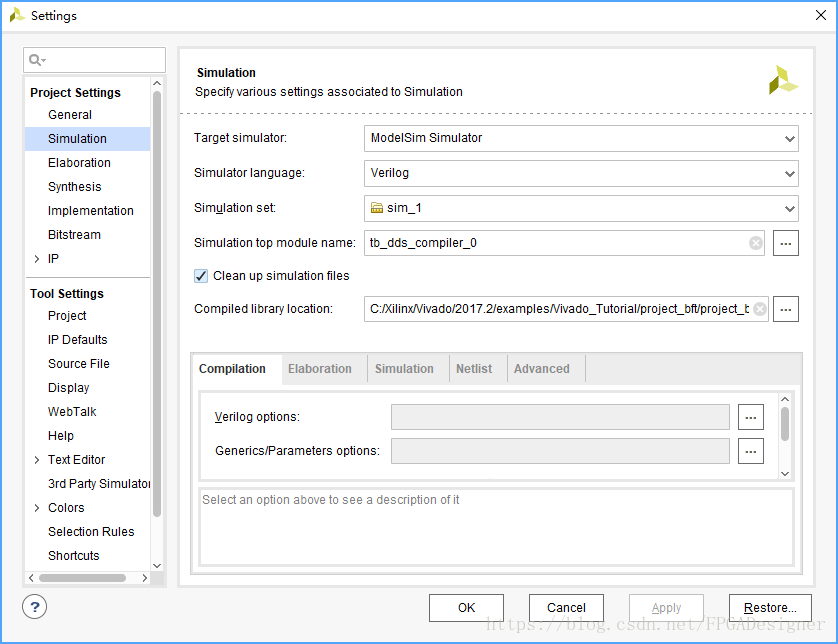

在仿真設置中規定目標仿真器、仿真集、仿真頂層模塊名稱等選項。打開Settings切換到Simulation標簽中,或在Flow Navigator中的Simulation上右鍵->Simulation Settings,打開設置窗口:

其中Clean up simulation files表示重新運行仿真時會將現存的整個仿真目錄全部移除,其余設置選項很熟悉了,不多作介紹。下面著重介紹Simulator language,理解背后的處理機制,其值可選擇VHDL、Verilog或Mixed。

大多數的Xilinx IP只會生成單語言的行為仿真模型;某些第三方仿真工具也僅支持單語言仿真。通常應該將Simulator language設置為仿真工具支持的語言,以確保工具正常運行。如果IP核同時也可以生成該語言的行為模型再好不過,但是如果IP核不支持該設置,Vivado會自動從IP核的DCP文件中生成一個結構化仿真模型用于仿真,確保仿真可以正常運行。

仿真分辨率需要在TestBench中使用timescale設置,某些人認為設置一個粗略的仿真分辨率(如1s)可以提升仿真性能,這是錯誤的。在 Xilinx仿真模型中,大多數仿真時間是基于一個固定間隔,與仿真分辨率并無聯系。設置仿真分辨率主要是為了觀察更方便。但是某些Xilinx原語組件(如MMCM)需要1ps的分辨率才能在仿真中正常工作,最常用的分辨率設置是`timescale 1ns/1ps。

仿真集功能

Vivado提供了仿真集(Simulation Sets)功能,該機制可以讓用戶將不同設計階段所用到的不同源文件添加到各自的仿真集中。比如一個仿真集可以添加用于RTL行為級仿真的源文件,另一個仿真集添加用于實現后時序仿真的源文件。或者不同的仿真集提供對一個設計的不同測試方法,等等。

在創建或添加仿真源文件時,可以選擇將文件加入到哪個仿真集,或者創建新的仿真集:

當設計中存在多個仿真集時,當前運行使用的仿真集會顯示為Active狀態:

編輯:hfy

-

vhdl

+關注

關注

30文章

817瀏覽量

128344 -

Vivado

+關注

關注

19文章

815瀏覽量

66892

發布評論請先 登錄

相關推薦

Vivado Design Suite用戶指南: 設計分析與收斂技巧

Vivado Design Suite用戶指南:邏輯仿真

Verilog 測試平臺設計方法 Verilog FPGA開發指南

正點原子fpga開發指南

FPGA設計中 Verilog HDL實現基本的圖像濾波處理仿真

深入探索Vivado非工程模式FPGA設計流程

FPGA開發Vivado的仿真設計案例分析

FPGA開發Vivado的仿真設計案例分析

評論