光子學的目標是利用光來實現通信、數據傳輸、信息處理等傳統電子設備所實現的功能。光子學成為一個實踐性的工作方向始于1960 年激光器的發明。光纖傳輸信息的發明推動了光子技術在電訊行業的廣泛應用。與此同時,光子技術還出現更加廣闊的各類技術應用領域,包括醫學診斷、生物和化學檢測、生產制造等。然而,制造光子器件的成本嚴重制約了它們的商業化。

多年來,硅晶圓代工廠已成功生產大批量的硅晶圓。如此大批量的生產降低了成本,使硅基電子集成電路 (IC) 不僅經濟實惠而且有利可圖。與此同時,芯片版圖設計規則和工藝開發套件 (PDK) 的開發促進了整個行業內的 IC 設計及驗證的標準化和優化,幫助設計公司切實可行并有利可圖的開發出現今市場中種類繁多的 IC 和知識產權 (IP)。

事實證明,被氧化硅包裹的硅可作為一種近乎理想的波導材料,這意味著光信號在這種材料中傳播時幾乎不會發生衰減,而這正是硅光子設計有廣闊市場前景的關鍵因素之一。在過去十年里,我們固然取得了許多成功,但硅光芯片 (PIC) 為何沒能得到更廣泛的采用呢?憑借其諸多優勢(傳輸速度、低功耗、經驗證的成熟工藝等),加以硅晶圓生產的成本效益,為什么還沒有占領市場呢?

答案并不復雜,通過硅晶圓代工廠實現的產品及市場規模化,建立并定制了一系列的晶體管設計技術規范。其中一部分只是慣性使然。晶圓代工廠在 IC 的摩爾定律模型方面積累了豐富的經驗和成功案例。雖然當今的 7 納米工藝與 20 到 30 年前的 0.5 微米工藝有著天壤之別,但這些改進和進步是隨著時間的推移,伴隨每種新工藝逐步實現的。對現有的機制和工藝略加修改,比從零開始新起爐灶總是要輕松一些,成本也更低。

然而,摩爾定律的發展如今也舉步維艱。是的,我們可以肯定地說會出現 3 nm 工藝,但它已經不會像以前的工藝節點提升那樣帶來巨大的性能或面積優勢,而且注定會被貼上昂貴的標價。這也意味著市場中出現了拐點機會。但除了這一機會以外,PIC 要想成功達到媲美IC 的規模,還需要些什么呢?

答案之一有賴于 IC 所實現的標準化和優化。我們需要復制作為無晶圓廠的設計開發模式,使其為光子學領域所用。當然,這說起來容易做起來難。但是,我們可以從深入研究該模式及歷史開始,了解需要投入的工作。

我們來想一想,無晶圓廠 IC 團隊在設計片上系統 (SOC) 時會從晶圓代工廠獲得哪些東西。首先是 PDK。PDK 實質上代表了一份隱式合同,即合理運用適當的電子設計自動化 (EDA) 軟件工具將能夠實現目標工藝中可制造和可操作的設計。PDK 的核心是設計規則,它們定義了物理版圖的制造要求。設計規則檢查 (DRC) 確保在版圖中創建的幾何形狀可以在給定的代工廠工藝節點上成功制造。為了配合設計規則,晶圓代工廠還必須公開 GDS 或 OASIS 文件中的層分別用于哪個工藝步驟及制造相應的掩膜版。

PDK 中還有一個重要部分是器件模型。晶圓代工廠是晶體管領域的專家。他們會細致、準確地描述晶體管在給定結構中的工作情況。只要設計人員正確地構建晶體管,他們就可以放心,器件會按設計預期的那樣運行工作。

但是,僅有器件模型還不足以實現規模化。如果設計人員不得不把注意力放在確保版圖中的每個晶體管都正確設計,那么要設計出我們當前創建的包含數十億個晶體管的 SoC,將會是一項曠日持久的工程。

為實現規模化,PDK 中加入了更多信息。首先是預先特征化的單元 (Pcell)。Pcell 允許設計人員在一組已知和允許的參數中進行選擇,這些參數可在一定范圍內修改,以使一個晶體管或一組晶體管表現出不同的電子行為。更重要的是,這些參數可通過電路原理圖形式的預定義和特征化設計來驅動。這種原理圖驅動的設計方法使設計人員可以專注于設計需求而不是物理版圖,從而大幅提高了開發效率。為了進一步簡化流程,PDK 還提供了參數化的原理圖符號,設計人員可使用這些符號來確保原理圖中搭建的模塊可以準確無誤的代表設計意圖。

當然,這仍然不夠。晶圓代工廠還進一步提供了定制好的標準單元庫。這些庫包括常用的邏輯單元和其他相對簡單的基礎模塊。晶圓代工廠還提供更大的 IP 模塊和(或)來自第三方供應商的經過定制及驗證的模塊 IP,例如存儲器、處理器等。從理論上講,SoC 設計人員可以根據自己的喜好組合其中的任意或全部模塊,而不必擔心它們的行為和性能。

但即使要做到這一點也不輕松。我們如何得知將這些模塊組合到一起后的性能如何?數字設計流程正是從這里真正蓬勃發展起來的。附帶時序庫的標準單元和 IP 讓設計人員可以了解在版圖中將它們組合到一起后的行為。這些時序庫沒有提供詳細分析,而是提供各種工藝極限下的相關信息,指示組件在特定工作條件下的行為。通過添加一些參數(通常以 LEF 庫和 tech 文件的形式),這些庫可用于指導一種既可驗證時序,又可通過布局和布線 (P&R) 工具來驅動版圖的設計流程。

然而,即便這些全部到位,IC 設計流程也遠非按個按鈕那么簡單,人們依然很可能而且相對容易犯錯誤,從而造成良率或可靠性問題。盡管如此,在大致了解他們的成功史后,您應該可以明白,設計人員為何不愿放棄所有這些設計模式和安全保障了。

這對硅光子意味著什么呢?這意味著,開發類似的工具和組件對于將 PIC 整合成傳統的 IC 設計及驗證流程至關重要,首先要開發一個光子 PDK。

實際上,盡管面臨挑戰,但在實現這一目標方面仍取得了可喜的進展。雖然 GDS 和 OASIS 文件格式本身并不支持 PIC 中常見的曲線結構,而且對這些曲線結構進行傳統的 DRC 驗證會導致成千上萬的誤報,但我們已成功找到一些方法,利用專用的 DRC 來檢查 PIC 版圖中存在的實際問題,同時避免產生大量誤報。

盡管我們尚未實現真正統一的包含定制化單元的完整 Pcell 光子器件庫,但也只有一步之遙了。通過使用基于 Python? 的 Pcell (Pycells),或使用 PhoeniX OptoDesigner 設計平臺或Luceda IPKISS.eda 設計框架 [1][2][3] 等工具,可以獲得創建此類 Pcell 的能力。Calibre?nmLVS?電路驗證可以執行簡單的器件級黑盒式版圖與原理圖 (LVS) 驗證,以確保生成的版圖中不存在短路或開路,并將從版圖中提取的光學設計傳遞給光學仿真器,例如 Lumerical 的 Interconnect設計工具 [4][5]。Mentor 已經發布了 Tanner L-Edit 工具的增強功能,可對集成光子設計進行手動版圖布局。更進一步的,Mentor 還提供了業界首個集成的電子/光子混合版圖自動化工具。自動化工具完成的版圖設計將是“通過 Calibre 驗證的設計”,并可融入 OpenAccess 設計流程。這些工具和流程共同代表了一項重大進步,可幫助光子學設計人員將注意力從關注器件構成差異化轉向基于已知和定制化器件的設計開發上。

EDA 行業認識到仍有很多有待逾越的障礙。我們的晶圓代工廠合作伙伴是晶體管專家,但遠遠還沒有成為光學專家。我們可以助您一臂之力!基于生產制造后的測量可以創建適當的工藝模型,借助這些模型,我們可以預知版圖中繪制的 PIC 設計將如何在制造步驟中呈現。我們可以自動捕獲版圖設計中的圖形與實際制造出的圖形之間的差異。通過這種方式,晶圓代工廠或設計團隊可以基于多個可能的物理參數生成幾種不同的版圖設計來表征一個器件,再通過實際的測量來確定這些差異將如何影響光學行為。遵循這樣的表征過程,可以更好地了解不同物理參數間多種組合形式的可行性,并最終制作出適用于 PIC 設計的經過認證可以確保質量的 Pcell。

晶體管的電子行為主要由寬度和間距來表征,光學器件則不然,在沒有進行充分仿真的情況下,要基于版圖甚至硅圖像來驗證光學器件的預期電子行為要困難得多。幸運的是,這可能不是必需的。LVS 器件驗證背后的理念是確保版圖充分體現原理圖中的設計意圖。一種替代方法是,在相關的版圖設計中重現相應的版圖設計。如果未發現更改,則設計人員知道布局的器件與預期器件匹配。從復雜的圖形匹配到直接根據光學方程式重新生成圖形,有多種方法可用于進行這樣的比較。

還有最后一個需要考慮的問題 — 如何成功地將光子和電子器件整合在一起。理想情況下,設計人員會將所需的電子和光子器件擺放在同一芯片上。但是,與電子器件相比,光子器件通常要大得多,所以光子器件設計不需要使用更先進的工藝節點。如果設計人員需要只能借助先進工藝實現的電子功能來驅動光子器件,那么最終這些光子器件將會占用大量非常昂貴的面積,導致最終的 SOC 價格令人難以承受。事實上,鑒于光子器件的尺寸很大,試圖將它們與電子器件整合在一個芯片上會直接導致芯片的尺寸增大,進一步增加成本。

顯而易見的解決方案是采用多芯片封裝,在這方面有很多積極的消息。晶圓代工廠、外包裝配與測試 (OSAT) 公司以開發類似 PDK 的方法來簡化和降低封裝設計和驗證的風險方面,也取得了長足的進展。實際上,領先的硅光子生產代工廠 TowerJazz 近期發布了基于業界領先

的 Calibre nmPlatform 的初版硅光子 PDK。在 Calibre nmPlatform 的支持下,采用 TowerJazz PH18硅光子工藝的客戶現在能夠像構建互補式金屬氧化物半導體 (CMOS) 器件那樣,一如既往地放心構建物理結構正確的硅光子器件 [6]。

硅光子具有高速數據傳輸、高帶寬以及低功耗的前景優勢,這對于當今的高性能計算、電信、軍事、國防、航空航天、醫療和研究應用而言至關重要。但要實現這一前景,設計公司必須獲得晶圓代工廠和 EDA 供應商為 IC 設計和驗證提供的同等水平的支持。幸運的是,預后良好!業界正在積極地聯合晶圓代工廠、設計人員、EDA 供應商和封測廠,致力于延續并擴大迄今為止已取得的進展,終極目標是實現硅光子技術產品化所需的實惠且規模化的設計開發平臺。

編輯:hfy

-

集成電路

+關注

關注

5392文章

11624瀏覽量

363201 -

eda

+關注

關注

71文章

2788瀏覽量

173881 -

晶圓代工

+關注

關注

6文章

861瀏覽量

48655 -

光子器件

+關注

關注

0文章

31瀏覽量

11963 -

硅光子

+關注

關注

6文章

88瀏覽量

14904

發布評論請先 登錄

相關推薦

臺灣精銳APEX減速機在半導體制造設備中的應用案例

半導體制造里的ALD工藝:比“精”更“精”!

無塵車間半導體制造設備的振動標準

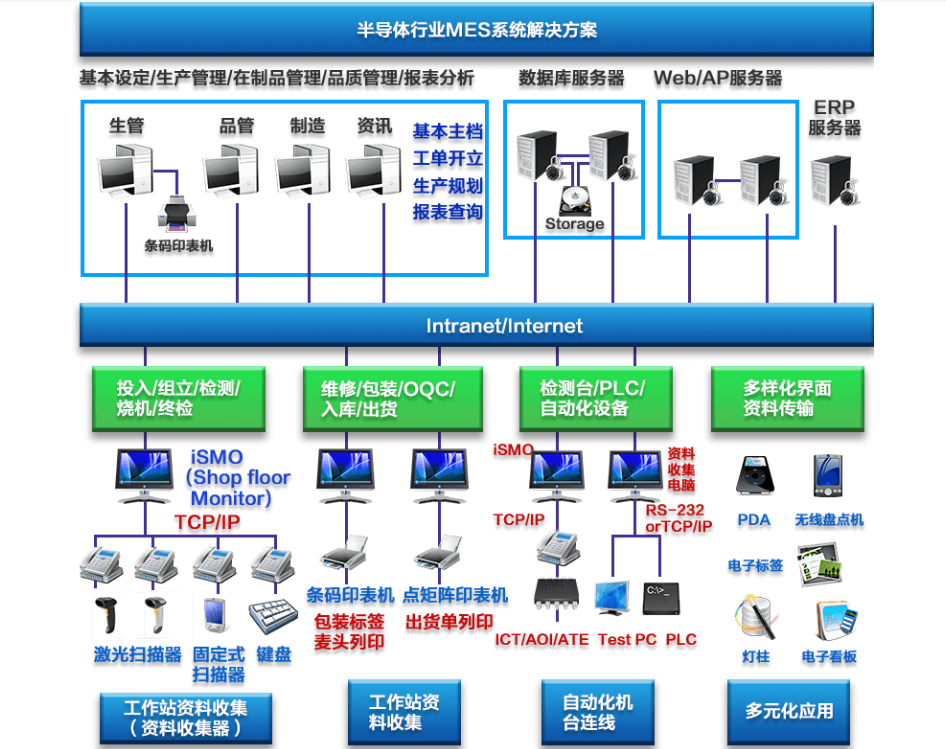

半導體制造行業MES系統解決方案

ESD靜電對半導體制造的影響

半導體制造設備革新:機床需求全面剖析

半導體制造設備對機床的苛刻要求與未來展望

全球半導體制造業邁向新高:SEMI預測未來兩年產能大幅提升

半導體制造商必須適應不斷變化的格局

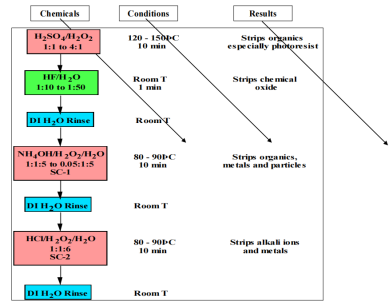

硅晶片清洗:半導體制造過程中的一個基本和關鍵步驟

硅光子在半導體制造技術的未來前景

硅光子在半導體制造技術的未來前景

評論