在高速PCB設計的學習中,有很多的知識點需要大家去了解和掌握,比如常見的信號完整性、反射、串擾、電源噪聲、濾波等。本文就和大家分享10個和高速PCB設計相關的重要知識,希望對大家的學習有所幫助。

信號完整性

信號完整性(英語:Signal integrity,SI)是指信號在傳輸路徑上的質量,傳輸路徑可以是普通的金屬線,可以是光學器件,也可以是其他媒質。

在短距離、低比特率的情況里,一個簡單的導體可以忠實地傳輸信號。

而長距離、高比特率的信號如果通過幾種不同的導體,多種效應可以降低信號的可信度,這樣系統或設備不能正常工作。

隨著集成電路輸出開關速度提高以及PCB板密度增加,信號完整性已經成為高速數字PCB設計必須關心的問題之一。

元器件和PCB板的參數、元器件在PCB板上的布局、高速信號的布線等因素,都會引起信號完整性問題,導致系統工作不穩定,甚至完全不工作。

信號完整性需要考慮的問題主要有振鈴(ringing)、串擾(crosstalk)、接地反彈、扭曲(skew)、信號損失和電源供應中的噪音。

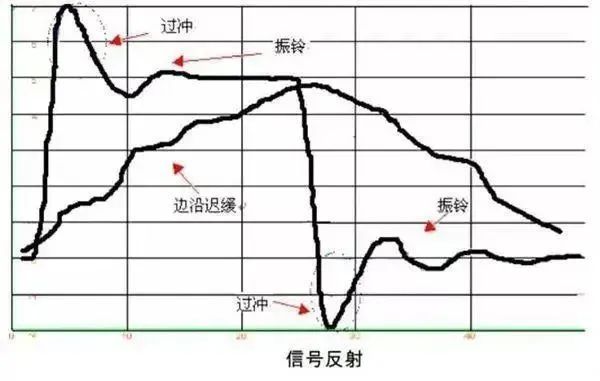

反射

反射就是在傳輸線上的回波。信號功率(電壓和電流)的一部分傳輸到線上并達到負載處,但是有一部分被反射了。

如果源端與負載端具有相同的阻抗,反射就不會發生了。源端與負載端阻抗不匹配會引起線上反射,負載將一部分電壓反射回源端。

如果負載阻抗小于源阻抗,反射電壓為負,反之,如果負載阻抗大于源阻抗,反射電壓為正。

布線的幾何形狀、不正確的線端接、經過連接器的傳輸及電源平面的不連續等因素的變化均會導致此類反射。

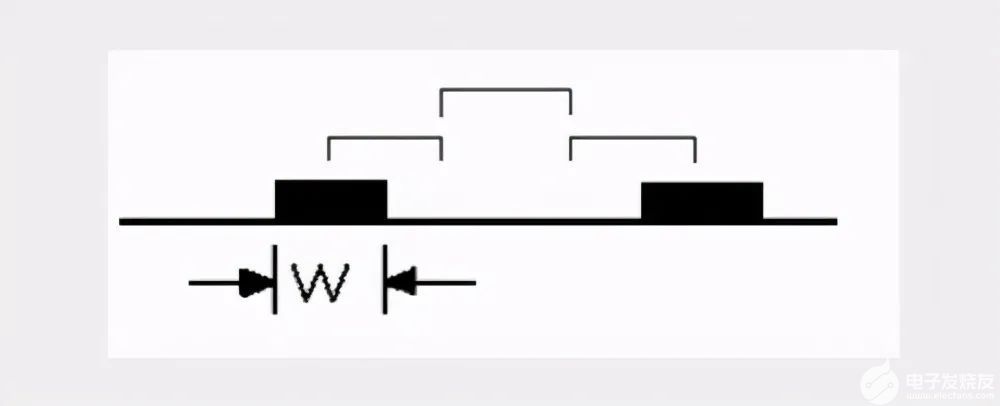

串擾

串擾是兩條信號線之間的耦合,信號線之間的互感和互容引起線上的噪聲。

容性耦合引發耦合電流,而感性耦合引發耦合電壓。PCB 板層的參數、信號線間距、驅動端和接收端的電氣特性及線端接方式對串擾都有一定的影響。

特性阻抗

先來澄清幾個概念,我們經常會看到阻抗、特性阻抗、瞬時阻抗,嚴格來講,他們是有區別的,但是萬變不離其宗,它們仍然是阻抗的基本定義:

將傳輸線始端的輸入阻抗簡稱為阻抗;

將信號隨時遇到的及時阻抗稱為瞬時阻抗;

如果傳輸線具有恒定不變的瞬時阻抗,就稱之為傳輸線的特性阻抗。

特性阻抗描述了信號沿傳輸線傳播時所受到的瞬態阻抗,這是影響傳輸線電路中信號完整性的一個主要因素。

如果沒有特殊說明,一般用特性阻抗來統稱傳輸線阻抗。

PS:對于高速PCB設計而言,我們的目標是信號在傳輸過程中盡量保持阻抗穩定,而這必須保持傳輸線特性阻抗的穩定。

電源完整性

電源完整性(Power integrity)簡稱PI,是確認電源來源及目的端的電壓及電流是否符合需求。

電源完整性在現今的電子產品中相當重要。有幾個有關電源完整性的層面:芯片層面、芯片封裝層面、電路板層面及系統層面。

其中,在電路板層面的電源完整性要達到以下三個需求:

使芯片引腳的電壓漣波比規格要小一些(例如電壓和1V之間的誤差小于+/-50 mV)

控制接地反彈(也稱為同步切換噪聲SSN、同步切換輸出SSO)

降低電磁干擾(EMI)并且維持電磁兼容性(EMC):電源分布網絡(PDN)是電路板上最大型的導體,因此也是最容易發射及接收噪聲的天線。

電源噪聲

電源噪聲是電磁干擾的一種,其傳導噪聲的頻譜大致為10kHz~30MHz,最高可達150MHz。

電源噪聲,特別是瞬態噪聲干擾,其上升速度快、持續時間短、電壓振幅度高、隨機性強,對微機和數字電路易產生嚴重干擾。

在高頻電路中,電源所帶有的噪聲對高頻信號影響尤為明顯。因此,首先要求電源是低噪聲的。在這里,干凈的地和干凈的電源同樣重要。

濾波

濾波(Wave filtering)是將信號中特定波段頻率濾除的操作,是抑制和防止干擾的一項重要措施,濾波分為經典濾波和現代濾波。

并行總線

總線是兩個或兩個以上設備通訊的共享物理通路,是信號線的集合,是多個部件間的公共連線,用于在各個部件間傳輸信息。

接照工作模式不同,總線可以分為兩種類型:一種是并行總線,一種是串行總線。

并行總線:同一時刻可以傳輸多位數據,好比是一條允許多輛車并排開的寬敞道路,而且它還有雙向單向之分。

串行總線

串行總線:在同一時刻只能傳輸一個數據,好比只容許一輛車行走的狹窄道路,數據必須一個接一個傳輸、看起來仿佛一個長長的數據串,故稱為“串行”。

拓撲結構

拓撲結構是指網絡中各個站點相互連接的形式,PCB設計中的拓撲,指的是芯片之間的連接關系。

常用的拓撲結構包括點對點、菊花鏈、遠端簇型、星型等。

責任編輯人:CC

-

高速PCB設計

+關注

關注

2文章

50瀏覽量

15256 -

高速PCB

+關注

關注

4文章

94瀏覽量

25090

原文標題:學習高速PCB設計,掌握這10個知識點很重要!

文章出處:【微信號:gh_454737165c13,微信公眾號:Torex產品資訊】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

關于高速PCB設計的串擾知識

關于高速PCB設計的串擾知識

高速PCB設計中有關阻抗的一些知識

高速PCB設計誤區與對策

高速PCB設計的6個關鍵要素

10個和高速PCB設計相關的重要知識分享

10個和高速PCB設計相關的重要知識分享

評論