本應(yīng)用筆記說明了如何使用微處理器的UART來實現(xiàn)1-Wire?總線主機。它包括所需的電接口,UART配置以及UART與1-Wire信號之間的時序關(guān)系的說明。設(shè)置UART字節(jié)時序提供的靈活性允許直接實現(xiàn)1-Wire時隙以及復(fù)位和在線檢測脈沖。通過包含深度發(fā)送和接收FIFO,可以在1-Wire總線上傳輸幾個字節(jié)值,而主處理器只需要每位幾個時鐘周期即可。

1-Wire器件為識別,存儲,計時,測量和控制提供了經(jīng)濟的解決方案。1-Wire數(shù)據(jù)接口減小到絕對最小值,即一條數(shù)據(jù)線加上一個接地基準。由于大多數(shù)1-Wire器件提供的數(shù)據(jù)量相對較少,典型的16kbps數(shù)據(jù)速率足以滿足預(yù)期任務(wù)的需要。通常以“位敲打”的方式使用8位或16位微控制器的通用輸入/輸出(GPIO)引腳作為總線主控器很方便。

但是,在32位系統(tǒng)中,處理器時鐘頻率通常超過100MHz,并且使用GPIO引腳作為1-Wire總線主機時,每個1-Wire位消耗大量時鐘周期。在32位便攜式系統(tǒng)中,在對1-Wire讀寫時隙進行定時時會消耗寶貴的電池電量。一些系統(tǒng)通過在其芯片組中包含DS1WM可合成1-Wire總線主控器*硬件模塊,減輕了主處理器的位定時和字節(jié)成幀操作的負擔(dān)。如果DS1WM或其他硬件1-Wire主端口不可用,則在有通用異步接收器發(fā)送器(UART)通道可用的情況下,與1-Wire器件的通信可以輕松完成。

本應(yīng)用筆記包括所需的電氣接口,UART配置以及UART與1-Wire信號之間的時序關(guān)系的說明。假定對1-Wire通信有一個一般的了解。在下面的討論中將使用典型的時序和邏輯電平,讀者應(yīng)參考特定的1-Wire器件數(shù)據(jù)手冊,以了解特定的時序和電壓規(guī)格以及容差。

正確配置了波特率,每個字符的數(shù)據(jù)位,奇偶校驗和停止位的數(shù)量后,每秒115,200位的UART提供了實現(xiàn)1-Wire主設(shè)備所需的輸入和輸出時序。UART產(chǎn)生1-Wire復(fù)位脈沖以及讀和寫時隙。微處理器只需將一個字節(jié)的字符代碼放入UART發(fā)送寄存器中,以發(fā)送1-Wire 1或0位,然后UART即可完成工作。相反,微處理器讀取與從1-Wire從器件讀取的1位或0位相對應(yīng)的單字節(jié)字符代碼。所有1-Wire位傳輸都需要總線主機UART來通過將1-Wire總線驅(qū)動為低電平來開始周期。因此,每個1-Wire位周期包括UART發(fā)送的字節(jié)和接收的字節(jié)。讀取時,接收到的數(shù)據(jù)是有意義的,但是寫入時,接收字節(jié)被丟棄。根據(jù)UART的讀取和寫入先進先出(FIFO)緩沖區(qū)深度,UART還可以將1-Wire位成幀為字節(jié)值,從而進一步減少了處理器開銷。

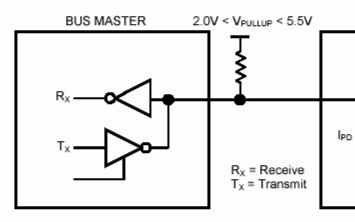

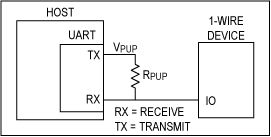

UART至1-Wire電接口

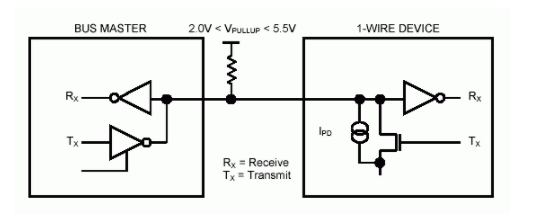

1-Wire器件在漏極開路環(huán)境下,總線電壓范圍為2.0V至5.5V。精確的邏輯電平和最小上拉電壓取決于器件,盡管通常寄生功率器件要求最小上拉電壓為2.8V,以便在數(shù)據(jù)線為低電平期間為用于供電的內(nèi)部存儲電容器充電。4.7kΩ電阻通常用作1-Wire數(shù)據(jù)線上的上拉電阻。電阻器被動地提供邏輯高信號,總線主機和所有從器件驅(qū)動邏輯低信號。器件通常具有弱內(nèi)部下拉電阻,如圖1的Ipd所示。

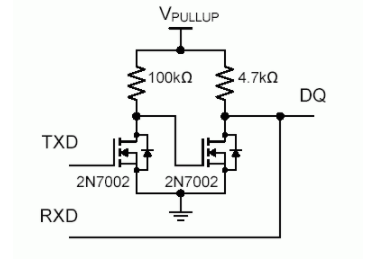

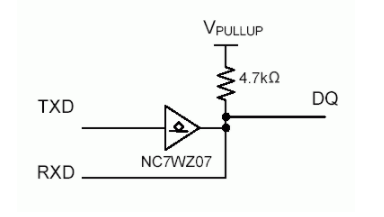

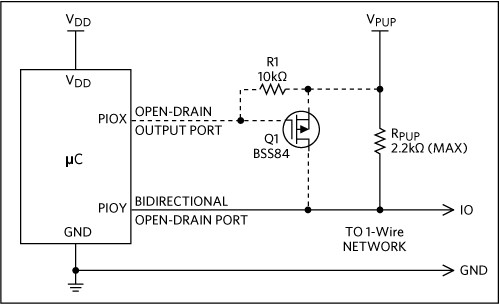

由于大多數(shù)UART發(fā)送數(shù)據(jù)(TXD)引腳都不是漏極開路的,因此通常需要一個外部漏極開路緩沖電路。該電路可以由如圖2所示的分立元件構(gòu)成,也可以采用如圖3所示的FairchildNC7WZ07之類的集成解決方案。在這兩個電路中,4.7kΩ上拉電阻在1-Wire總線上提供邏輯高電平。

離散漏極開路緩沖器。

集成的漏極開路緩沖器。

編輯:hfy

-

處理器

+關(guān)注

關(guān)注

68文章

19407瀏覽量

231183 -

緩沖器

+關(guān)注

關(guān)注

6文章

1930瀏覽量

45645

發(fā)布評論請先 登錄

相關(guān)推薦

DS2465 SHA-256協(xié)處理器與1-Wire主機功能

基于C++模板技術(shù)的1-wire總線編程

微控制器和1-Wire溫度傳感器的軟件接口

DS2480B串行接口1-Wire 線驅(qū)動器的使用

嵌入1-Wire主機

嵌入1-Wire主機

用軟件實現(xiàn)1-Wire通信

1-Wire雙向電平轉(zhuǎn)換器應(yīng)用

1-Wire總線主機

為什么UART驅(qū)動1-Wire設(shè)備總是出現(xiàn)問題?

實現(xiàn)隔離式1-Wire總線

可靠的長線1-Wire網(wǎng)絡(luò)指南

如何使用微處理器的UART來實現(xiàn)1-Wire?總線主機

如何使用微處理器的UART來實現(xiàn)1-Wire?總線主機

評論