在這個圍毆開篇的時候征集了大伙的一些問題及最感興趣的話題,其中最多的是T型拓撲和Fly_by拓撲的應用,那么這一篇就讓我們了解拓撲和端接方式吧,同時也將開篇時大家的一些其他問題爭取在終結篇給大家答復。

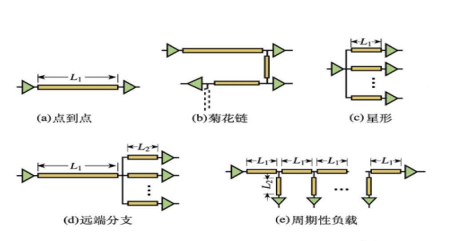

首先,簡單總結下各拓撲的應用場合問題。點對點拓撲主要用在時鐘及比較單一的芯片連接上,這個誰都會,就兩個芯片,當然必須點對點啊!同時與點對點搭配最多的就是源端串聯端接,當然也有其他的并聯端接。那么點對點拓撲可不可以不用外部端接?當然是有的,如DDR3的數據信號就可以不用外部端接,因為它有ODT(片內端接)。還有一些可調驅動的電路,其他的就比較少了。如果不想加外部端接又要保證系統足夠穩定怎么辦呢?高速先生的回答是:仿真,仿真,仿真(重要的事情說三遍哈)!另外還有一些經驗可以供大家參考,那就是將線路阻抗做小(源端匹配的考慮,一般芯片驅動內阻都是低于50歐姆的)!點對多點拓撲就稍微復雜點,主要看信號速率以及負載數目了。超過100MHz的多負載拓撲及端接方案建議先仿真,一兩句話也說不清楚,具體問題具體分析吧。

其次,不同的端接方式有不同的考慮點。

末端并聯端接也用的比較多,如前文提到的T點及Fly_by拓撲,其中上拉比較常見,端接電阻通常和傳輸線阻抗一致,但也有例外,如負載較多的情況下這個阻值還會根據信號質量有一些變化,具體多少最好是通過仿真來確定,最后可以通過測試來驗證。

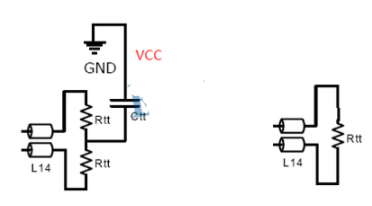

戴維南端接的效果其實和末端上拉是一樣的,在早期的DDR2設計上見得比較多,就相當于上下拉端接。好處是不需要額外轉Vtt電路,一個電阻接到Vcc,一個電阻接到地,并聯之后的效果相當于一個電阻上拉到Vtt。不好的地方就是需要2個電阻,功耗較大,對布線空間本來就很稀缺的設計來說不怎么好實現。通常來說這兩個并聯電阻的阻值是一樣的,如100ohm,這樣并聯后的等效電阻為50ohm,和我們大部分的傳輸線阻抗一致,這個在DDR2的設計里面經常是這樣配置的。當然還有一些其他的電阻組合,如一些非DDR2的情況,有見過80//120組合的,不管怎么組合,通常的原則是并聯后的有效阻抗保持和傳輸線阻抗一致,另外還取決于兩個電阻中間需要的電平的值(分壓的原則)。

最后來看看AC端接,其實如果有經常做DDRx設計的朋友們對這個端接也是非常熟悉的,如我們的DDRx時鐘信號,有時我們使用100歐姆并聯電阻端接,有時我們就使用AC端接,兩端分別接個電阻再到電容,然后再到Vcc或者地,這個就是我們說的AC端接,如下圖所示。

編輯:hfy

-

拓撲

+關注

關注

4文章

341瀏覽量

29671 -

DDR2

+關注

關注

1文章

101瀏覽量

41623 -

并聯電阻

+關注

關注

1文章

47瀏覽量

13563

發布評論請先 登錄

相關推薦

DDR3采用fly-by拓撲為什么有的采用RTT上拉端接,而有的采用RC下拉端接?

如何選擇端接方式

端接的方式和規則

高速PCB的終端端接方式淺析

端接與拓撲竟有這些區別,電子小白收好了!

圍繞拓撲結構與端接展開,淺談對fly-by結構

常用的五種端接方式資料下載

淺談拓撲和不同端接方式

淺談拓撲和不同端接方式

評論