DDR的拓?fù)浣Y(jié)構(gòu)選擇也是一個(gè)老生常談的話題了,從最初只能采用T拓?fù)涞街С肿x寫平衡的Fly-by拓?fù)洌O(shè)計(jì)似乎變得越來(lái)越簡(jiǎn)單了。大家來(lái)看這樣一種情況,一個(gè)驅(qū)動(dòng)拖動(dòng)兩片DDR顆粒,芯片支持讀寫平衡,您一般會(huì)選擇什么拓?fù)浣Y(jié)構(gòu)呢?我想,這個(gè)應(yīng)該和個(gè)人的設(shè)計(jì)習(xí)慣有關(guān),或者選擇T拓?fù)洌蛘哌x擇Fly-by,沒(méi)有標(biāo)準(zhǔn)答案。但是作者最近遇到的一個(gè)項(xiàng)目,一個(gè)主控拖動(dòng)兩個(gè)DDR顆粒,采用Fly-by結(jié)構(gòu),信號(hào)質(zhì)量就不穩(wěn)定,小批量量產(chǎn)總有幾塊板子DDR不能正常工作,仿真發(fā)現(xiàn)DDR信號(hào)質(zhì)量并不是很理想,修改拓?fù)浣Y(jié)構(gòu)后,DDR運(yùn)行變得穩(wěn)定,具體什么情況呢?

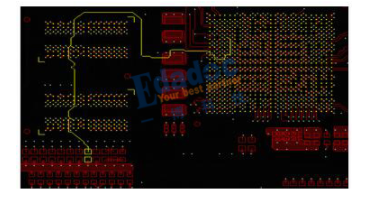

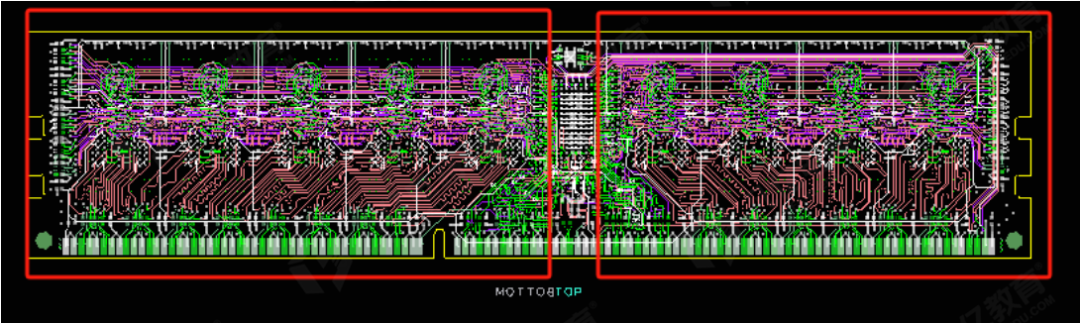

該主板上有一塊FPGA和一塊DSP,F(xiàn)PGA驅(qū)動(dòng)的DDR3沒(méi)有問(wèn)題,但是DSP驅(qū)動(dòng)的DDR不穩(wěn)定,我們仔細(xì)進(jìn)行了查板工作,該主板上DSP與FPGA都是采用Fly-by拓?fù)浣Y(jié)構(gòu),DDR顆粒也都支持讀寫平衡,如下圖1所示,從布線上來(lái)看,設(shè)計(jì)并無(wú)不妥。

圖1 Fly-by 拓?fù)渥呔€

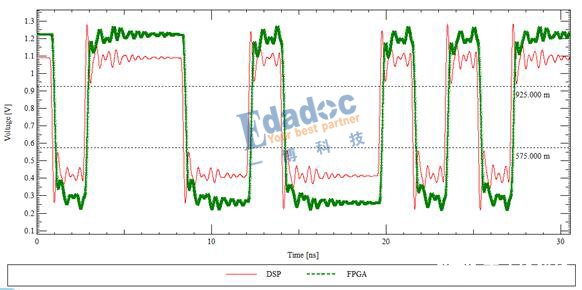

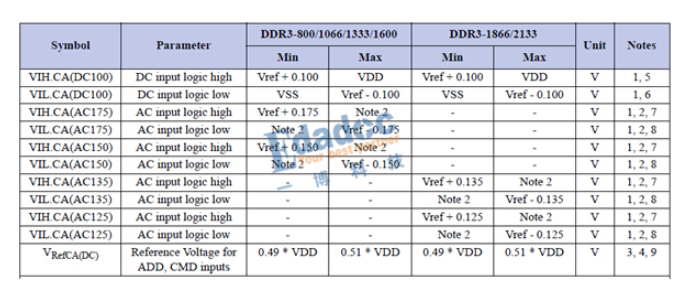

FPGA和DSP作為驅(qū)動(dòng)時(shí),仿真發(fā)現(xiàn),兩者的波形還是存在較大差異的,如下圖所示:

圖2 DSP與FPGA波形對(duì)比

由圖2可知,該主板上FPGA的驅(qū)動(dòng)能力明顯好于DSP,DSP不僅驅(qū)動(dòng)能力比較弱而且信號(hào)的過(guò)沖還很嚴(yán)重,信號(hào)的裕量非常的小。

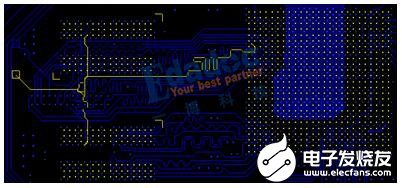

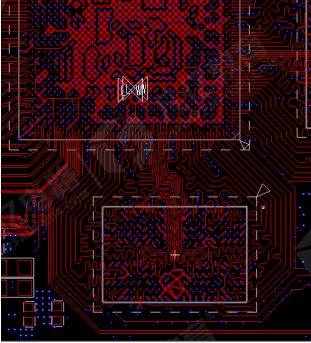

怎樣去改善信號(hào)質(zhì)量呢?芯片的驅(qū)動(dòng)能力是有限的,沒(méi)有太大調(diào)整空間,但既然選擇了這款芯片,也不能輕易的改變,只能從布線上作調(diào)整,希望可以提高信號(hào)裕量,于是,作者想到了使用T拓?fù)浣Y(jié)構(gòu),修改后的拓?fù)浣Y(jié)構(gòu)如下圖3所示:

圖3 T拓?fù)渥呔€

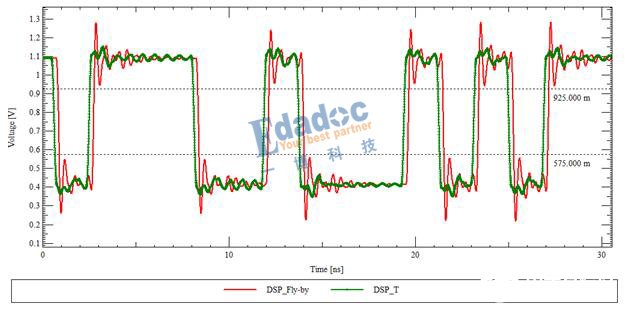

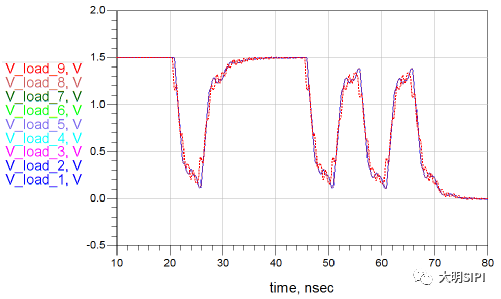

經(jīng)過(guò)仿真分析,將Fly-by拓?fù)渥兂蒚拓?fù)渲螅盘?hào)質(zhì)量明顯好了很多,如下圖所示,紅色波形代表的是采用Fly-by拓?fù)鋾r(shí)信號(hào)的波形,綠色波形代表的是采用T拓?fù)鋾r(shí),仿真得到的波形。相比于采用Fly-by拓?fù)洌琓拓?fù)涞玫降牟ㄐ芜^(guò)沖更小。

圖4 T拓?fù)渑cFly-by拓?fù)渥呔€對(duì)比

修改拓?fù)浣Y(jié)構(gòu),實(shí)際打板,再次小批量量產(chǎn),該主板DSP驅(qū)動(dòng)DDR不穩(wěn)定的現(xiàn)象沒(méi)有了。

看來(lái)在顆粒數(shù)目比較小的情況下,T拓?fù)溥€是具有一定的優(yōu)勢(shì)的,因?yàn)門拓?fù)涫峭耆珜?duì)稱的,在完全等臂分支的情況下,兩個(gè)接收端感受到的反射也是一樣的,可以相互抵消一部分,從而抑制信號(hào)過(guò)沖。

總結(jié):

(1) DDR的拓?fù)浣Y(jié)構(gòu)選擇還要考慮芯片的驅(qū)動(dòng)能力,同樣的拓?fù)浣Y(jié)構(gòu),不同的芯片驅(qū)動(dòng)得到不同的信號(hào)質(zhì)量,所以拓?fù)浣Y(jié)構(gòu)的設(shè)計(jì)也不是一勞永逸的,最好做一下仿真驗(yàn)證,評(píng)估設(shè)計(jì)風(fēng)險(xiǎn)。

(2) 顆粒比較少情況(少于4片),建議使用T拓?fù)洌幌鄬?duì)于Fly-by,T拓?fù)鋾?huì)使信號(hào)的過(guò)沖更小,信號(hào)質(zhì)量更穩(wěn)定。

編輯:hfy

-

dsp

+關(guān)注

關(guān)注

554文章

8059瀏覽量

350465 -

FPGA

+關(guān)注

關(guān)注

1630文章

21798瀏覽量

606067

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

在Boost電源中該怎樣去選擇電容的型號(hào)和電容容量呢?

LMH7322怎樣去改善輸出波形呢 ?

案例分享之DDR拓?fù)?/b>結(jié)構(gòu)的選擇

合適的CAN總線拓?fù)?/b>結(jié)構(gòu)如何選擇?

怎樣去設(shè)計(jì)FFD和RFD相結(jié)合的鏈狀拓?fù)?/b>結(jié)構(gòu)?

怎樣去查看RK3399 4.4內(nèi)核的DDR頻率和容量呢

過(guò)孔STUB長(zhǎng),DDR信號(hào)“強(qiáng)”?

ddr3菊花鏈拓?fù)?/b>結(jié)構(gòu)是什么

關(guān)于DDR信號(hào)的如何去判斷信號(hào)質(zhì)量?

DDR PCB設(shè)計(jì)布線時(shí),拓?fù)?/b>結(jié)構(gòu)的選擇

DDR的拓?fù)?/b>結(jié)構(gòu)有哪些

改善帶有ECC奇數(shù)負(fù)載的DDR2信號(hào)質(zhì)量的方法

DDR加終端匹配電阻和不加信號(hào)質(zhì)量的區(qū)別

DDR拓?fù)?/b>結(jié)構(gòu)的詳細(xì)解析

如何選擇DDR的拓?fù)浣Y(jié)構(gòu)?怎樣去改善信號(hào)質(zhì)量呢?

如何選擇DDR的拓?fù)浣Y(jié)構(gòu)?怎樣去改善信號(hào)質(zhì)量呢?

評(píng)論