使用Altium Designer進(jìn)行DDR2的PCB設(shè)計(jì)

本文首先列出了DDR2布線中面臨的困難,接著系統(tǒng)的講述了DDR2電路板設(shè)計(jì)的具體方法,最后給出個(gè)人對(duì)本次電路設(shè)計(jì)的一些思考。本次設(shè)計(jì)中CPU的封裝為BGA844-SOC-Y,DDR2的封裝為FBGA84,DDR2的控制總線采用星形連接,使用的PCB軟件為AltiumDesigner10,參考設(shè)計(jì)教程為《Altium Designer DDR2設(shè)計(jì)教學(xué)視頻》[1]!

1. DDR2布線中面臨的困難

1.1 DDR與CPU之間的布局[1]

(1)DDR2:內(nèi)存與CPU的邊緣間距建議5~8mm;

(2)DDR3:排阻自身長(zhǎng)度為2mm,排阻與CPU邊緣間距建議3mm,排阻與內(nèi)存邊緣間距建議3mm。

1.2 如何設(shè)置Width(信號(hào)線寬)和Clearance(安全間距)?

在封裝BGA844-SOC-Y中,焊盤的直徑為18.9mil,焊盤間距為39.37mil,兩個(gè)焊盤之間的間隔為20.47mil,要想從BGA中引出所有的信號(hào)線,必須合理的設(shè)置Width和Clearance等規(guī)則。

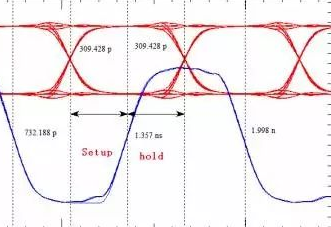

圖1 BGA844-SOC-Y焊盤間距

在《DDR布線規(guī)則與過程》[2]一文中,交代了線寬與線距的設(shè)置規(guī)則:

(1)DDR的供電線線寬建議8mil以上,信號(hào)線默認(rèn)線寬為5mil;

(2)線與線間距建議采用2W原則為8mil,線與其它sub-class的間距為5mil;

(3)CPU與DDR的區(qū)域規(guī)則:走線線寬為5mil,允許最小間距為3.3mil;

在博通BCM53344開發(fā)板中,CPU采用1006-pin FCBGA封裝,DDR3采用FBGA封裝,在BGA的區(qū)域內(nèi),線間距設(shè)為3.098mil,如圖2所示,線寬設(shè)為3.902mil,如圖3所示。

圖2 線距規(guī)則

圖3 線寬規(guī)則

1.3 網(wǎng)絡(luò)分類與差分線的設(shè)置

在《DDR2信號(hào)分類及等長(zhǎng)設(shè)計(jì)》[3]一文中,DDR2可以分為以下三類:

(1)差分時(shí)鐘信號(hào):CLK_N,CLK_P;

(2)數(shù)據(jù)線DQ0~DQ15,數(shù)據(jù)掩碼信號(hào)DQM0,DQM1,數(shù)據(jù)選通信號(hào)DQS*_N,DQS*_P;

(3)地址線/控制線:除數(shù)據(jù),時(shí)鐘外的其他信號(hào),如A0~A12,WE,CS,BA0~2,CKE等;

可以設(shè)置為以下幾個(gè)class規(guī)則:

(1)DATA_L_BUS:Q0~DQ7,DQM0,DQS0_N,DQS0_P;

(2)DATA_H_BUS:Q8~DQ15,DQM1,DQS1_N,DQS1_P;

(3)ADDR_BUS:除數(shù)據(jù)線外的其他信號(hào);

(4)CLK_DIFF: CLK_N,CLK_P;

1.4 如何確定小T點(diǎn)與大T點(diǎn)的位置?

如圖4所示,小T點(diǎn)對(duì)應(yīng)于DDR2焊盤扇出后的過孔C與D,C與D點(diǎn)扇出的走線方式必須保持一致。大T點(diǎn)對(duì)應(yīng)于地址/命令總線的分支點(diǎn)過孔B,在DDR做等長(zhǎng)布線時(shí),地址/命令總線Net-Class(網(wǎng)絡(luò)類)每條網(wǎng)絡(luò)滿足:

(1)AB+BC=AB+BD;

(2)每條網(wǎng)絡(luò)的總長(zhǎng)度(AB+BC+BD)均相等。

為了降低DDR等長(zhǎng)布線的難度,通常將大T點(diǎn)設(shè)在C與D的對(duì)稱軸上,假如大T點(diǎn)沒有落在C與D的中軸線上,該怎么辦?

在《用Altium Designer實(shí)現(xiàn)DDR2的等長(zhǎng)布線》[4]和《Altium Designer 中 DDRII SDRAM 的等長(zhǎng)布線》[5]中給出了解決辦法,文中使用了AD里面的From-To Editor 網(wǎng)絡(luò)編輯器,將同一個(gè)網(wǎng)絡(luò)在T點(diǎn)處劃分為3個(gè)部分,然后通過設(shè)置焊盤到焊盤之間的等長(zhǎng)來實(shí)現(xiàn)DDR的等長(zhǎng)布線,有興趣的讀者可以查看原文!

圖4 選取大T點(diǎn)

1.5 BGA自動(dòng)扇出與手動(dòng)優(yōu)化

在使用AD10給BGA自動(dòng)扇出時(shí),需要注意一下幾點(diǎn):

(1)在執(zhí)行自動(dòng)扇出前,BGA上的所有焊盤均不能連線,否則自動(dòng)扇出無法完成!

(2)FBGA84封裝的DDR2在進(jìn)行自動(dòng)扇出時(shí),扇出的效果非常差,必須使用手工扇出。

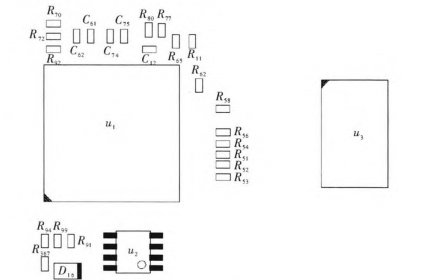

對(duì)CPU和DDR2進(jìn)行自動(dòng)扇出,可分別得到圖5和圖6所示所示結(jié)果。

圖5 CPU自動(dòng)扇出

圖6 DDR2自動(dòng)扇出效果

1.6 如何控制等長(zhǎng)誤差

在《DDR2信號(hào)分類及等長(zhǎng)設(shè)計(jì)》[3]一文中,等長(zhǎng)誤差如下設(shè)置:

(1)所有信號(hào)線參考差分時(shí)鐘的長(zhǎng)度作等長(zhǎng);

(2)DATA_L_BUS共11根走在同層,與差分時(shí)鐘的長(zhǎng)度誤差25mil;

(3)DATA_H_BUS共11根走在同層,與差分時(shí)鐘的長(zhǎng)度誤差25mil;

(4)ADDR_BUS:與差分時(shí)鐘的長(zhǎng)度誤差200~300mil;

在視頻《Altium Designer DDR2設(shè)計(jì)教學(xué)視頻》中,作者給出了如下的等長(zhǎng)誤差,記地址/控制網(wǎng)絡(luò)類(包括差分時(shí)鐘)的等長(zhǎng)目標(biāo)為L(zhǎng)1,數(shù)據(jù)網(wǎng)絡(luò)類等長(zhǎng)目標(biāo)為L(zhǎng)2,則:

(1)在地址/控制網(wǎng)絡(luò)類中,差分時(shí)鐘長(zhǎng)度設(shè)為L(zhǎng)1,其它等長(zhǎng)誤差控制在L1±200mil之內(nèi);

(2)數(shù)據(jù)網(wǎng)絡(luò)類等長(zhǎng)誤差控制在L2±25mil之內(nèi),同一組之間作等長(zhǎng)即可;

(3)L1與L2滿足:0<L1-L2<1000mil!

2. DDR2等長(zhǎng)布線

2.1 區(qū)域規(guī)則ROOM講解

如何放置ROOM?

執(zhí)行Design→Rooms→Place Rectangular Room,給CPU和DDR2添加ROOM,添加后將ROOM名稱分別修改為“CPU_ROOM”、“DDR2_ROOM”,如圖7所示。

圖7 添加ROOM

2.2 區(qū)域規(guī)則設(shè)置

(1)如何設(shè)置規(guī)則?

執(zhí)行Design→Rules...即可進(jìn)入規(guī)則編輯菜單。

(2)如何定義ROOM內(nèi)的規(guī)則?

進(jìn)入規(guī)則編輯器后,首先點(diǎn)擊需要編輯的規(guī)則并右擊新建“new rule...”,接著先點(diǎn)擊新鍵的規(guī)則,然后在“Where The First Object Matches”一欄選擇“Advanced(Query)”,在“Full Query”一欄填入“withinroom('name_ROOM')”,最后Apply并單擊OK即可!

上面的name_ROOM為ROOM的名稱,輸入語法時(shí)請(qǐng)切換為英文輸入法,如果需要同時(shí)給多個(gè)ROOM定義規(guī)則,其語法為:withinroom('name_ROOM')&withinroom('name1_ROOM')&withinroom('name2_ROOM')

(3)如何給PCB定義規(guī)則?

為了引出BGA內(nèi)部走線,規(guī)則中的Clearance和Width進(jìn)行如下設(shè)置:

Clearance設(shè)置方案(優(yōu)先級(jí)從下到上依次遞增):

Clearance_CPU : 4 mil withinroom('CPU_ROOM')

Clearance_DDR2 : 4.4 mil withinroom('DDR2_ROOM')

Clearance : 5 mil

Width(最小 / 推薦 / 最大)設(shè)置方案(優(yōu)先級(jí)從下到上依次遞增):

Width_PWR : 12 / 12 / 120 mil

Width_CPU : 4 / 4 / 4 mil withinroom('CPU_ROOM')

Width_DDR2 : 4.4 / 4.4 / 4.4 mil withinroom('DDR2_ROOM')

Width : 5 / 5 / 5 mil

說明:Width_PWR為電源網(wǎng)絡(luò)的線寬規(guī)則!

2.3 過孔、網(wǎng)絡(luò)CLASS及差分線的設(shè)置

(1)如何給PCB定義Via(過孔)的規(guī)則?

Via(內(nèi)徑 / 外徑)設(shè)置方案(優(yōu)先級(jí)從下到上依次遞增):

RoutingVias_DDR2 : 8 / 16 mil withinroom('DDR2_ROOM')

RoutingVias : 10 / 22 mil

(2)如何設(shè)置網(wǎng)絡(luò)Class

DDR2的所有網(wǎng)絡(luò),可以分為以下3類:

電源地信號(hào),數(shù)據(jù)信號(hào),時(shí)鐘、地址、控制類信號(hào)。

執(zhí)行Design→ Classes...,調(diào)出類設(shè)置界面,按下方的規(guī)則對(duì)網(wǎng)絡(luò)進(jìn)行分類:

POWER_CLASS:GND、VREF、VCC1V8、VTT。

DATA_CLASS:

Data0-7:DRAM0_D0~7、DRAM0_DM0、DRAM0_DQS0_N、DRAM0_DQS0_P;

Data8-15:DRAM0_D8~15、DRAM0_DM1、DRAM0_DQS1_N、DRAM0_DQS1_P;

Data16-23:DRAM0_D16~23、DRAM0_DM2、DRAM0_DQS2_N、DRAM0_DQS2_P;

Data24-31:DRAM0_D24~31、DRAM0_DM3、DRAM0_DQS3_N、DRAM0_DQS3_P;

ADD_CLASS:DRAM0_A0~13、DRAM0_BA0~2、DRAM0_CAS#、DRAM0_CLKE、DRAM0_CLK_N、DRAM0_CLK_P、DRAM0_CS#、DRAM0_ODT、DRAM0_RAS#、DRAM0_WE#

網(wǎng)絡(luò)歸類后效果如圖8所示。

圖8 網(wǎng)絡(luò)分類

(3)如何設(shè)置差分線?

在軟件左側(cè)欄中,選擇“Differential Pairs Editor”項(xiàng)目,將DDR2的時(shí)鐘和DQS信號(hào)歸為差分對(duì),如圖1.10所示:

差分對(duì)DRAM0_DQS0:DRAM0_DQS0_N、DRAM0_DQS0_P;

差分對(duì)DRAM0_DQS1:DRAM0_DQS1_N、DRAM0_DQS1_P;

差分對(duì)DRAM0_DQS2:DRAM0_DQS2_N、DRAM0_DQS2_P;

差分對(duì)DRAM0_DQS3:DRAM0_DQS3_N、DRAM0_DQS3_P;

差分對(duì)DRAM0_CLK:DRAM0_CLK_N、DRAM0_CLK_P。

圖9 添加差分對(duì)

2.4 小T點(diǎn)設(shè)置

DDR2手動(dòng)扇出效果圖如圖10所示,封裝中心處的過孔對(duì)應(yīng)為小T點(diǎn),兩個(gè)小T點(diǎn)的中點(diǎn)對(duì)應(yīng)大T點(diǎn)所在的位置。

完成小T點(diǎn)的設(shè)置主要分為以下幾步:

1. 對(duì)左側(cè)的DDR2進(jìn)行手動(dòng)扇出;

2. 全選DDR2扇出的走線和過孔,對(duì)已選對(duì)象進(jìn)行復(fù)制并以左上第一個(gè)焊盤作為參考點(diǎn);

3. 將所選對(duì)象復(fù)制到右側(cè)DDR2上,十字光標(biāo)對(duì)準(zhǔn)左上第一個(gè)焊盤!

以上操作也可稱作走線與過孔的復(fù)用!

圖10 小T點(diǎn)設(shè)置

圖10 小T點(diǎn)設(shè)置

2.5 大T點(diǎn)設(shè)置

將圖10的小T點(diǎn)依次連接,并在兩個(gè)小T點(diǎn)的中心打上過孔(即大T點(diǎn)),完成后效果如圖11所示。

在連線時(shí)請(qǐng)注意以下細(xì)節(jié):

1. 大T點(diǎn)的位置是允許一定的誤差的,不需要絕對(duì)的中心!

2. 繞線時(shí)需要優(yōu)化電源過孔的布局;

3. 小T點(diǎn)(過孔)之間的水平與垂直間距需要保持在30mil以上!

4. 大T點(diǎn)與小T點(diǎn)放置完后,請(qǐng)進(jìn)行上鎖設(shè)置,防止誤刪!

圖11 大T點(diǎn)設(shè)置

2.6 CPU自動(dòng)扇出

執(zhí)行Auto Route→Fanout→Component,點(diǎn)擊CPU封裝即可完成CPU的自動(dòng)扇出,扇出效果如圖12所示。由于規(guī)則的設(shè)置,電源類管腳扇出線寬為12mil,信號(hào)管腳扇出線寬為4mil,下圖中打白色圓圈的管腳為無網(wǎng)絡(luò)的焊盤。

圖12 CPU扇出

2.7 數(shù)據(jù)互聯(lián)

數(shù)據(jù)類總線分為兩部分互連,一部分走頂層,另一部分走L3層!

如圖13所示,為數(shù)據(jù)網(wǎng)絡(luò)類DATA0-[D8-15]和DATA0-[D24-31]在頂層的連線效果圖。

圖13 頂層DDR數(shù)據(jù)線互連

如圖14所示,為數(shù)據(jù)網(wǎng)絡(luò)類DATA0-[D0-7]和DATA0-[D16-23]在L3層的連線效果圖。

圖14 L3層DDR數(shù)據(jù)線互連

2.8 地址線T點(diǎn)互連

地址與控制類總線分為兩部分互連,一部分走頂層如圖15所示,另一部分走底層如圖16所示。

圖15 頂層控制、地址類總線連接

圖16 底層控制、地址類總線連接

2.9 尋找等長(zhǎng)目標(biāo)

如圖16所示,為地址類網(wǎng)絡(luò)長(zhǎng)度分布,根據(jù)網(wǎng)絡(luò)長(zhǎng)度分布,選擇3000mil作為地址類網(wǎng)絡(luò)的等長(zhǎng)目標(biāo),等長(zhǎng)誤差控制在±200mil以內(nèi)。

根據(jù)作者描述,地址類與數(shù)據(jù)類網(wǎng)絡(luò)長(zhǎng)度差應(yīng)小于1000mil,所以將數(shù)據(jù)類網(wǎng)絡(luò)等長(zhǎng)目標(biāo)控制在2000mil,數(shù)據(jù)類網(wǎng)絡(luò)之間的等長(zhǎng)誤差控制在±25mil以內(nèi)。

2.10 走等長(zhǎng)線

1. 如何走等長(zhǎng)線?

(1)普通信號(hào)線,按快捷鍵T+R,差分線按T+I,進(jìn)入等長(zhǎng)布線狀態(tài);

(2)等長(zhǎng)布線時(shí),W鍵上方的1、2、3、4依次對(duì)應(yīng)拐角弧度減小、拐角弧度增大、蛇形線間距減小、蛇形線間距增大等功能!

2 地址類等長(zhǎng)

頂層:

圖17 頂層地址網(wǎng)絡(luò)等長(zhǎng)

底層:

圖18 底層地址網(wǎng)絡(luò)等長(zhǎng)

3. 數(shù)據(jù)類等長(zhǎng)

頂層

圖19 頂層數(shù)據(jù)網(wǎng)絡(luò)等長(zhǎng)

底層

圖20 L3層數(shù)據(jù)網(wǎng)絡(luò)等長(zhǎng)

2.11 等長(zhǎng)輸出

在Nets查看欄中,復(fù)制需要等長(zhǎng)網(wǎng)絡(luò)的名稱和長(zhǎng)度等屬性,粘貼到Excel中并加以整理,即完成了DDR2等長(zhǎng)信息的輸出!

3. 個(gè)人思考

1、為何同一根信號(hào)線在不同區(qū)域(CPU_ROOM、DDR2_ROOM、其它)的線寬會(huì)不一樣?

(1)在其它區(qū)域(DDR與CPU的中間區(qū)域)走5mil的線,是通過阻抗匹配計(jì)算出來的結(jié)果;

(2)在CPU_ROOM內(nèi)走4mil的線是為了使信號(hào)線從BGA內(nèi)部扇出,那么信號(hào)線在其它區(qū)域?yàn)槭裁床挥?mil的線呢,這里可能是考慮了成本的原因(線寬越小成本越高)。在不影響DDR2性能同時(shí)又要使信號(hào)線成功扇出的情況下,必須使信號(hào)線擁有多重線寬規(guī)則(個(gè)人猜測(cè),沒有證實(shí)過)!

2、如何最大化利用好布線空間,同時(shí)減小信號(hào)線間的串?dāng)_?

如何最大化利用好布線空間:

地址總線的布線空間最緊張,需要優(yōu)先布局,相鄰信號(hào)線走蛇形線的區(qū)域應(yīng)錯(cuò)開,走完所有的地址類信號(hào)線再走數(shù)據(jù)類信號(hào)線!

減小信號(hào)線間的串?dāng)_,可通過增加信號(hào)線之間的安全間距來實(shí)現(xiàn),具體方法有:

(1)可以先改變?nèi)值腸learance規(guī)則(優(yōu)先級(jí)設(shè)為最高),比如設(shè)為10mil,如果出現(xiàn)報(bào)錯(cuò)提示可暫時(shí)忽略,走完等長(zhǎng)線后再改回原有規(guī)則!

(2)在走線的側(cè)邊直接畫出一條無網(wǎng)絡(luò)的銅線,走完信號(hào)后再刪除該銅線!

(3)修改等長(zhǎng)控制參數(shù)中的振幅。

3、相同模塊之間的復(fù)用

在第2.4小節(jié)中,將左側(cè)DDR2的扇出銅線和過孔進(jìn)行復(fù)用,可以明顯縮短其它DDR2所需的扇出時(shí)間!

尾巴:本文是我首次接觸高速電路設(shè)計(jì)的一次嘗試,通過文章的形式記錄下學(xué)習(xí)的點(diǎn)滴。本次設(shè)計(jì)并不是一個(gè)完整的工程,在DDR2濾波電容

的放置與優(yōu)化、DDR2信號(hào)完整性仿真、以及PCB阻抗匹配的計(jì)算等方面均未涉及,由于個(gè)人能力有限,文章難免有錯(cuò)誤,希望大家能夠給出

寶貴的建議!

參考:

[1] 《Altium Designer DDR2設(shè)計(jì)教學(xué)視頻》

[2] DDR布線規(guī)則與過程,

[3] DDR2信號(hào)分類及等長(zhǎng)設(shè)計(jì),

[4] 用Altium Designer實(shí)現(xiàn)DDR2的等長(zhǎng)布線,https://wenku.baidu.com/view/a1334bfcad51f01dc281f17e.html

[5] Altium Designer 中 DDRII SDRAM 的等長(zhǎng)布線,https://wenku.baidu.com/view/424dd712ccbff121dc368324.html?re=view

編輯:hfy

-

cpu

+關(guān)注

關(guān)注

68文章

10905瀏覽量

213029 -

altium

+關(guān)注

關(guān)注

47文章

949瀏覽量

118278 -

DDR2

+關(guān)注

關(guān)注

1文章

101瀏覽量

41621 -

PCB設(shè)計(jì)

+關(guān)注

關(guān)注

394文章

4701瀏覽量

86353 -

華秋DFM

+關(guān)注

關(guān)注

20文章

3494瀏覽量

4741

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

DDR布線在PCB設(shè)計(jì)應(yīng)用,你怎么看?

【PCB設(shè)計(jì)干貨】DDR電路的PCB布局布線要求

DDR2布線經(jīng)驗(yàn)總結(jié)

【漢普觀點(diǎn)】PCB設(shè)計(jì)面臨的挑戰(zhàn)

淺談PCB布線設(shè)計(jì)中DDR2的重要性

DDR2的PCB設(shè)計(jì)如何實(shí)現(xiàn)?

什么是DDR2 SDRAM

DDR2,DDR2是什么意思

MPC8379E與DDR2之間的PCB布線及仿真設(shè)計(jì)

DDR2的PCB設(shè)計(jì)問題解決

如何實(shí)現(xiàn)TMS320DM644x數(shù)字媒體系統(tǒng)芯片DMSo實(shí)施DDR2PCB布局

如何實(shí)現(xiàn)在TMS320DM357數(shù)字媒體系統(tǒng)芯片DMS實(shí)施DDR2PCB布局

如何進(jìn)行DDR2高速PCB設(shè)計(jì)和信號(hào)完整性分析的詳細(xì)資料分析

DDR布線在PCB設(shè)計(jì)中的應(yīng)用解析

在DSP上實(shí)現(xiàn)DDR2 PCB布局布線

淺談PCB設(shè)計(jì)DDR2布線中面臨的困難

淺談PCB設(shè)計(jì)DDR2布線中面臨的困難

評(píng)論