一塊四層板PCB的層壓和阻抗計算調整建議

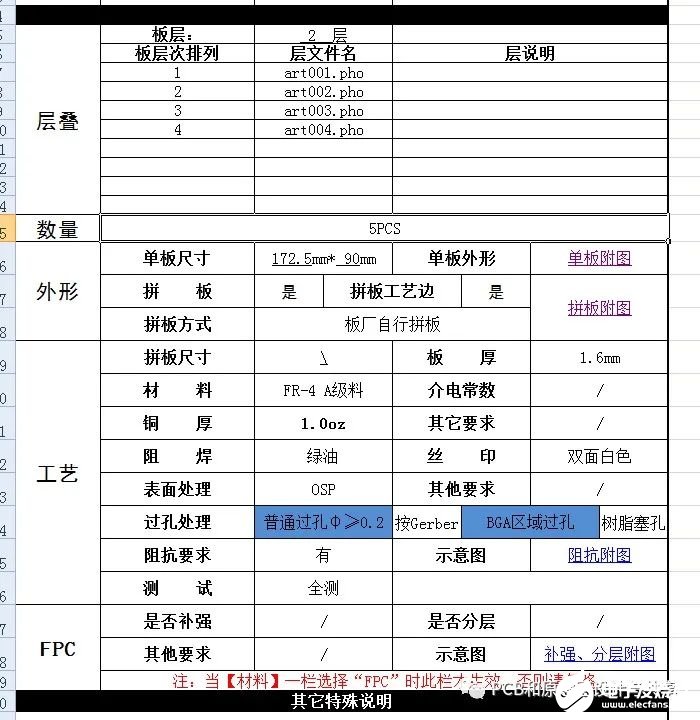

最近設計了一塊四層板PCB,因為是高速電路,有阻抗匹配的要求,所以在發給pcb板廠打樣時,特定指定了哪些線要做阻抗線。我自己給出的做板要求是這樣的。

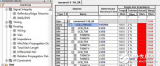

有阻抗匹配要求的線有單端的50歐姆射頻線,有90歐姆的USB差分線,也有100歐姆的DDR差分線,如下圖所示,

50歐姆射頻線阻抗要求:

90歐姆usb差分線和100歐姆DDR差分線阻抗要求:

我自己簡單計算了上述阻抗線的阻抗,半固化片用2116,參考平面的高度按4.5mil來算,介電系數用4.2,銅厚1zo。單端射頻線線寬走6mil,間距10mil,算出單端走線的阻抗是50.47歐姆。

usb差分線線寬走了5mil,間距是5mil,線到地的間距是6mil,算出來的結果是88.96歐姆。

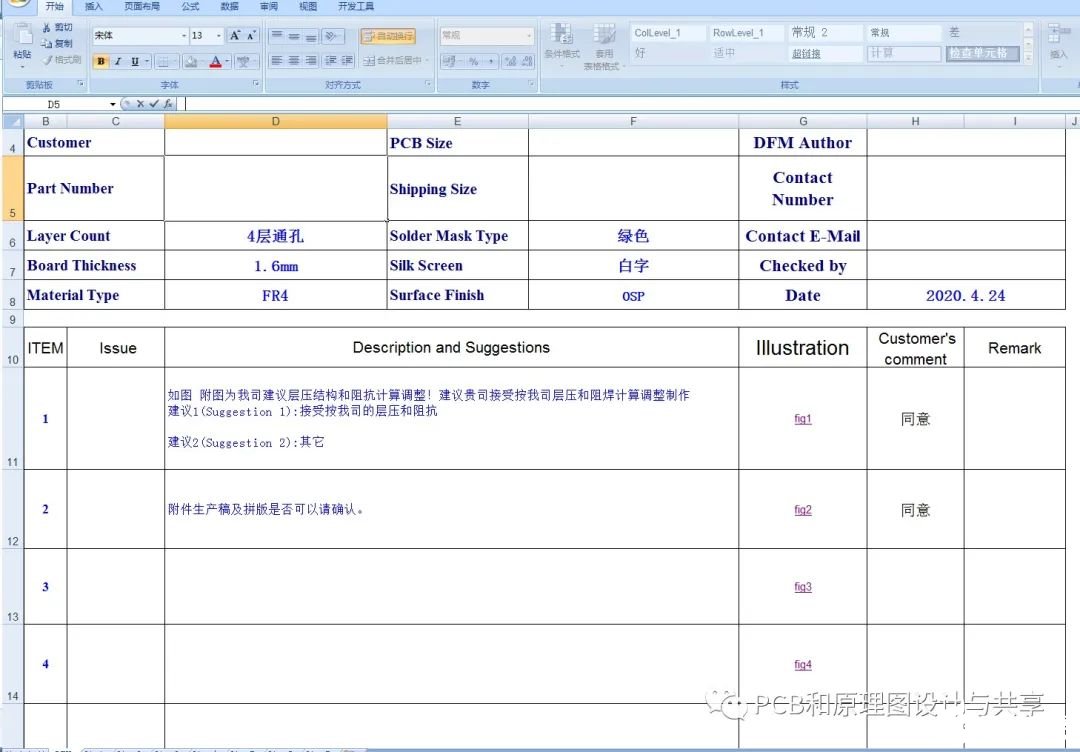

之后板廠評估后反饋回來的層壓和阻抗計算調整建議是這樣的,

從板廠反饋回來的信息可以知道,板廠用的板芯厚是1.3mm,半固化片用的是

3313PP,厚度是0.1mm,換算成mil應該是大概是4mil。

50歐姆單端射頻線不需要調整,按照板廠的層壓方式算出的阻抗是51.77歐姆,可以滿足阻抗要求

90歐姆usb差分線需要由原稿的5mil線寬,5mil間距調整到5.5mil線寬,4.5mil間距,計算出來的阻抗是89.89歐姆,才能滿足要求。

100歐姆的DDR差分線不需要調整,按照板廠的層壓方式算出的阻抗是99.42歐姆,滿足要求。

編輯:hfy

-

pcb

+關注

關注

4326文章

23161瀏覽量

399989 -

阻抗

+關注

關注

17文章

961瀏覽量

46266 -

DDR

+關注

關注

11文章

715瀏覽量

65536 -

高速電路

+關注

關注

8文章

159瀏覽量

24275

發布評論請先 登錄

相關推薦

如何解決PCB設計中的阻抗匹配問題

高速PCB設計中的阻抗匹配

10層板PCB,內層信號層(5,6)阻抗匹配如何選擇參考層?

高頻高速PCB設計中的阻抗匹配,你了解多少?

PCB阻抗匹配計算工具(附教程)

高速PCB中的阻抗匹配

怎樣理解阻抗匹配_pcb阻抗匹配如何計算

關于四層板PCB設計阻抗匹配的要求和建議

關于四層板PCB設計阻抗匹配的要求和建議

評論