1.項目需求

FPGA :V7-690T兩片

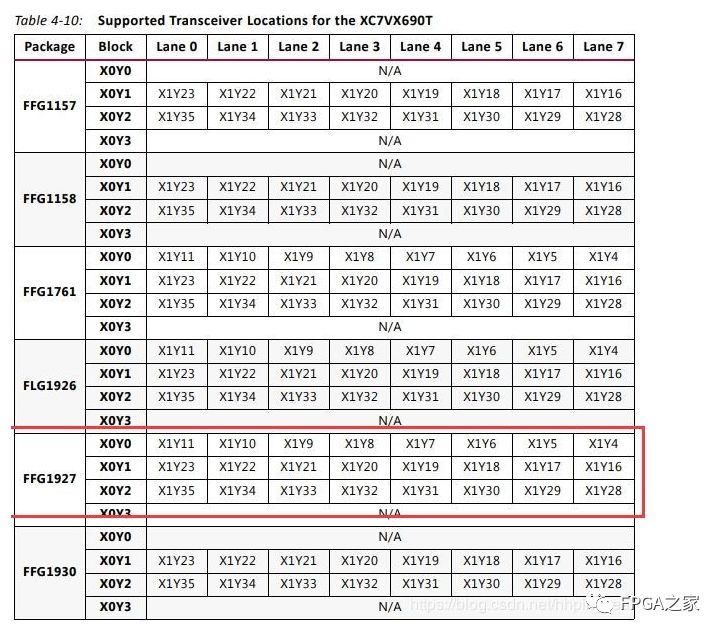

Resource:兩片FPGA通過X12 gth互聯;每片FPGA使用48路serdes走光口與板外連接;每片FPGA使用SIROx4通過VPX與外界互聯;每片FPGA使用PCIE X8與板上CPU Intel XEON互聯;每片FPGA使用20對LVDS互聯;CPLD控制FPGA上電時序/CPU啟動/FPGA加載;每片FPGA掛載2路4GB DDR3。

2.FPGA架構設計問題

我們知道,FPGA片上分布著各種資源,如時鐘,serdes,RAM,LUT,IO等。在進行FPGA規劃時候,應當需要知道項目設計需求,以及需求各模塊之間的數據交織情況,這樣可以避免后續FPGA RTL設計出現時序很難優化的情況。

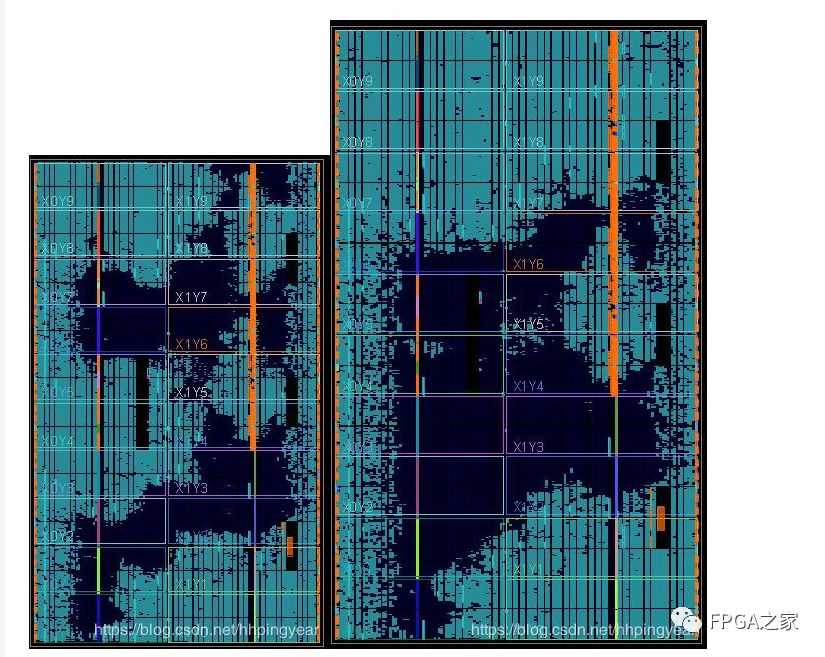

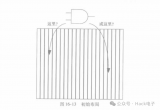

對應這個情況,舉一個簡單的例子。如果一個FPGA工程中含有一個PCIE和一個DDR接口,并且,需要用到PCIE與外部設備進行大量數據塊上傳和下載方面的傳輸。那么DDR作為PCIE的一個緩存接口,最優的方案是在FPGA內部對PCIE接口和DDR接口盡量靠近放置。這樣FPGA RTL設計的時候時序很容易達到最優。在V7-690T FPGA中,可以將PCIE放置的最優位置如下圖。

同時,我們也知道,在V7-690 FPGA中,DDR通常可以放置的位置可以是BANK34/35/36和BANK36/37/38。這時綜合上述兩個條件,我們可以得到最優放置PCIE和DDR的位置。使得FPGA內部編譯通過率或者說時序最好。

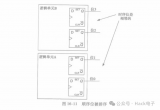

下面是兩種不同放置方式得到的example design編譯結果圖。

3.前期碰到的問題

1).時鐘優化

在管腳驗證的時候,本人將各個功能模塊都用XILINX FPGA的IP生成 example design并集成到一個工程下面,但是發現上面提出的功能集成下來FPGA的BUFG資源遠遠不夠。下圖是FPGA example design各模塊BUFG資源需求情況。因此做了一些資源優化。

a.前期驗證中,發現SRIO是消耗BUFG資源最多的IP,因此能省出最多的BUFG。

b.DDR也消耗比較多時鐘,這個項目一個FPGA用到兩個DDR控制器,也能省出比較多BUFG。

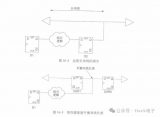

2).PCIE不是在所有serdes下都能放的,對V7-690,需要放置在特殊的SERDES處,這樣,實際PCIE 程序編譯時候,這個特殊的serdes里PCIE 特殊資源離得最近,編譯出來的時序報告是最好的。如若不然,需要設置PCIE IP內部特殊參數,才能使得PCIE DEV被CPU看到,也就是PCIE link上。

3).DDR布局也要參考數據是如何在FPGA內部交織的,勁量靠近會用到大數據流量的模塊放置,這樣后期設計時序會好很多。

4)FPGA功耗估計問題。

這個可以在XILINX官網下載一個XPE Excel表格,很實用的,用一兩次就熟悉了。但是本人認為這個工具對很多人也有個缺點,就是實際并不知道以后自己的代碼各種資源消耗有多少。所以可能評估不太準。

本人是用example design工程查看編譯報告得出。當涉及到調整溫度啊電流啊啥的時候,在vivado下需要打開implementation的結果后才可以改動電流/溫度的值進行評估的。

3.FPGA PCB布線時會遇到調整線序的問題。

1)這要根據項目需求看調整后的布局是否滿足項目需求,調整好后一定要原理圖工程師給出最新的原理圖,最后FPGA根據新布局重新驗證管腳等。千萬不要口口相傳丟失了信息。

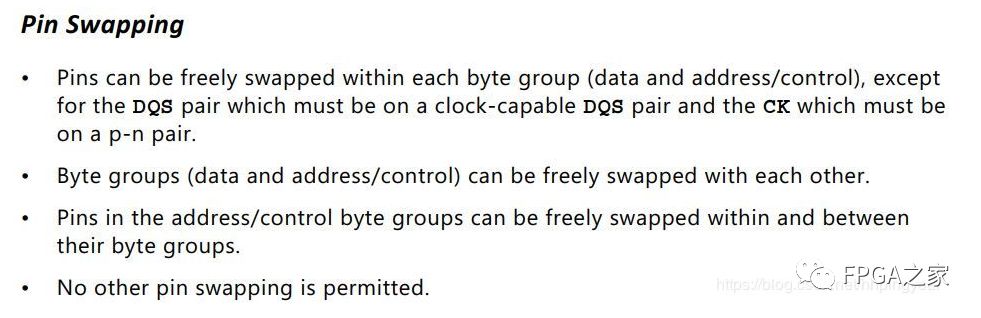

2)DDR換線序可以參照XILINX的MIG手冊,仔細核對的。

3) DDR PCB布線所需的管腳延時信息,可以通過新建一個空白工程,在空白工程的tcl下輸入如下命令:

link_design -part xc7k160tfbg676

4.CPLD調試

1)CPLD控制FPGA上電順序,XILINX又一個check list,各位可以根據check list表格對硬件板卡進行關鍵信號測量確認,對上電時序進行控制等。

2)對FPGA的配置控制也可以月底 xilinx ug470等。

責任編輯:xj

原文標題:FPGA布局及資源優化(開發隨筆)

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1630文章

21798瀏覽量

606037 -

cpld

+關注

關注

32文章

1257瀏覽量

169636 -

時鐘

+關注

關注

11文章

1747瀏覽量

131803

原文標題:FPGA布局及資源優化(開發隨筆)

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何優化 CPLD 性能

如何優化FPGA設計的性能

優化 FPGA HLS 設計

淺談如何克服FPGA I/O引腳分配挑戰

FPGA學習筆記-關于FPGA資源

FPGA布局布線優化策略(五)

FPGA布局布線優化技術

FPGA布局布線的可行性 FPGA布局布線失敗怎么辦

FPGA布局及資源優化

FPGA布局及資源優化

評論