CES 2021期間,存儲大廠威剛“拿”出了他們的下一代DDR5內(nèi)存,不過不是實(shí)物,只是渲染圖。

SK海力士、三星、美光等大廠也在CES 2021期間披露了自己的DDR5規(guī)劃,而作為模組廠商,威剛稱正在與微星、技嘉兩大主板廠商合作,測試自己的DDR5內(nèi)存條,以確保兼容性。

威剛的DDR5內(nèi)存條采用綠色PCB電路板,安放了八顆顆粒,是沒有馬甲的普條。

規(guī)格方面,威剛方面稱頻率最高可達(dá)8400MHz,相當(dāng)于高端DDR4的兩倍左右,單條容量則是直接上到64GB。

威剛沒有透露自己的DDR5顆粒來自哪家,也沒有說何時(shí)出貨。消息稱,Intel Alder Lake 12代酷睿、AMD Zen4架構(gòu)都會支持DDR5。

責(zé)編AJX

-

內(nèi)存

+關(guān)注

關(guān)注

8文章

3055瀏覽量

74328 -

威剛

+關(guān)注

關(guān)注

0文章

46瀏覽量

11252 -

DDR5

+關(guān)注

關(guān)注

1文章

430瀏覽量

24208

發(fā)布評論請先 登錄

相關(guān)推薦

國產(chǎn)DDR5內(nèi)存上市,內(nèi)存市場價(jià)格戰(zhàn)一觸即發(fā)

佰維存儲發(fā)布新一代LPDDR5X內(nèi)存與DDR5內(nèi)存模組

DDR3、DDR4、DDR5的性能對比

DDR5內(nèi)存與DDR4內(nèi)存性能差異

DDR5內(nèi)存的工作原理詳解 DDR5和DDR4的主要區(qū)別

揭秘DDR5的讀寫分離技術(shù)奧秘

Rambus推出DDR5客戶端時(shí)鐘驅(qū)動器

Rambus推出DDR5客戶端時(shí)鐘驅(qū)動器,將業(yè)界領(lǐng)先的內(nèi)存接口芯片產(chǎn)品擴(kuò)展到高性能 PC領(lǐng)域

DDR5內(nèi)存面臨漲價(jià)潮,存儲巨頭轉(zhuǎn)向HBM生產(chǎn)

Introspect DDR5/LPDDR5總線協(xié)議分析儀

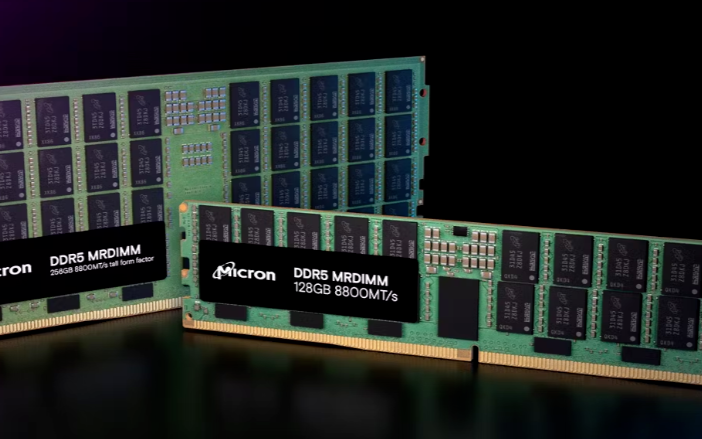

DDR5 MRDIMM內(nèi)存標(biāo)準(zhǔn)將發(fā),存儲廠商方案先行

DDR5內(nèi)存條上的時(shí)鐘走線

0706線下活動 I DDR4/DDR5內(nèi)存技術(shù)高速信號專題設(shè)計(jì)技術(shù)交流活動

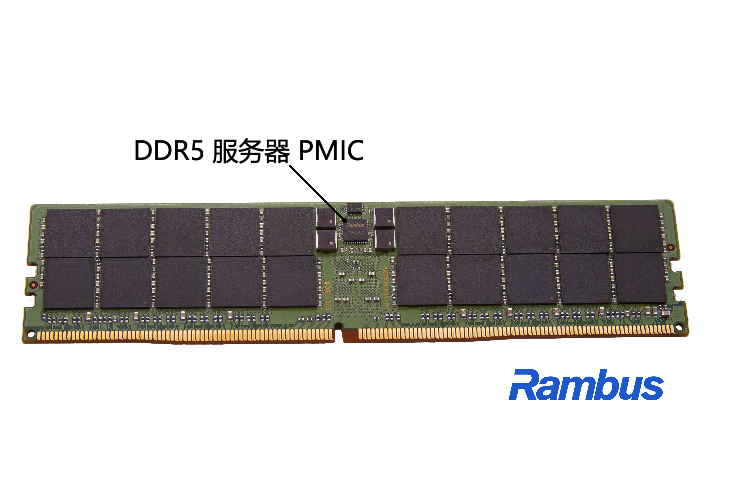

Rambus 通過 DDR5 服務(wù)器 PMIC 擴(kuò)展適用于高級數(shù)據(jù)中心內(nèi)存模塊的芯片組

DDR5內(nèi)存接口芯片組如何利用DDR5 for DIMM的優(yōu)勢?

威剛演示下一代DDR5內(nèi)存渲染圖

威剛演示下一代DDR5內(nèi)存渲染圖

評論