毫無(wú)疑問(wèn),布線是整個(gè)PCB設(shè)計(jì)中最重要、最費(fèi)時(shí)的工序,直接影響著 PCB 板的性能好壞。作為一名合格的、優(yōu)秀的PCB設(shè)計(jì)工程師,除了要把線布通外,更要滿足其電氣性能、讓線整齊美觀,而這需要工程師掌握一些布線技巧。

走線長(zhǎng)度

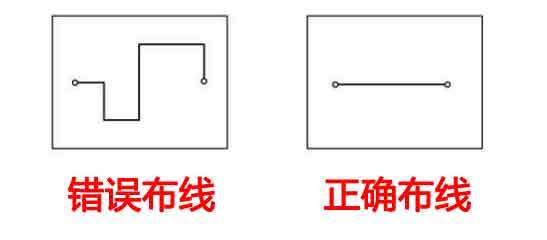

1. 使走線長(zhǎng)度盡可能的短

在 PCB 布線時(shí),應(yīng)該使走線長(zhǎng)度盡可能的短,以減少由走線長(zhǎng)度帶來(lái)的干擾問(wèn)題。

2. 調(diào)整走線長(zhǎng)度

數(shù)字電路系統(tǒng)對(duì)時(shí)序有嚴(yán)格的要求,為了滿足信號(hào)時(shí)序的要求,對(duì)PCB上的信號(hào)走線長(zhǎng)度進(jìn)行調(diào)整已經(jīng)成為PCB設(shè)計(jì)工作的一部分。

走線長(zhǎng)度的調(diào)整包括以下兩個(gè)方面的要求:

a. 要求走線長(zhǎng)度保持一致,保證信號(hào)同步到達(dá)若干個(gè)接收器。有時(shí)在PCB上的一組信號(hào)線之間存在著相關(guān)性,如總線,就需要對(duì)其長(zhǎng)度進(jìn)行校正,因?yàn)樾枰盘?hào)在接收端同步。調(diào)整方法就是找出其中最長(zhǎng)的那根走線,然后將其他走線調(diào)整到等長(zhǎng)。

b. 控制兩個(gè)器件之間的走線延遲為某一個(gè)特定值,如控制器件A、B之間的導(dǎo)線延遲為1ns,而這樣的要求往往由電路設(shè)計(jì)者提出,但由PCB工程師去實(shí)現(xiàn)。需要注意的是,在PCB上的信號(hào)傳播速度是與PCB的材料、走線的結(jié)構(gòu)、走線的寬度、過(guò)孔等因素相關(guān)的。通過(guò)信號(hào)傳播速度,可以計(jì)算出所要求的走線延遲對(duì)應(yīng)的走線長(zhǎng)度。

走線長(zhǎng)度的調(diào)整常采用的是蛇形線的方式。

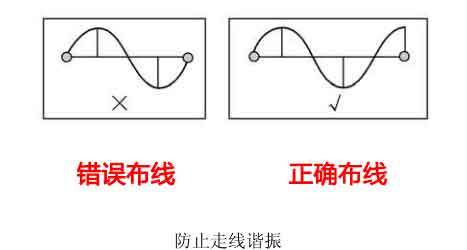

3、防止走線諧振

在PCB布線時(shí),布線長(zhǎng)度不得與其波長(zhǎng)成整數(shù)倍關(guān)系,以免產(chǎn)生諧振現(xiàn)象。

超實(shí)用PCB布線技巧,菜鳥(niǎo)和老司機(jī)都應(yīng)該知道

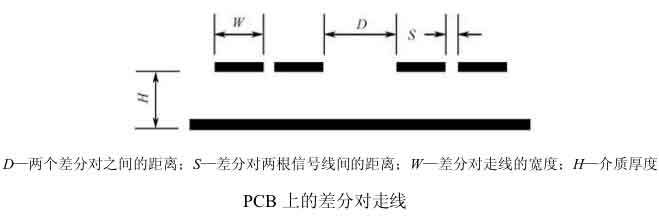

差分對(duì)走線

為了避免不理想返回路徑的影響,可以采用差分對(duì)走線。為了獲得較好的信號(hào)完整性,可以選用差分對(duì)走線來(lái)實(shí)現(xiàn)高速信號(hào)傳輸。

1. 差分信號(hào)傳輸優(yōu)點(diǎn):

a. 輸出驅(qū)動(dòng)總的di/dt會(huì)大幅降低,從而減小了軌道塌陷和潛在的電磁干擾。

c. 差分信號(hào)在一對(duì)緊耦合差分對(duì)中傳輸時(shí),在返回路徑中對(duì)付串?dāng)_和突變的魯棒性更好。

d. 因?yàn)槊總€(gè)信號(hào)都有自己的返回路徑,所以差分信號(hào)通過(guò)接插件或封裝時(shí),不易受到開(kāi)關(guān)噪聲的干擾。

2. 差分信號(hào)的缺點(diǎn):

a. 如果不對(duì)差分信號(hào)進(jìn)行恰當(dāng)?shù)钠胶饣驗(yàn)V波,或者存在任何共模信號(hào),就可能會(huì)產(chǎn)生EMI問(wèn)題。

b. 與單端信號(hào)相比,傳輸差分信號(hào)需要雙倍的信號(hào)線。

3. 設(shè)計(jì)差分對(duì)走線時(shí),要遵循以下原則:

a. 保持差分對(duì)的兩信號(hào)走線之間的距離S在整個(gè)走線上為常數(shù)。

b. 確保D>2S,以最小化兩個(gè)差分對(duì)信號(hào)之間的串?dāng)_。

c. 使差分對(duì)的兩信號(hào)走線之間的距離S滿足S=3H,以便使元件的反射阻抗最小化。

d. 將兩差分信號(hào)線的長(zhǎng)度保持相等,以消除信號(hào)的相位差。

e. 避免在差分對(duì)上使用多個(gè)過(guò)孔,因?yàn)檫^(guò)孔會(huì)產(chǎn)生阻抗不匹配和電感。

電源、地線的處理

即使在整個(gè)PCB板中的布線完成的很好,但由于電源和地線的考慮不周到而引起的干擾,會(huì)使產(chǎn)品的性能下降,有時(shí)甚至?xí)绊懙疆a(chǎn)品的成功率。所以對(duì)電源和地線的處理要認(rèn)真對(duì)待,把電源和地線的所產(chǎn)生的噪音和干擾降到最低限度,以保證產(chǎn)品的質(zhì)量。

1)盡量加寬電源和地線的寬度,最好是地線比電源線寬,它們的關(guān)系是:地線—電源線—信號(hào)線。

2)對(duì)數(shù)字電路的PCB可用寬的地導(dǎo)線組成一個(gè)回路,即構(gòu)成一個(gè)地網(wǎng)來(lái)使用(模擬電路的地不能這樣使用)

3)用大面積銅層作地線用,在印制板上把沒(méi)被用上的地方都與地相連接作為地線用。或是多層板,電源和地線各占用一層。

數(shù)字電路與模擬電路的共地處理

現(xiàn)在許多PCB不再是單一功能電路,而是由數(shù)字電路和模擬電路混合構(gòu)成的。因此在布線時(shí)就需要考慮它們之間互相干擾的問(wèn)題,特別是地線上的噪音干擾。

數(shù)字電路的頻率高,模擬電路的敏感度強(qiáng),對(duì)信號(hào)線來(lái)說(shuō),高頻的信號(hào)線盡可能遠(yuǎn)離敏感的模擬電路器件,對(duì)地線來(lái)說(shuō),整個(gè)PCB對(duì)外界只有一個(gè)結(jié)點(diǎn),所以必須在PCB內(nèi)部進(jìn)行處理數(shù)字和模擬共地的問(wèn)題,而在板內(nèi)部數(shù)字地和模擬地實(shí)際上是分開(kāi)的,它們之間是互不相連的,只是在PCB與外界連接的接口處(如插頭等)。數(shù)字地與模擬地有一點(diǎn)短接,(請(qǐng)注意,只有一個(gè)連接點(diǎn)),也有在PCB上不共地的,這由系統(tǒng)設(shè)定來(lái)決定。

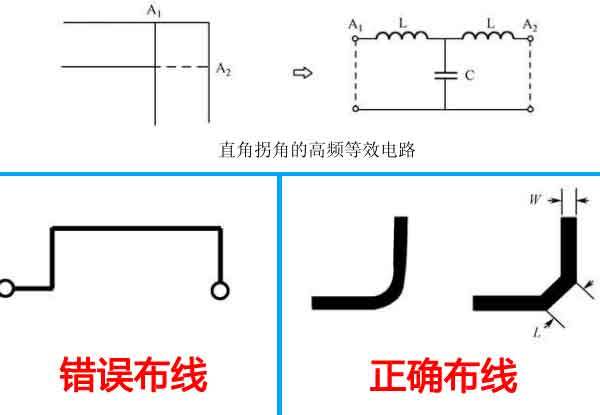

拐角設(shè)計(jì)

在PCB布線時(shí),走線拐彎是不可避免的,當(dāng)走線出現(xiàn)直角拐角時(shí),在拐角處會(huì)產(chǎn)生額外的寄生電容和寄生電感?走線拐彎的拐角應(yīng)避免設(shè)計(jì)成銳角和直角形式,以免產(chǎn)生不必要的輻射,同時(shí)銳角和直角形式的工藝性能也不好?要求所有線與線的夾角應(yīng)大于等于135°?在走線確實(shí)需要直角拐角的情況下,可以采取兩種改進(jìn)方法:一種是將90°拐角變成兩個(gè)45°拐角;另一種是采用圓角?圓角方式是最好的,45°拐角可以用到10GHz頻率上?對(duì)于45°拐角走線,拐角長(zhǎng)度最好滿足L≥3W。

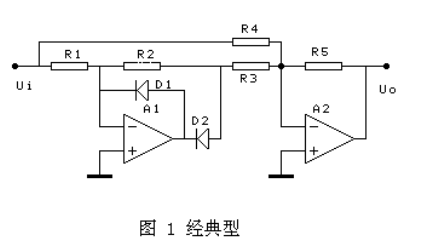

控制PCB導(dǎo)線的阻抗和走線終端匹配

在高速數(shù)字電路PCB和射頻電路PCB中,對(duì)PCB導(dǎo)線的阻抗是有要求的,需要控制PCB導(dǎo)線的阻抗。在PCB布線時(shí),同一網(wǎng)絡(luò)的線寬應(yīng)保持一致。由于線寬的變化會(huì)造成線路特性阻抗的不均勻,對(duì)高速數(shù)字電路傳輸?shù)男盘?hào)會(huì)產(chǎn)生反射,故在設(shè)計(jì)中應(yīng)該盡量避免出現(xiàn)這種情況。在某些條件下,如接插件引出線、BGA封裝的引出線等類似的結(jié)構(gòu)時(shí),如果無(wú)法避免線寬的變化,應(yīng)該盡量控制和減少中間不一致部分的有效長(zhǎng)度。

在高速數(shù)字電路中,當(dāng)PCB布線的延遲時(shí)間大于信號(hào)上升時(shí)間(或下降時(shí)間)的1/4時(shí),該布線即可以看成傳輸線。為了保證信號(hào)的輸入和輸出阻抗與傳輸線的阻抗正確匹配,可以采用多種形式的終端匹配方法,所選擇的匹配方法與網(wǎng)絡(luò)的連接方式和布線的拓?fù)浣Y(jié)構(gòu)有關(guān)。

審核編輯:何安

-

PCB布線

+關(guān)注

關(guān)注

21文章

463瀏覽量

42134

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

電子工程師的PCB設(shè)計(jì)經(jīng)驗(yàn)

不同時(shí)期的硬件工程師,最怕發(fā)生的事 #電子工程師 #硬件工程師 #內(nèi)容過(guò)于真實(shí) #YXC晶振 #揚(yáng)興科技

104條關(guān)于PCB布局布線的小技巧

談?wù)?b class='flag-5'>PCB工程師金字塔分級(jí)標(biāo)準(zhǔn)

笑死,掌握一眼識(shí)別資深硬件工程師的訣竅了!# #電路知識(shí) #電工 #硬核拆解

硬件工程師需要掌握的硬件基礎(chǔ)知識(shí)

硬件工程師VS軟件工程師|硬件工程師看到這都淚目了!#硬件設(shè)計(jì) #硬件工程師 #電子工程師 #軟件工程師

需要無(wú)刷電控硬件工程師

嵌入式軟件工程師如何提升自己?

嵌入式軟件工程師和硬件工程師的區(qū)別?

電子工程師必備知識(shí):PCB布局中的干擾噪音問(wèn)題解決方案

工程師需要掌握的實(shí)用PCB布線技巧

工程師需要掌握的實(shí)用PCB布線技巧

評(píng)論