高速電路設(shè)計(jì),工程師需要掌握哪些知識(shí)技能呢?下面以具體的七個(gè)技術(shù)面,為大家詳細(xì)敘述一一解答:

1. 電源布局布線(xiàn)相關(guān)

2. 走線(xiàn)的彎曲方式

3. 信號(hào)的接近度

4. 走線(xiàn)stubs

5. 阻抗不連續(xù)

6. 等分信號(hào)

7. 等長(zhǎng)

1. 電源布局布線(xiàn)相關(guān)

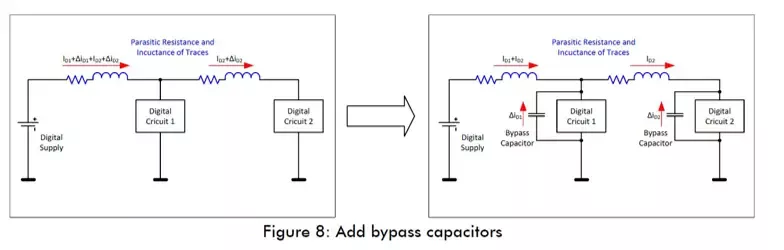

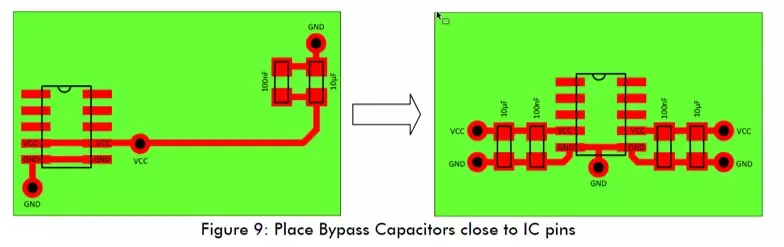

數(shù)字電路很多時(shí)候需要的電流是不連續(xù)的,所以對(duì)一些高速器件就會(huì)產(chǎn)生浪涌電流。如果電源走線(xiàn)很長(zhǎng),則由于浪涌電流的存在進(jìn)而會(huì)導(dǎo)致高頻噪聲,而此高頻噪聲會(huì)引入到其他信號(hào)中去。而在高速電路中必然會(huì)存在寄生電感和寄生電阻以及寄生電容,因此該高頻噪聲最終會(huì)耦合到其他電路當(dāng)中,而由于寄生電感的存在也會(huì)導(dǎo)致走線(xiàn)可以承受的最大浪涌電流的能力下降,進(jìn)而導(dǎo)致有部分壓降,有可能會(huì)使電路失能。所以在數(shù)字器件前面加上旁路電容就顯得尤為重要。電容越大,其在傳輸能量上是受限于傳輸速率的,所以一般會(huì)結(jié)合一個(gè)大電容和一個(gè)小電容一起,來(lái)滿(mǎn)足全頻率范圍內(nèi)。

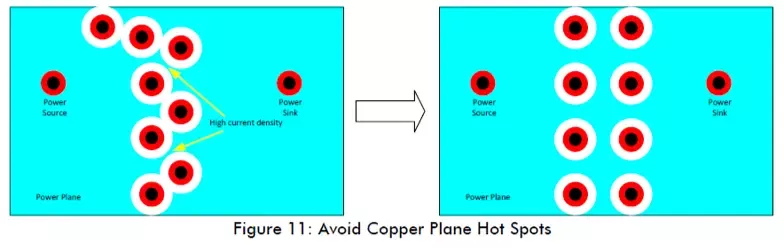

避免熱點(diǎn)產(chǎn)生:信號(hào)過(guò)孔會(huì)在電源層和底層產(chǎn)生voids。所以不合理的放置過(guò)孔很有可能會(huì)使電源或者地平面某些區(qū)域的電流密度增加。而這些電流密度增加的地方我們稱(chēng)之為熱點(diǎn)。

所以,我們?cè)谠O(shè)置過(guò)孔的時(shí)候要極力避免這種情況發(fā)生,以免平面被割裂,最終導(dǎo)致EMC的問(wèn)題產(chǎn)生。通常最好的避免熱點(diǎn)的辦法就是網(wǎng)狀式的放置過(guò)孔,如此電流密度均勻,同時(shí)平面不會(huì)隔離,回流路徑就不會(huì)過(guò)長(zhǎng),也就不會(huì)產(chǎn)生EMC的問(wèn)題。

2. 走線(xiàn)的彎曲方式

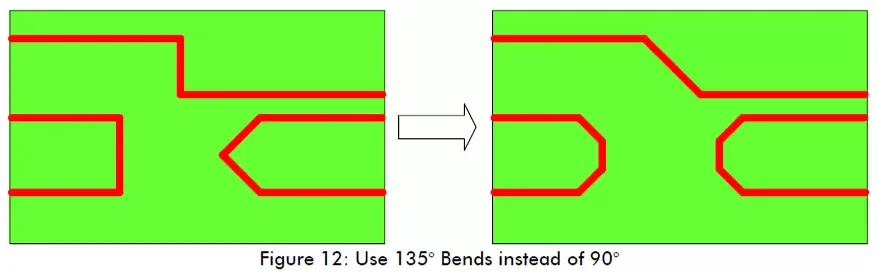

在布高速信號(hào)線(xiàn)時(shí),信號(hào)線(xiàn)應(yīng)盡量避免彎曲。如果不得不彎曲走線(xiàn),則不要銳角或者直角走線(xiàn),而是應(yīng)該用鈍角走線(xiàn)。

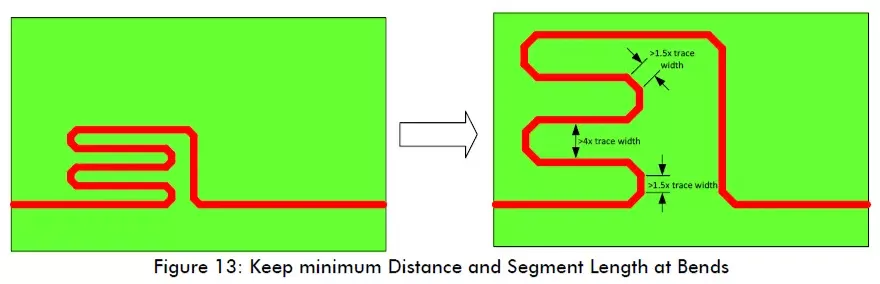

在布高速信號(hào)線(xiàn)時(shí),我們經(jīng)常通過(guò)走蛇形線(xiàn)來(lái)實(shí)現(xiàn)等長(zhǎng),同樣的蛇形線(xiàn)也其實(shí)一種走線(xiàn)的彎曲。線(xiàn)寬,間距,以及彎曲方式都應(yīng)該做合理的選擇,間距應(yīng)滿(mǎn)足4W/1.5W規(guī)則的。

3. 信號(hào)的接近度

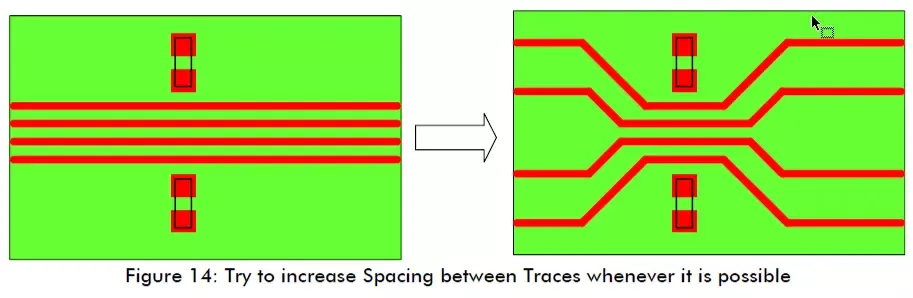

高速信號(hào)線(xiàn)之間如果距離太近,很容易產(chǎn)生串?dāng)_。有些時(shí)候,因?yàn)椴季帧蹇虺叽绲仍颍瑢?dǎo)致我們?cè)诓几咚傩盘?hào)線(xiàn)之間的距離超過(guò)了我們的最低要求距離,那我們只能在靠近其瓶頸的地方盡量加大高速信號(hào)線(xiàn)之間的距離。其實(shí)如果空間足夠容許,則盡量加大兩高速信號(hào)線(xiàn)之間的距離。

4. 走線(xiàn)stubs

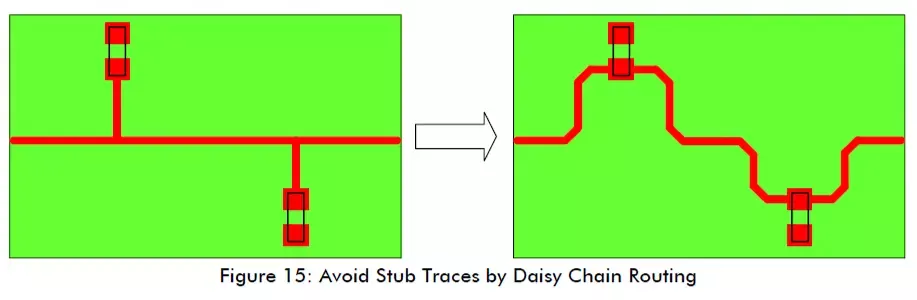

長(zhǎng)的stub線(xiàn)就相當(dāng)于一個(gè)天線(xiàn),處理不當(dāng)會(huì)產(chǎn)生很?chē)?yán)重的EMC的問(wèn)題。同時(shí)stub線(xiàn)也會(huì)造成反射,降低信號(hào)的完整度。通常在高速信號(hào)線(xiàn)上面添加上拉或者下拉電阻的時(shí)候,會(huì)最容易產(chǎn)生stub線(xiàn),而一般處理stub線(xiàn)的將走線(xiàn)可以菊花走線(xiàn)。根據(jù)經(jīng)驗(yàn)可知,如果stub線(xiàn)的長(zhǎng)度大于1/10波長(zhǎng)就可以當(dāng)做一個(gè)天線(xiàn)了,此時(shí)就會(huì)成為一個(gè)問(wèn)題。

5. 阻抗不連續(xù)

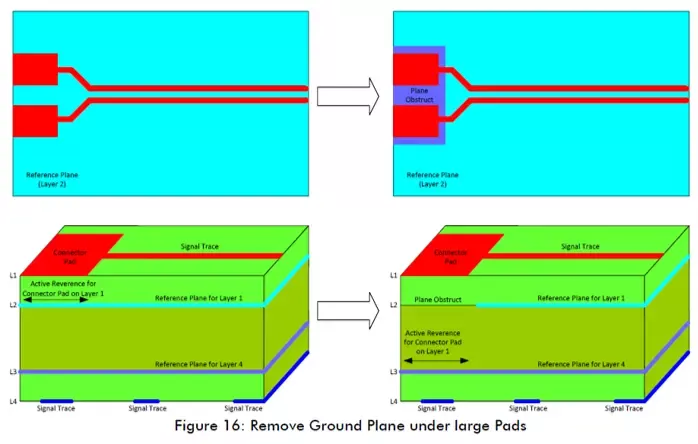

走線(xiàn)的阻抗值一般取決于其線(xiàn)寬以及該走線(xiàn)與參考平面之間的距離。走線(xiàn)越寬,其阻抗越小。而在一些接口端子也器件的焊盤(pán),其原理同樣適用。當(dāng)一個(gè)接口端子的焊盤(pán)和一根高速信號(hào)線(xiàn)連接時(shí),如果此時(shí)焊盤(pán)特別大,而高速信號(hào)線(xiàn)特別窄,大焊盤(pán)則阻抗小,而窄的走線(xiàn)必然是大阻抗,在這種情況下就會(huì)出現(xiàn)阻抗不連續(xù),阻抗不連續(xù)就會(huì)產(chǎn)生信號(hào)反射。所以一般為了解決這個(gè)問(wèn)題,都是在接口端子或者器件的大焊盤(pán)下面放置一個(gè)禁布銅皮,同時(shí)在另外一層放置該焊盤(pán)的參考平面,進(jìn)而加大阻抗,使阻抗連續(xù)。

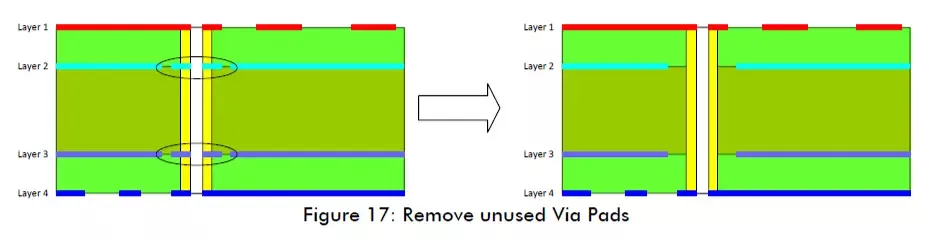

過(guò)孔是另外一種會(huì)產(chǎn)生阻抗不連續(xù)的源頭。為了最小化這種效應(yīng),在內(nèi)層和過(guò)孔連接的不需要的銅皮應(yīng)該去除。而這樣的操作其實(shí)可以在設(shè)計(jì)的時(shí)候通過(guò)CAD工具來(lái)消除或者聯(lián)系溝通PCB加工產(chǎn)假來(lái)消除不需要的銅皮,保證阻抗的連續(xù)性。

6. 差分信號(hào)

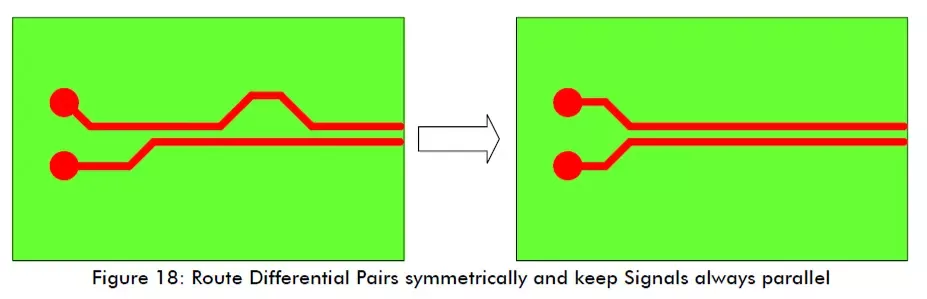

高速差分信號(hào)線(xiàn)我們必須保證等寬、等間距來(lái)實(shí)現(xiàn)特定的差分阻抗值。所以在布差分信號(hào)線(xiàn)的時(shí)候盡量保證對(duì)稱(chēng)。

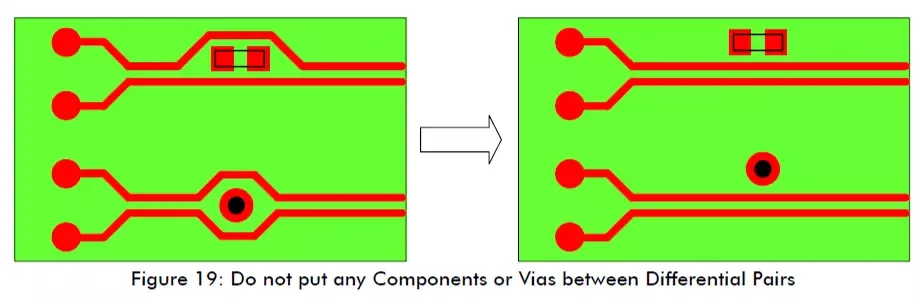

在差分線(xiàn)對(duì)內(nèi)禁止布置過(guò)孔或者元器件,如果在差分線(xiàn)對(duì)內(nèi)放置了過(guò)孔或者器件會(huì)產(chǎn)生EMC問(wèn)題同時(shí)也會(huì)導(dǎo)致阻抗不連續(xù)。

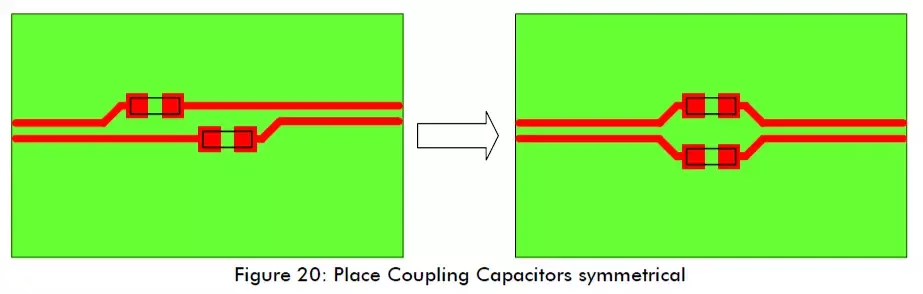

有時(shí)候,一些高速差分信號(hào)線(xiàn)需要串接耦合電容。該耦合電容同樣需要對(duì)稱(chēng)布置,同時(shí)該耦合電容的封裝不能過(guò)大,推薦使用0402,0603也可以接受,0805以上的電容或者并排電容最好不要使用。

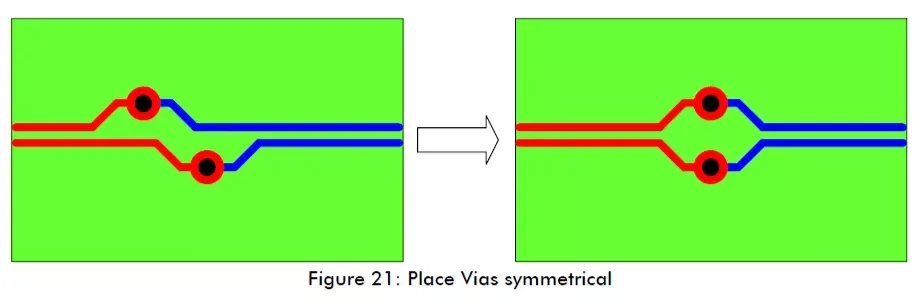

通常,過(guò)孔會(huì)產(chǎn)生巨大的阻抗不連續(xù),所以對(duì)于高速差分信號(hào)線(xiàn)對(duì)則盡量減少過(guò)孔,如果要使用過(guò)孔則對(duì)稱(chēng)布置。

7. 等長(zhǎng)

在一些高速信號(hào)接口,一般如總線(xiàn)等需要考慮其個(gè)信號(hào)線(xiàn)之間的到達(dá)時(shí)間以及時(shí)滯誤差。例如,在一組高速平行總線(xiàn)中的所以數(shù)據(jù)信號(hào)線(xiàn)其到達(dá)時(shí)間,必須保證在一定的時(shí)滯誤差以?xún)?nèi),從來(lái)來(lái)保證其建立時(shí)間和保持時(shí)間的一致性。為了滿(mǎn)足這一需求,我們必須要考慮等長(zhǎng)。

而高速差分信號(hào)線(xiàn)對(duì)兩信號(hào)線(xiàn)必須保證嚴(yán)格的時(shí)滯,否則很有可能通訊失敗。故為了滿(mǎn)足這一要求,可以通過(guò)蛇形線(xiàn)來(lái)實(shí)現(xiàn)等長(zhǎng),進(jìn)而滿(mǎn)足時(shí)滯要求。

蛇形線(xiàn)一般應(yīng)該布置在失長(zhǎng)的源頭處,而不是遠(yuǎn)端。在源頭處才能保證差分線(xiàn)的正負(fù)端的信號(hào)在大部分時(shí)間內(nèi)都是同步傳輸?shù)摹?/p>

走線(xiàn)彎曲處是產(chǎn)生失長(zhǎng)的源頭之一。對(duì)于走線(xiàn)彎曲處,其實(shí)現(xiàn)等長(zhǎng)的應(yīng)靠近彎曲處(<=15mm)

如果有兩個(gè)走線(xiàn)彎曲,且兩者之間的距離<15mm,故此時(shí)兩者的失長(zhǎng)會(huì)互相補(bǔ)償,故此時(shí)不用再做等長(zhǎng)處理。

對(duì)于不同部分的高速差分信號(hào)線(xiàn),應(yīng)分別獨(dú)立等長(zhǎng)。過(guò)孔,串接耦合電容以及接口端子都會(huì)是高速差分信號(hào)線(xiàn)分成兩部分,所以這個(gè)時(shí)候要特別注意。一定要分別等長(zhǎng)。因?yàn)楹芏?a target="_blank">EDA軟件在DRC的時(shí)候都只關(guān)注整個(gè)走線(xiàn)是否失長(zhǎng)。

對(duì)于如LVDS顯示器件等接口,會(huì)同時(shí)存在數(shù)對(duì)差分對(duì),且差分對(duì)之間的時(shí)序要求一般都會(huì)特別嚴(yán)格,時(shí)滯要求特別小,所以,對(duì)于此類(lèi)差分信號(hào)對(duì)我們要求一般在同一平面內(nèi)進(jìn)行補(bǔ)償。因?yàn)椴煌瑢拥男盘?hào)傳輸速度是不同的。

有些EDA軟件在計(jì)算走線(xiàn)長(zhǎng)度時(shí),會(huì)將焊盤(pán)內(nèi)部的走線(xiàn)也會(huì)計(jì)算在長(zhǎng)度之內(nèi),如果此時(shí)進(jìn)行長(zhǎng)度補(bǔ)償,最終實(shí)際結(jié)果會(huì)失長(zhǎng)。所以此時(shí)要特別注意,在使用一些EDA的軟件的時(shí)候。

在任何時(shí)候,如果可以就一定選擇對(duì)稱(chēng)出線(xiàn)進(jìn)而避免需要最終為了等長(zhǎng)而進(jìn)行蛇形走線(xiàn)。

如果空間容許,盡量在短的差分線(xiàn)源頭處加一個(gè)小的回環(huán)來(lái)實(shí)現(xiàn)補(bǔ)償,而不是通過(guò)蛇形線(xiàn)來(lái)補(bǔ)償。

審核編輯:何安

-

高速電路設(shè)計(jì)

+關(guān)注

關(guān)注

2文章

20瀏覽量

8181

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

年薪30萬(wàn)的嵌入式工程師,究竟需要掌握哪些技能?

不同時(shí)期的硬件工程師,最怕發(fā)生的事 #電子工程師 #硬件工程師 #內(nèi)容過(guò)于真實(shí) #YXC晶振 #揚(yáng)興科技

為什么嵌入式驅(qū)動(dòng)開(kāi)發(fā)工程師可以拿高薪?

笑死,掌握一眼識(shí)別資深硬件工程師的訣竅了!# #電路知識(shí) #電工 #硬核拆解

硬件工程師需要掌握的硬件基礎(chǔ)知識(shí)

芯片封裝工藝集成工程師的必修課程指南

Keysight助力提升工程師的測(cè)試測(cè)量知識(shí)水平

硬件工程師VS軟件工程師|硬件工程師看到這都淚目了!#硬件設(shè)計(jì) #硬件工程師 #電子工程師 #軟件工程師

需要無(wú)刷電控硬件工程師

嵌入式軟件工程師如何提升自己?

嵌入式軟件工程師和硬件工程師的區(qū)別?

工程師需要掌握哪些知識(shí)技能呢

工程師需要掌握哪些知識(shí)技能呢

評(píng)論