在進入關于編碼器和解碼器的現實之前,讓我們對復用進行簡要的思考。通常我們會在需要將一些輸入信號一次一個地加載到一個單獨負載的應用程序中。選擇輸入信號中的一個輸入信號的過程稱為多路復用。這種操作的逆轉,即從一個公共信號源滋養少量負載的方式稱為解復用。類似地,在數字領域中,為了信息傳輸的簡單性,信息被定期地加擾或者在代碼內設置,并且之后,傳輸該安全代碼。在收集器處,編碼信息被解碼或從代碼中累積,并被處理為同樣被顯示或給予負載。

編碼器和解碼器完成了信息加密和解密信息的分配。那么我們現在怎么理解真正的編碼器和解碼器。

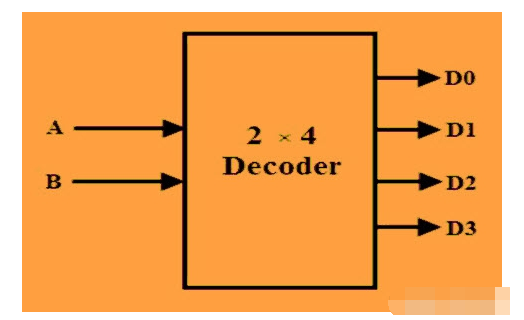

什么是解碼器?

解碼器是一個多輸入多輸出邏輯電路,它將代碼i / ps變為編碼的o / ps,其中輸入和輸出都不相似,例如n-2n,以及二進制編碼的十進制解碼器。解碼在數據復用,存儲器地址解碼和7段顯示等應用中至關重要。解碼器電路最好的例子是一個與門,因為當所有的輸入都是“高電平”時,這個門的輸出是“高電平”,這就是所謂的“高電平有效輸出”。作為與門的替代,與非門被連接,只有當其所有輸入都為“高”時,輸出將為“低”(0)。這樣的o / p被稱為“低電平有效輸出”。

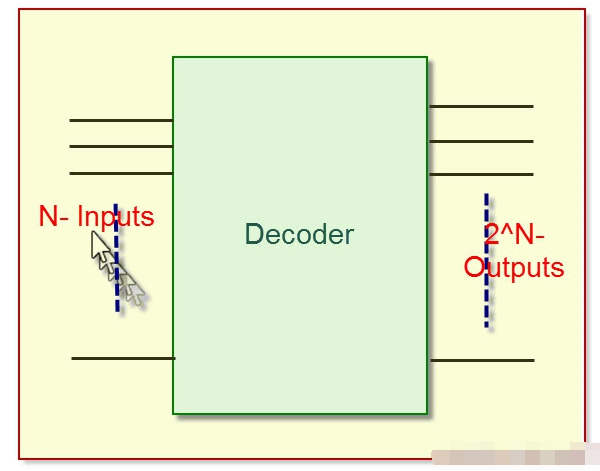

一個稍微困難的解碼器將是n到2n型二進制解碼器。這些類型的解碼器是組合電路,可將二進制信息從n編碼輸入修改為大部分2n獨占輸出。如果隨后比特編碼的數據具有空閑比特組合,解碼器可能具有少于2n個輸出。其他示例包括2至4,3 至8行解碼器或4至16解碼器。

并行二進制數字是解碼器的輸入,用于注意輸入處出現的特定二進制數。輸出顯示在解碼器輸入處存在或不存在精確數字。

2至4線解碼器電路的設計

與多路復用器電路類似,解碼器不限于特定地址線,因此可以具有多于兩個輸出(具有兩個,三個或四個地址線)。解碼器電路可以解碼2,3或4位二進制數,或者可以解碼多達4,8或16個時分復用信號。

作為一個解碼器,該電路采用一個n位二進制數并在其中一條輸出線上產生一個輸出。因此通常通過尋址i / p線的數量和數據o / p線的數量來描述。典型的解碼器IC可能包括兩個2-4線路電路,一個3-8線路電路或一個4-16線路解碼器電路。對該電路的二進制字符的一個排除是4-10行解碼器,其被提議將二進制編碼的十進制(BCD)輸入改變為0-9范圍的輸出。

如果您將此電路用作解碼器,則可能需要在o / ps處插入數據鎖存器,以便在傳輸其他信號時保持每個信號。但是,當你使用這個電路作為解碼器時,這與你并不相關,那么你只需要一個有效的o / p來等于輸入碼。

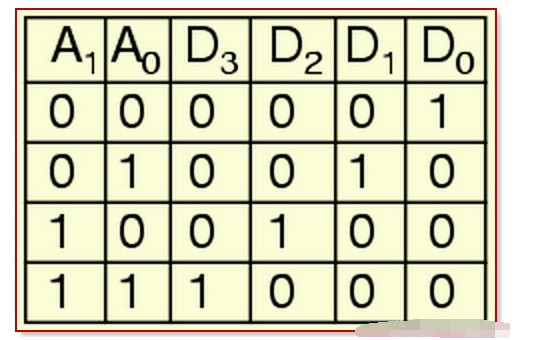

2至4行解碼器真值表

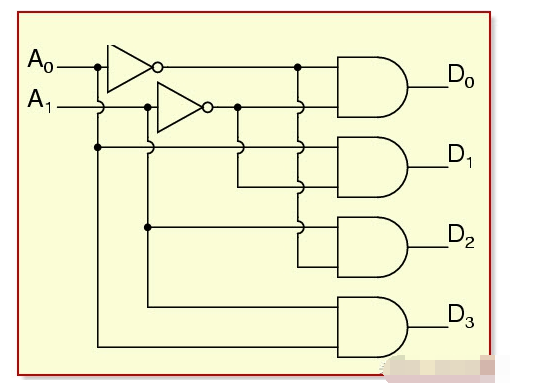

在這種類型的解碼器中,解碼器具有兩個輸入,即A0,A1以及由D0,D1,D2和D3表示的四個輸出。正如您在以下真值表中看到的 - 對于每個輸入組合,打開一個o / p線。

在上面的例子中,你可以觀察到每個解碼器的o / p確實是一個最小項,由一個確定的輸入組合產生,即:

D0 = A1 A0,(minterm m0)對應輸入端00 D1 = A1 A0,(minterm m1)對應于輸入端01 D2 = A1 A0,(minterm m2)對應輸入端10 D3 = A1 A0,(minterm m3 )它對應于輸入11如圖所示,該電路采用與門實現。在這個電路中,D0的邏輯方程是A1 / A0,依此類推。因此,解碼器的每個輸出將被生成為輸入組合。

責任編輯人:CC

-

解碼器

+關注

關注

9文章

1148瀏覽量

40936

發布評論請先 登錄

相關推薦

74AHC139-Q100/74AHCT139-Q100雙通道2至4線解碼器/解復用器手冊

74AHC139/74AHCT139雙通道2至4線解碼器/解復用器手冊

一文解析2至4線解碼器的設計

一文解析2至4線解碼器的設計

評論