原創(chuàng)聲明:

本原創(chuàng)教程由芯驛電子科技(上海)有限公司(ALINX)創(chuàng)作,版權(quán)歸本公司所有,如需轉(zhuǎn)載,需授權(quán)并注明出處(http://www.alinx.com)。

適用于板卡型號(hào):

PGL22G/PGL12G

1. 文檔簡介

通過按鍵檢測實(shí)驗(yàn),檢測開發(fā)板的按鍵功能是否正常,了解硬件描述語言和FPGA的具體關(guān)系,學(xué)習(xí)PDS View RTL Schematic的使用。

2. 實(shí)驗(yàn)環(huán)境

-

Windows 10 64位

-

View RTL Schematic(Pango Design Suite 2020.3)

3. 實(shí)驗(yàn)原理

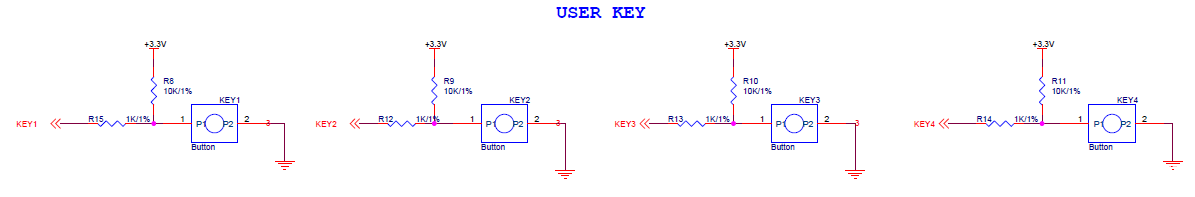

3.1 按鍵硬件電路

開發(fā)板按鍵部分電路

開發(fā)板按鍵部分電路

從圖中可以看到,電路的按鍵松開時(shí)是高電平,按下時(shí)是低電平。

3.2 程序設(shè)計(jì)

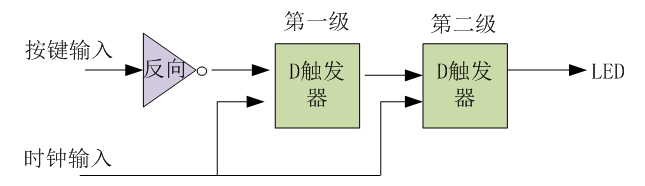

這個(gè)程序沒有設(shè)計(jì)的很復(fù)雜,通過簡單的硬件描述語言看透硬件描述語言和FPGA硬件的聯(lián)系。首先我們將按鍵輸入經(jīng)過一個(gè)非門后再經(jīng)過2組D觸發(fā)器。經(jīng)過D觸發(fā)器的信號(hào),會(huì)在D觸發(fā)器時(shí)鐘輸入的上升沿鎖存然后再送到輸出。

在進(jìn)行硬件描述語言編碼之前,我們已經(jīng)把硬件構(gòu)建完成,這是一個(gè)正常的開發(fā)流程。有了硬件設(shè)計(jì)思路無論是通過畫圖還是通過Verilog HDL、VHDL都能完成設(shè)計(jì),根據(jù)設(shè)計(jì)的復(fù)雜程序和對(duì)某種語言的熟悉程序來選擇工具。

4. 工程分析

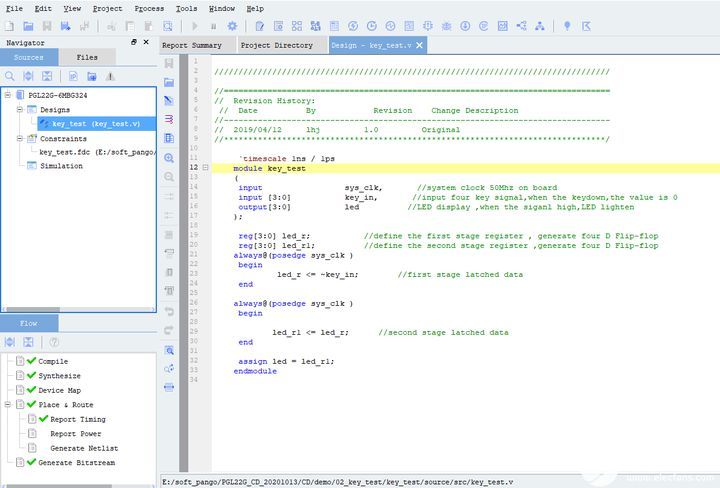

1)首先建立按鍵的測試工程,添加verilog測試代碼,完成編譯分配管腳等流程。

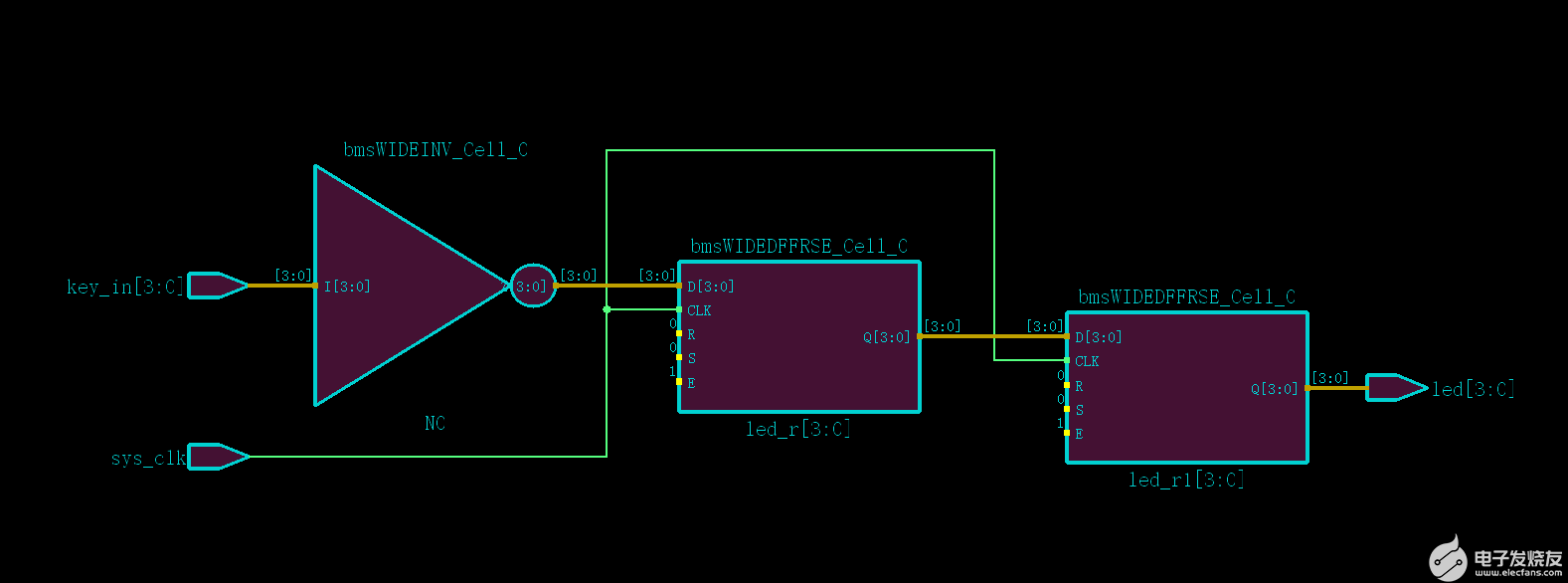

2)使用View RTL Schematic工具查看設(shè)計(jì)

3)分析RTL圖,可以看出第一級(jí)D觸發(fā)器經(jīng)過取反后輸入,第二級(jí)直接輸入,和預(yù)期設(shè)計(jì)一致。

5. 實(shí)驗(yàn)現(xiàn)象

程序下載到開發(fā)板以后, "LED1"、"LED2"、"LED3"、"LED4"都處于亮狀態(tài),按鍵“KEY1”按下“LED1” 滅,按鍵“KEY2”按下“LED2” 滅,按鍵“KEY3”按下“LED3” 滅, 按鍵“KEY4”按下“LED4”滅。

6. 附錄

key_test.v(verilog代碼)

`timescale1ns/1psmodulekey_test(inputsys_clk,//systemclock50Mhzonboardinputrst_n,//reset,lowactiveinput[3:0]key_in,//inputfourkeysignal,whenthekeydown,thevalueis0output[3:0]led//LEDdisplay,whenthesiganlhigh,LEDlighten);reg[3:0]led_r;//definethefirststageregister,generatefourDFlip-flop reg[3:0]led_r1;//definethesecondstageregister,generatefourDFlip-flopalways@(posedgesys_clkornegedgerst_n)beginif(~rst_n) led_r<=4'b0000;else ????????????led_r?<=~key_in;//first?stage?latched?dataendalways@(posedge?sys_clk?ornegedge?rst_n)beginif(~rst_n) ????????????led_r1?<=4'b0000;else ????????????led_r1?<=?led_r;//second?stage?latched?dataendassign?led?=?led_r1;endmodule

-

FPGA

+關(guān)注

關(guān)注

1630文章

21798瀏覽量

606057 -

RTL

+關(guān)注

關(guān)注

1文章

385瀏覽量

59954 -

按鍵

+關(guān)注

關(guān)注

4文章

223瀏覽量

57663 -

硬件描述語言

+關(guān)注

關(guān)注

0文章

10瀏覽量

12065 -

紫光同創(chuàng)

+關(guān)注

關(guān)注

5文章

88瀏覽量

27563

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

【紫光同創(chuàng)國產(chǎn)FPGA教程】【PGC1/2KG第三章】鍵控彩燈實(shí)驗(yàn)例程

自動(dòng)控制原理第三章習(xí)題答案

STM8S BLDC 電機(jī) 第三章 EEPROM 實(shí)驗(yàn)例程

計(jì)算機(jī)網(wǎng)絡(luò)第三章數(shù)據(jù)鏈路層資源下載

【正點(diǎn)原子FPGA連載】第三章 硬件資源詳解 -摘自【正點(diǎn)原子】新起點(diǎn)之FPGA開發(fā)指南_V2.1

【紫光同創(chuàng)國產(chǎn)FPGA教程】【第三章】按鍵檢測實(shí)驗(yàn)

【紫光同創(chuàng)國產(chǎn)FPGA教程】【第三章】按鍵檢測實(shí)驗(yàn)

評(píng)論