今天帶大家來設計一個自定義的IP核,我們從最基本的做起,包括datasheet 的理解,設計的整體框架,AD轉換代碼的編寫,仿真,Avalon-MM總線接口的編寫,硬件系統還是基于上次的硬件系統,不過我們不再用altera給我們提供的IP核了,我們要自己做一個,有時候我們找不到他們提供的IP核,或者有些IP核是收費的,這個時候我們就可以自己來編寫自己的IP,雖然沒有官方的那么標準,但是用來做一些實驗還是沒什么問題的。

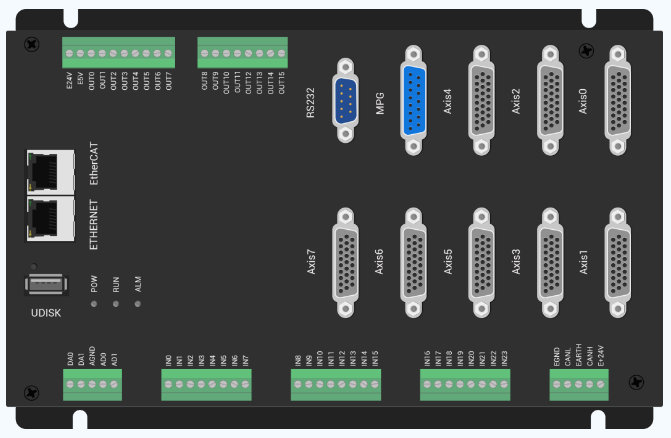

這次實驗我用的是原來我那塊板子,因為那塊板子上有AD轉換芯片,而我們上次搭建的硬件系統是基于cyclone IV的硬件系統,但是這塊開發板上沒有AD芯片,我們就不做軟件下載的實驗了,其實只要在我們編寫AD轉換HDL代碼的時候測試成功,那么我們軟件調試部分就應該沒什么問題了,有條件的同學可以自己做這一部分。

一、有理可依

所有編寫的代碼必須都得有理可依,要不然直接看代碼那得有多痛苦啊,第一部分先來帶大家熟悉一下datasheet上的東西

我們要操作的AD轉換芯片TLC549的頂層視圖

可以看到這個芯片應該不太難操作,左邊是模擬信號輸入端,因為是模數轉換,這邊我們就暫時可以不管,看右邊有時鐘信號,數字信號輸出端和片選端,那么我們需要控制的,無非就是時鐘信號和片選信號了

還有什么器件描述什么的大家可以自己取去看,我們主要去看時序圖

大體上來看一下,,首先是ADC的工作時鐘,它在片選信號為低電平的時候有效,連續8個周期用來將轉換后的數字信號送到數據總線上,8個時鐘周期過后就是轉換周期,用來對模擬信號進行轉換,在這期間,片選信號要拉高,對于片選信號,開始的時候有一個從高電平到低電平的跳變,然后等待一個建立時間TSU,建立時間結束后ADC工作時鐘開始工作,8個時鐘周期后,片選拉高開始模數轉換,之后片選拉低,將轉換后的數據送出去。

細節部分,可以看到當片選拉低后,我們可以定義一個使能信號en來開啟工作時鐘,從片選拉低到工作時鐘有效需要一個建立時間1.4us,這個數據在下面的表格中可以查到,之后是8個數據鎖存周期,每一個時鐘的高低電平延時不能小于404ns,具體也是表格中找,然后是轉換周期,時間是17us,至于轉換期間的工作時鐘是什么我們可以不必關心。

再來看一下它的注釋內容,大體意思是說轉換周期需要一個17us的延時,注釋B大體意思是說,當片選拉低之后,數據的第8位就自動的放到了數據總線上,剩下的7位數據在第7個時鐘下降沿到來的時候就已經鎖存了。

二、編程思路

這段時間跟著他們在上課,聽李老師講課的時候,李老師不會將大量的時間放到代碼的編寫上,而是有時候花一整節課的時間來幫助學生來構建編程的思路,包括系統架構,狀態轉移圖等,有了這些都東西作為鋪墊,我們的代碼編寫就可以手到擒來,起到事半功倍的效果,如果我們不做好事先的準備設計工作,沒有一個系統的架構在我們腦海里,上來就去寫代碼,就會發現越寫問題越多,思路不通,處理不當等問題,所以小墨同學回來之后也用word做了這么個狀態轉移圖,這個實驗不是很難,狀態機也沒那么復雜,就是希望起到一個拋磚引玉的過程,通過一個小小的實例,告訴大家以后在拿到一個問題后改怎么下手。雖然畫的不怎么樣~還是可以看得哈~

理一下編程思路吧,從datasheet里面我們知道。我們要做好這幾個延時,即準備轉換的延時1.4us,17us的轉換延時,和404ns的ADC工作時鐘高低電平延時等。狀態機部分采用兩段式狀態機。將組合邏輯與時序邏輯分開,采用獨熱編碼。按照狀態轉移圖構思好狀態機的編程思路。數據處理部分,為了保證數據的穩定性,可以采用邊沿脈沖檢測法檢測ADC工作時鐘的上升沿,在每一個上升沿將轉化后的數據一位一位鎖存,由于數據是串行輸入,還要用到串并轉換的思想,這些編程方法前面都已經介紹過,就不一一講解了。

代碼風格部分,個人感覺這一套代碼比起以前有了一些進步,至少看起來思路清晰,注釋合理,數據處理恰當,語法直白,沒有用到一些很別扭的語法等。具體還需要廣大讀者自己去體會,也希望你們能夠喜歡~

代碼部分就不一一講解了,源代碼會附在文章后面,大家可以自行消化

三、仿真與驗證

上面是前仿真的過程,從波形來看和我們的設計吻合,用標尺量一下,延時參數也和我們設計的一致

按理說我們下一步需要進行時序約束部分,但是我們的這個設計是us級的,即使不做時序約束也是可以的,但是畢竟我設計的是一個IP核,為了穩定起見還是做一下時序約束比較好。說實話,時序約束部分,個人感覺是一門高大上的學問,變化多端,有些都是經驗值,你問一個工程師為什么是這樣約束,有時候可能他也答不上來。之前也接觸過靜態時序分析的知識,但是一直不敢寫,感覺還是學的不怎么樣吧,想回去以后學內存這方面的時候再去好好研究一下它~

下面是后仿真的波形圖

可以看到,波形跟我們的設計吻合,也沒有出現什么不合理的設計什么的,可以下板驗證了

可以看到,當我們扭動滑動變阻器的時候,相應的模擬量被轉化成數字量并在數碼管上顯示了

四、Avalon-MM總線接口設計

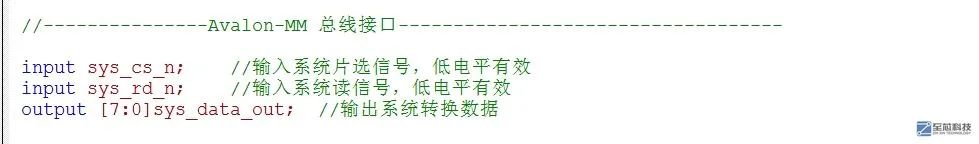

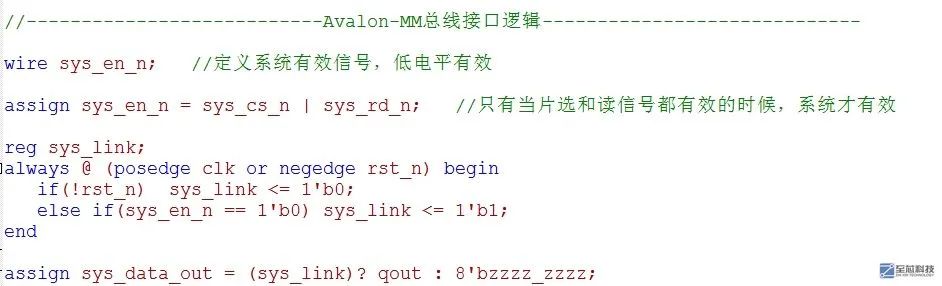

我們知道,我們設計的這個IP核是要掛到Avalon-MM總線上的,作為一個從機,總線需要通過片選信號來訪問總線上掛的這些IP,因此,我們也需要給我們的IP設計一個和總線通信的接口

我們設計AD轉換的IP核的片選信號低電平有效,當片選信號有效的時候,如果再來一個讀信號,那么,數據就會被總線讀走,送至CPU

五、自定義IP

好了,下面我們就可以來定義我們自己的IP了

先將我們剛才設計好的AD轉換的.V文件復制到我們硬件系統的目錄中,并養成一個好的習慣,新建一個文件夾,并命名為IP,以后我們設計的IP都可以放到里面

打開我們之前硬件系統的sopc builder,雙擊左上角的NEW component ,在HDL file一欄中添加我們的adc.v文件,

在signal一欄中,根據端口的類型配置端口,時鐘復位信號不用說,其中我們的與總線接口部分的端口屬于總線的從機端口,我們需要把它定義為avalon_slave_0端口類型,信號類型設置為低電平片選,低電平讀就好,其他端口設置為conduit類型,信號類型設置為export,因為我們是用來輸出到外部器件的端口

在接口一欄中,我們可以設置一些相關參數,一般為默認就好,為了我們數據的穩定性,我們可以把讀延時周期設置為4個,保證它有足夠的時間去處理數據

然后點擊finish,雙擊我們生成的IP核將它添加到系統工程中即可,然后重新生成硬件系統

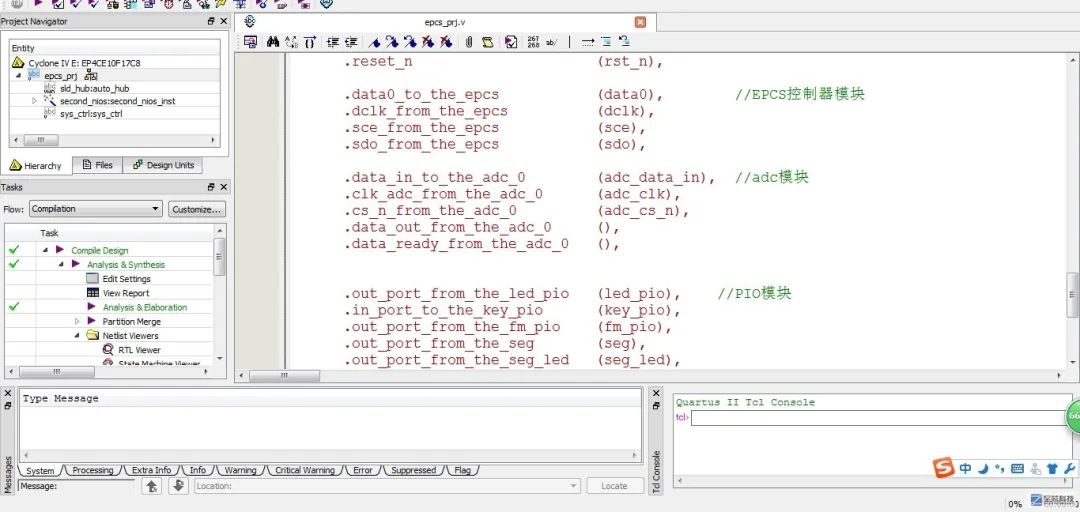

六、硬件系統生成

將生成的新的硬件系統的例化接口聲明好,這樣在我們的設計頂層又多了這樣一個模塊,按照慣例分析綜合,時序約束,分配管腳,這樣我們的硬件系統就設計好了

七、軟件部分

因為我的硬件系統上沒有AD芯片,這里就只簡單說一下軟件代碼,不做下板調試了

軟件部分只講一下主函數部分,看下圖

代碼很簡單,就是每隔一段時間將采集到的值在窗口打印,不過有個問題需要解釋一下,有人會問,我們在自定義IP的時候不是定義了片選端和讀信號么,為什么我們沒有對它進行操作就可以讀數據了呢?

其實我們是不需要對我們的外設進行片選或者讀寫使能的,因為我們的avalon-MM總線一次只能訪問一個從機,我們給出了我們AD轉換的IP的地址,就默認片選了這個模塊了,又因為我們調用了IO操作的讀函數,在定義信號的時候我們定義的是低電平,這樣其實就是總線默認幫我們選好了,我們只需要給它一個地址,那么數據就會自動的傳到總線上去。

責任編輯:lq6

-

cpu

+關注

關注

68文章

10905瀏覽量

213030 -

IP核

+關注

關注

4文章

331瀏覽量

49643 -

AD轉換芯片

+關注

關注

3文章

68瀏覽量

18166 -

Avalon總線

+關注

關注

0文章

11瀏覽量

10160

原文標題:零基礎學FPGA SOPC進階,自定義AD轉換IP核設計全流程

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

think-cell:自定義think-cell(四)

think-cell;自定義think-cell(一)

如何將自定義邏輯從FPGA/CPLD遷移到C2000?微控制器

TSMaster 自定義 LIN 調度表編程指導

HarmonyOS開發案例:【UIAbility和自定義組件生命周期】

基于FPGA的SOPC自定義IP核設計全流程

基于FPGA的SOPC自定義IP核設計全流程

評論